Etude d’un oscillateur à contrôle numérique, partie 1...

-

Upload

vuongtuong -

Category

Documents

-

view

252 -

download

1

Transcript of Etude d’un oscillateur à contrôle numérique, partie 1...

Denis Rabasté 1/24 IUFM Aix-Marseille

Etude d’un oscillateur à contrôle numérique, partie 1 : introduction aux « méga-fonctions » de Quartus II

L’étude d’un oscillateur à contrôle numérique (OCN ou NCO en anglais), encore appelé oscillateur modulateur à contrôle numérique (OMCN) va nous permettre d’approcher les « méga-fonctions » que propose le logiciel de synthèse de FPGA et CPLD, Quartus II. Celles-ci permettent une implantation rapide et efficace de composants numériques complexes tel que mémoires, additionneurs, registres multiplieurs numériques etc…. Comme son nom l’indique, l’oscillateur numérique contrôlé permet de générer numériquement un signal, dont on va pouvoir ajuster les paramètres, en particulier la fréquence, mais aussi la phase et l’amplitude, de manière numérique également. Deux solutions sont classiquement utilisées pour la synthèse de signaux : - la synthèse indirecte à boucle à verrouillage de phase semi-numérique ; - la synthèse numérique directe (SND ou DDS pour Direct Digital Synthesis), que nous allons

étudier maintenant. La première solution présente l’avantage de pouvoir directement travailler avec une fréquence de sortie élevée (l’oscillateur étant analogique), tandis que la seconde entièrement numérique (hormis le CNA en fin de chaîne) présente tous les avantages liés à cette technologie. L’inconvénient inhérent à une fréquence de sortie limitée peut être pallié par un décalage fréquentiel du signal de sortie du CNA du NCO. Les applications de ce type de fonctions sont nombreuses, tant dans le domaine des télécommunications, où nous verrons quelques exemples de modulateur entièrement numériques, que dans l’instrumentation. Au cours de cette séance, nous nous intéresseront plus particulièrement au principe de base du NCO, alors que dans la suivante (partie 2) nous synthétiserons le NCO par une mégafonction fournie avec Quartus.

1 Principe de base

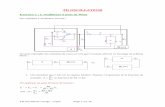

L’idée de départ de la synthèse numérique de fréquence est l’incrémentation à fréquence fixe par une horloge à quartz, d’un compteur dont la sortie va lire une mémoire morte. Si dans celle-ci, à chaque adresse associée à l’incrément de temps, se trouve l’amplitude du signal souhaité, après conversion numérique analogique, on obtient le signal recherché. Généralement celui-ci est sinusoïdal, mais ce n’est pas une obligation (en particulier en instrumentation). Dans le cas sinusoïdal, les données de la mémoire peuvent être vues comme l’amplitude associée à chaque phase instantanée du signal, et les adresses comme la phase du signal. Le schéma ci-après représente un compteur 8 bits (mégafonction « lmp_counter ») incrémentant une mémoire rom (mégafonction lpm_rom »). Le bus de sortie q[0..7] n’a d’intérêt ici que pour pouvoir représenter facilement le bus d’adresse de la ROM lors des simulations.

VCCH INPUT

sortie[0..7]OUTPUT

up counterclockq[7..0]

lpm_counter0

inst2address[7..0]clock

q[7..0]

lpm_rom0

inst

q[0..7]OUTPUT

étude d’un OCN, introduction aux méga-fonctions de Quartus

Denis Rabasté 2/24 IUFM Aix-Marseille

Cette structure ne permet pour l’instant pas d’ajustage de fréquence, ni d’aucun autre paramètre ; nous la modifierons en conséquence par la suite. Avant d’implanter ce schéma dans un projet, il nous faut d’abord déterminer les données à placer dans la mémoire (lors de l’implantation d’une ROM, Quartus impose de connaître ces données).

1.1 Initialisation de la mémoire L’implantation des données en mémoire se fait déclarant un fichier d’initialisation au moment de l’implantation de la mémoire dans la feuille graphique. Ce fichier, d’extension « .mif », pour « memory initialization file » (il existe d’autres possibilités), est un fichier texte précisant la valeur de chaque mot à chaque adresse. Pour obtenir des informations sur le format souhaité, taper « Memory Initialization File (.mif) Definition » dans la recherche de l’aide en ligne de Quartus. Observer la structure de ce type de fichier. Pour générer le fichier « .mif », il est possible d’entrer les 256 valeurs une par une (Quartus propose un éditeur de fichier .mif, mais n’importe quel éditeur de texte ferait l’affaire), nous allons les générer automatiquement à l’aide du logiciel Scilab dont une présentation est donnée en annexe. Ouvrir ce dernier et entrer le script suivant :

// programme d’écriture d'un fichier mémoire // clear; // // changement du répertoire courant vers celui de Quartus // ici e:\altera\descriptions\NCO\NCO1 chdir('e:\altera\descriptions\NCO\NCO1') ; // // définition des 256 incréments de phase correspondant aux adresses // et mise sous forme de vecteur colonne ft=0:255 ; ft=ft'; // // contenu de la mémoire, sinusoïde centrée sur le milieu de la dynamique des valeurs x=127*(1+sin(2*%pi*ft/256)); // // création et ouverture d’un fichier « mem.mif » en écriture fd=mopen("mem.mif","w"); // // écriture des adresses et données, sous forme d’entiers (%i), avec caractère de tabulation (\t) // séparées par « : » et ligne terminée par « ; », puis retour à la ligne (\n) mfprintf(fd,"\t%i : \t%i \t ; \n",ft,x); // // fermeture du fichier mclose(fd);

Ouvrir ensuite le fichier avec un éditeur de texte quelconque. Celui de Quartus ne convient cependant pas car il cherchera pour un fichier .mif la syntaxe que nous allons placer maintenant.

0 : 127 ; 1 : 130 ; 2 : 133 ; ……………………………………. 252 : 114 ; 253 : 117 ; 254 : 120 ; 255 : 123 ;

Modifier alors le fichier de manière à le rendre compatible avec un fichier « .mif ». On obtient finalement ceci :

étude d’un OCN, introduction aux méga-fonctions de Quartus

Denis Rabasté 3/24 IUFM Aix-Marseille

DEPTH = 256; WIDTH = 8; ADDRESS_RADIX =DEC; DATA_RADIX =DEC; CONTENT BEGIN 0 : 127 ; 1 : 130 ; 2 : 133 ; 3 : 136 ; 4 : 139 ; ……………………………………….. 252 : 114 ; 253 : 117 ; 254 : 120 ; 255 : 123 ; END;

Remarque : - ces dernières opérations pouvaient se faire également au moyen d’instructions Scilab ; il serait

également envisageable de décrire une fonction réalisant ces opérations automatiquement ; - il maintenant possible d’ouvrir le fichier avec l’éditeur de Quartus.

1.2 Saisie du schéma Ouvrir un nouveau projet, puis une nouvelle feuille graphique (.bdf ) et y implanter le compteur et la mémoire, par le biais des composants prédéfinis (clic droit dans la feuille, puis Enter Symbol ). Nous utiliserons : - le composant LPM_COUNTER de la bibliothèque c:\..\megafunction\arithmetic\ pour le

compteur ; la fenêtre qui s’ouvre alors permet de définir un compteur 8 bits, avec une horloge comme seul signal d’entrée ;

- la mémoire ROM LPM_ROM de la même bibliothèque c:\..\megafunction\storage ;. Paramétrer une mémoire de 256 mots de 8 bits, avec une seule horloge, déclarer le fichier mem.mif comme indiqué en annexe.

Bien que sur les circuits réels le nombre de bits utilisés soit important, nous nous contenterons ici d’une mémoire de 256 mots de 8 bits afin de ne pas trop alourdir le projet ; il sera aisé de le modifier par la suite. Placer les ports d’entrées et de sortie, faire une compilation en vue de simulation fonctionnelle. On notera au passage le temps de latence de deux coups d’horloge entre l’application d’une adresse et la présence de la sortie en mémoire :

étude d’un OCN, introduction aux méga-fonctions de Quartus

Denis Rabasté 4/24 IUFM Aix-Marseille

Demander alors l’affichage de la sortie sous forme analogique :

Ce qui va nécessiter de réécrire sur le vecteur de simulation :

Puis de demandant de nouveau l’affichage sous forme analogique :

Pour obtenir finalement le résultat suivant :

étude d’un OCN, introduction aux méga-fonctions de Quartus

Denis Rabasté 5/24 IUFM Aix-Marseille

2 Ajustement de la fréquence

Celle-ci pourrait être modifiée en divisant la valeur de la fréquence d’horloge, mais les performances du synthétiseur seraient atténuées par rapport à la solution retenue, présentée ci-après.

2.1 Modification du schéma de base La solution adoptée, beaucoup plus efficace, consiste à modifier l’incrément d’adressage de la mémoire (c’est à dire l’incrément de phase) en remplaçant le compteur par un additionneur suivi d’un registre fonctionnant à la fréquence d’horloge, comme l’indique le schéma ci-après :

VCCH INPUT

sortie[0..7]OUTPUTaddress[7..0]clock

q[7..0]

lpm_rom0

inst

DFFdata[11..0]clock q[11..0]

lpm_ff0

inst2

q[11..4]

q[11..0]OUTPUT

A

BA+B

dataa[11..0]

datab[11..0]result[11..0]

lpm_add_sub0

inst1VCCMF[11..0] INPUT

Si le nombre à l’entrée Mf augmente, la phase sur le bus d’adresse de la mémoire augmente également, et la mémoire est lue plus rapidement (toutes les valeurs n’étant pas lues comme dans le cas précédent). La fréquence de sortie augmente alors. On peut noter qu’un nombre de bit important sur l’additionneur et le registre permet une bonne précision au niveau de l’incrément de phase ; il n’est cependant pas nécessaire d’utiliser tous les bits pour lire la mémoire, ce qui permet de garder la précision tout en diminuant la taille de la ROM. On peut également remarquer que l’ensemble additionneur registre se comporte comme un intégrateur numérique ; si on place à l’entrée un nombre représentatif de la fréquence, une fois intégré, celui-ci représente la phase. A l’aide de l’explorateur Windows, créé un nouveau dossier de travail, y copier l’intégralité du projet précédent, ouvrir le projet du le nouveau dossier, et le modifier pour être conforme au schéma précédent avec les mégafonctions « lpm_ff » et « lpm_add_sub » qui se trouve dans les répertoires « storage » et « arithmetic » du dossier « megafunctions ». Tester votre projet par simulation. Voici un exemple de simulation avec une incrémentation de MF toute les 2 µs :

étude d’un OCN, introduction aux méga-fonctions de Quartus

Denis Rabasté 6/24 IUFM Aix-Marseille

2.2 Calcul de la fréquence de sortie et problème du filtrage Si L est la taille du bus du registre à incrémentation de phase, MF le nombre présent à l’entrée de commande de la fréquence (sur le bus MF) et FCK la fréquence du signal d’horloge H, nous avons alors en sortie une fréquence F0 :

F0=MF . FCK / 2 L

Le signal ainsi obtenu en sortie de la mémoire, est équivalent à un signal échantillonné et est donc soumis au théorème de Shannon. Dans notre cas la fréquence ne doit pas dépasser 25 MHz, ce qui correspond à MF=211D=100H. Dans la pratique, le filtrage réalisé n’étant pas parfait, on ne dépasse pas 0,2 à 0,4.FCK. On trouvera plus de détails sur ce point en annexe. On peut voir sur la simulation suivante l’effet du repliement de spectre, en imposant deux consignes complémentaires MF de FF0H et 00FH (la fréquence d’horloge à été réduite à 1 MHz afin de permettre le fonctionnement correcte de l’additionneur, ce qui ne change par la valeur maximal de MF).

2.3 Modulations Nous allons maintenant utiliser l’oscillateur numérique contrôlé comme modulateur de signaux numériques, par les techniques traditionnelles du déplacement de fréquence, de phase et d’amplitude. Nous testerons ensuite nos différentes solutions en utilisant le triple convertisseur numérique analogique vidéo ADV7123 de carte DE2 pour envoyer le signal modulé sur le connecteur VGA. Afin d’analyser facilement le signal, et surtout de synchroniser notre oscilloscope, nous sortirons également le signal modulant sur le connecteur VGA. On trouvera en annexe, un extrait de la documentation du CNA, ainsi que la connectique de la carte DE2 et de la sortie VGA ; pour des informations plus complètes, on consultera les documents ressources. Pour être efficaces, les technique de modulations de signaux numériques imposent que la fréquence de la porteuse soit un multiple du débit numérique (horloge « bits ») : - notre porteuse sera obtenue par la relation MF . 50 Mz / 212 où MF devra être impérativement une

valeur entière, faute de quoi, malgré une simulation correcte, la visualisation à l’oscilloscope sera instable ;

- l’horloge bit sera obtenue par division de l’horloge à 50 MHz et sera donc un sous multiple de cette valeur.

étude d’un OCN, introduction aux méga-fonctions de Quartus

Denis Rabasté 7/24 IUFM Aix-Marseille

Ces deux conditions nous imposent des fréquences de la forme . 50 Mz / 2n ; nous choisirons par exemple 1,5625 MHz (c'est-à-dire 50 MHz/25) et 3,125 MHz (c'est-à-dire 50 MHz/24) pour la porteuse (suivant le type de modulation), tandis que le débit numérique sera fixé à 1,5625 MHz.

2.3.1 Modulation de fréquence

L’entrée FM laisse la possibilité de réaliser une modulation numérique de fréquence. On souhaite transmettre un signal numérique de 1,5625 M bits/s par modulation à déplacement de fréquence (MDF : Modulation à Déplacement de Fréquence ou FSK : Frequency Shift Keying) sur une porteuse sinusoïdale, un niveau logique 0 du signal modulant imposant de 1,5625 MHz, tandis qu’un niveau logique 1 imposera 3,125 MHz. Le signal numérique en bande de base (code NRZ, Non Retour à Zéro) sera fournit par un générateur pseudo-aléatoire à 4 bascules (voir documentation en annexe). Proposer une synthèse des sous ensembles de ce projet, et validez vos solutions par des simulations fonctionnelles. Assembler les différents sous ensembles dans un schéma général, et valider par une simulation fonctionnelle. On enverra le signal modulé sur les bits de poids fort du convertisseur correspondant au canal rouge, tandis que le signal modulant NRZ sera envoyé sur le bit de poids fort du canal bleu. Les bits de poids faible non utilisés pour ces deux canaux seront forcés à 0. Vérifier que la fréquence d’horloge de la carte DE2 est adaptée à votre synthèse à l’aide de l’outil de détermination de fréquence maximale d’horloge. Programmer le FPGA et visualiser les signaux sur l’oscilloscope.

2.3.2 Modulation de phase

Proposer une modification du projet précédent pour moduler la porteuse en déplacement de phase (MDP : Modulation à Déplacement de Phase ou PSK : Phase Shift Keying) à partir du même signal NRZ, autour d’une porteuse à 1,5625 MHz.

2.3.3 Modulation d’amplitude

Proposer une modification du projet précédent pour moduler la porteuse en déplacement d’amplitude (MDA : Modulation à Déplacement d’Amplitude ou ASK : Amplitude Shift Keying) à partir du même signal NRZ, autour d’une porteuse à 1,5625 MHz. L’amplitude de la porteuse sera maximale pour un NL1 du signal NRZ et divisée par 2 pour un NL0.

2.3.4 Modulation de phase à plusieurs bits par symb ole

En vous inspirant des documents donnés en annexe, proposer une réalisation de modulateur de phase transmettant 2 bits par symbole.

2.3.5 Modulation d’amplitude à quadrature (MAQ ou Q AM)

En vous inspirant des documents donnés en annexe, proposer une réalisation de modulateur d’amplitude à quadrature, pour une constellation de 8 points.

étude d’un OCN, introduction aux méga-fonctions de Quartus

Denis Rabasté 8/24 IUFM Aix-Marseille

Annexe 1 : implantation des « méga-fonctions"

Le logiciel Quartus II propose un certain nombre d’IP (« Intellectual Properties », propriétés intellectuelles) synthétisant des fonctions complexes (mémoires, multiplieurs, comparateurs etc…) optimisées pour les circuits Altera. Ces IP, désignées par le terme « megafunction », sont regroupées dans des bibliothèques, incluant la « Library of Parameterized Modules » (LPM), regroupant les fonctions les plus complexes. On peut y accéder dans différentes descriptions (graphique, VHDL, Verilog etc…), nous nous limiterons à la description graphique (pour les autres descriptions, consulter l’aide). Deux possibilités d’implantation sont offertes : Dans l’éditeur graphique, par le menu contextuel puis Insert / Insert Symbol ou encore par le menu de la barre d’outils Edit / Insert Symbol on accède à la fenêtre de la figure suivante :

On a ensuite le choix entre les différentes bibliothèques proposées dans le logiciel, plus des bibliothèques personnelles. Celles-ci peuvent être ajoutées depuis l’éditeur graphique par le menu Assignments / Settings… / Librairies … . Parmi les bibliothèques d’origine, « megafunctions » propose des composants complexes, tandis que « primitives » propose, comme son nom l’indique des fonctions de base, comme des fonctions logique élémentaire, des bornes d’entrée sortie, des mise au NL1 ou NL0. Les anciennes fonctions de Maxplus II (bibliothèque « maxplus2 ») sont à utiliser avec précaution, les composants n’étant pas toujours « optimisés » pour le compilateur de Quartus. On peut obtenir une description détaillée des fonctions en ouvrant l’aide en ligne :

Une fois le composant choisi (dans l’exemple une mémoire ROM lp_rom), cliquer sur « OK » pour accéder au paramétrage, qui propose dans un premier temps de choisir entre différentes descriptions textuelles (en cas d’utilisation comme composant dans un programme VHDL ou Verilog), avant de définir la largeur du bus de données et d’adresse (256 données sur 8 bits dans notre exemple), les cellules du FPGA où la mémoire sera implantée (laisser en « auto »), le nombre de signaux d’horloge (une seule horloge dans notre cas).

étude d’un OCN, introduction aux méga-fonctions de Quartus

Denis Rabasté 9/24 IUFM Aix-Marseille

Le paramétrage propose ensuite de synchroniser les sorties sur l’horloge, puis de définir le fichier .mif où se trouverons les données de la ROM.

Pour ce dernier points, préciser au niveau de l’explorateur qui s’ouvre, que l’on cherche un fichier .mif et non .hex ; les deux dernières fenêtres suivantes se contentant de donner quelques informations.

Une fois le composant paramétré, le symbole s’affiche dans la feuille et il est possible de modifier le paramétrage par un double clic gauche sur le composant. La seconde solution commence de la même manière, mais après la première fenêtre, on sélectionne l’assistant « MegaWizard Plug-In Manager… » qui ouvre alors la fenêtre de gauche de la figure suivante, qui permet de créer un nouveau composant ou d’éditer un composant déjà créé :

étude d’un OCN, introduction aux méga-fonctions de Quartus

Denis Rabasté 10/24 IUFM Aix-Marseille

Si on valide un nouveau composant la fenêtre de gauche s’ouvre et permet de choisir parmi les composants de calcul (additionneur, multiplieurs…), les composants divers (multiplexeurs, décodeurs…) ou les composants de stockage (mémoires, registres…). On donne un nom au nouveau composant créé et on détermine l’endroit où on souhaite le stocker (répertoire qu’il faudra déclarer dans le projet par Assignment / Settings.. / Librairies… si ce n’est pas le même que le répertoire courant). Le paramétrage du composant est identique à la méthode précédente.

Annexe 2 : connexion des générateurs pseudo-aléatoi res

Le générateur pseudo aléatoire est composé de n bascules D synchrones, la sortie de chaque bascule étant reliée à l’entrée de la suivante. L’entrée de la première bascule est attaquée par un OU exclusif dont les entrées sont les sortie des bascules indiquées ci-dessous (la première bascule est de rang 1).

N sorties n sorties 3 2 3 8 4 5 6 8 4 3 4 9 5 9 5 3 5 10 7 10 6 5 6 11 9 11 7 6 7 12 1 4 6 12

étude d’un OCN, introduction aux méga-fonctions de Quartus

Denis Rabasté 11/24 IUFM Aix-Marseille

Annexe 3 : modulateur à déplacement de fréquence MD F : exemple de solution

Le diviseur fournit l’horloge du signal NRZ à 1,5625 MHz, tandis que le générateur pseudo-aléatoire impose une consigne MF de 128D=80H pour un NL0 du signal NRZ, et 256D=100H pour un NL1

address[7..0]clock

q[7..0]

lpm_rom0

inst

DFFdata[11..0]clock q[11..0]

lpm_ff0

inst2

A

BA+B

dataa[11..0]

datab[11..0]result[11..0]

lpm_add_sub0

inst1

H VLD

div_freq

inst3

HORVLD

SORTIE_NRZMF[11..0]

gene_alea

inst4

MF[11..0]

MF[11..0]

q[11..0]

VCCCLOCK_50 INPUT

PIN_N2

VGA_B[9]OUTPUT PIN_B12

VGA_R[1..0]OUTPUT PIN_C8PIN_F10

VGA_R[9..2]OUTPUT

PIN_G10PIN_D9PIN_C9PIN_A8PIN_H11PIN_H12PIN_F11PIN_E10

q[11..4]

VGA_BLANKOUTPUT PIN_D6

VGA_SYNCOUTPUT PIN_B7

VGA_CLKOUTPUT PIN_B8

VCC

GND

GND

NRZ

VGA_B[8..0]OUTPUT PIN_J13PIN_J14PIN_F12PIN_G12PIN_J10PIN_J11PIN_C11PIN_B11PIN_C12

Le diviseur LIBRARY ieee; USE ieee.std_logic_1164.all; USE ieee.std_logic_unsigned.all; -- ce programme génère un signal de validation d'horloge -- à 1,5625 MHz par division par 32 de l'horloge à 50 MHz ENTITY div_freq IS port ( H : IN STD_LOGIC; VLD : OUT STD_LOGIC); END div_freq; ARCHITECTURE archdiv OF div_freq IS --pour compter jusqu'a 31 il faut 5 bits SIGNAL X : STD_LOGIC_VECTOR (4 downto 0); BEGIN PROCESS (H) BEGIN --compteur modulo 32 IF (H'EVENT AND H = '1') THEN IF X >= 31 THEN X <= "00000"; ELSE X <= X + 1 ; END IF; END IF; END PROCESS; VLD<='1' when X="00000" else '0'; END archdiv;

Le générateur aléatoire LIBRARY ieee; USE ieee.std_logic_1164.all;

étude d’un OCN, introduction aux méga-fonctions de Quartus

Denis Rabasté 12/24 IUFM Aix-Marseille

-- ce programme génère en SORTIE_NRZ un signal pseudo-aléatoire de 15 symboles -- il produit en MF la consigne pour le NCO : 1,5625 MHz pour NL0, 3,125 MHz pour NL1 ENTITY gene_alea IS port ( HOR, VLD : IN STD_LOGIC; SORTIE_NRZ : OUT STD_LOGIC; MF : OUT STD_LOGIC_VECTOR(11 downto 0)); END gene_alea; ARCHITECTURE arch OF gene_alea IS SIGNAL X : STD_LOGIC_VECTOR (3 downto 0); BEGIN -- boucle de description du générateur pseudo-aléatoire à 4 bascules PROCESS (HOR) BEGIN if (HOR'event and HOR='1') and VLD='1' then X(0)<=X(3) XNOR X(2); for i in 0 to 2 loop X(i+1)<=X(i); end loop; end if; END PROCESS; SORTIE_NRZ<=X(3); -- configuration du NCO pour avoir 3,125 MHz pour un NL1 -- et 1,5625 MHz pour un NL0 MF<=x"100" when X(3)='1' else x"080" ; END arch;

Simulation

Validation de la fréquence d’horloge

étude d’un OCN, introduction aux méga-fonctions de Quartus

Denis Rabasté 13/24 IUFM Aix-Marseille

Annexe 4 : modulateur à déplacement de phase MDP : exemple de solutions

Il suffit cette fois d’agir directement sur le bus d’adresse de la mémoire en imposant en pointant soit le début de la mémoire, soit le milieu, suivant que l’on souhaite une phase de 0 (NL0, MP=0) ou une phase de 180° (NL1, MP=800 H ce qui donne ne gardant les 8 bits de poids fort pour le bus d’adresse 128D=80H)

address[7..0]clock

q[7..0]

lpm_rom0

inst

DFFdata[11..0]clock q[11..0]

lpm_ff0

inst2 A

BA+B

dataa[11..0]

datab[11..0]result[11..0]

lpm_add_sub1

inst5

A

BA+B

dataa[11..0]

datab[11..0]result[11..0]

lpm_add_sub0

inst1

HORVLD

SORTIE_NRZMP[11..0]

gene_alea

inst4

MP[11..0]AD[11..0]

AD[11..4]

q[11..0]

VGA_B[9]OUTPUT PIN_B12

VGA_B[8..0]OUTPUT PIN_J13PIN_J14PIN_F12PIN_G12PIN_J10PIN_J11PIN_C11PIN_B11PIN_C12

GND

VCCClock_50 INPUT

PIN_N2

VGA_SyncOUTPUT PIN_B7

VGA_BlankOUTPUT PIN_D6

VCC

VGA_CLKOUTPUT PIN_B8

GND

VGA_R[0..1]OUTPUT PIN_C8PIN_F10

VGA_R[9..2]OUTPUT

PIN_G10PIN_D9PIN_C9PIN_A8PIN_H11PIN_H12PIN_F11PIN_E10

12812

lpm_constant0inst6

MP[11..0]NRZ

H VLD

div_freq

inst15

Seule la dernière ligne du générateur pseudo-aléatoire (ainsi que le nom de la sortie) : MP : OUT STD_LOGIC_VECTOR(11 downto 0));

-- configuration du NCO pour avoir 180° pour un NL1 -- et 0° pour un NL0 MP<=x"800" when X(3)='1' else x"000" ; END arch;

étude d’un OCN, introduction aux méga-fonctions de Quartus

Denis Rabasté 14/24 IUFM Aix-Marseille

Annexe 5 : modulateur à déplacement d’amplitude MDA : exemple de solutions

Dans cet exemple, la sortie de la ROM est « multipliée » par 1 ou ½ (c'est-à-dire divisée par 2) suivant la valeur de NRZ.

address[7..0]clock

q[7..0]

lpm_rom0

inst

DFFdata[11..0]clock q[11..0]

lpm_ff0

inst2

H VLD

div_freq

inst3

A

BA+B

dataa[11..0]

datab[11..0]result[11..0]

lpm_add_sub0

inst1

HORVLD

SORTIE_NRZ

gene_alea

inst4

HORNRZS_ROM[7..0]

S_MDA[7..0]

mult

inst5

q[11..0]

NRZVLD

q[11..4]NRZNRZ

12812

lpm_constant0inst6

VGA_R[9..2]OUTPUT

PIN_G10PIN_D9PIN_C9PIN_A8PIN_H11PIN_H12PIN_F11PIN_E10

VGA_B[8..0]OUTPUT PIN_J13PIN_J14PIN_F12PIN_G12PIN_J10PIN_J11PIN_C11PIN_B11PIN_C12

VGA_SyncOUTPUT PIN_B7

VGA_BlankOUTPUT PIN_D6

VGA_CLKOUTPUT PIN_B8

GND

VCC

VGA_B[9]OUTPUT PIN_B12

GND

VGA_R[1..0]OUTPUT

PIN_C8PIN_F10

VCCClock_50 INPUT

PIN_N2

Le signal dans la ROM étant centré sur la valeur médiane 127, il peut être considéré comme une sinusoïde codée en binaire décalé ; la multiplication par ½ se traduit par : - si le MSB est au NL1 (partie positive de la sinusoïde), décalage d’un bit vers la droite des 6 bits de

poids faible et introduction d’un 0 entre le MSB et les 6 LSB ; - si le MSB est au NL0 (partie négative de la sinusoïde), décalage d’un bit vers la droite des 6 bits

de poids faible et introduction d’un 1 entre le MSB et les 6 LSB . LIBRARY ieee; USE ieee.std_logic_1164.all; -- ce programme conserve intégralement la sortie S_ROM de la ROM si NRZ=1 -- et divise par 2 l'amplitude (par rapport à 127) si NRZ=0 ENTITY mult IS port ( HOR, NRZ : IN STD_LOGIC; S_ROM : IN STD_LOGIC_VECTOR(7 downto 0); S_MDA : OUT STD_LOGIC_VECTOR(7 downto 0)); END mult; ARCHITECTURE arch OF mult IS BEGIN PROCESS (HOR) BEGIN if (HOR'event and HOR='1') then -- pas d'action si NRZ=1 if NRZ='1' then S_MDA<=S_ROM; -- si NRZ=0 division par 2 (décalage à droite) des LSB pour la partie positive elsif S_ROM(7)='1' then S_MDA<=S_ROM(7)&'0'& S_ROM(6 downto 1); -- NRZ=1, division par 2 des LSB de la partie négative else S_MDA<=S_ROM(7)&'1'& S_ROM(6 downto 1); end if; end if; END PROCESS; END arch;

Le signal MP du générateur pseudo-aléatoire a été supprimé.

étude d’un OCN, introduction aux méga-fonctions de Quartus

Denis Rabasté 15/24 IUFM Aix-Marseille

Annexe 6 : CAN vidéo de la carte DE2

La carte DE2 intègre un triple convertisseur numérique analogique ADV7123 dont un extrait de la documentation constructeur est représenté ici (pour plus d’information, on consultera la documentation complète dans les documents ressources) : - le schéma fonctionnel interne ci-contre : - les niveaux sur les sorties analogiques, et la

table de vérité du composant ci-dessous :

La figure suivante donne l’implantation du composant au sein de la carte DE2 :

étude d’un OCN, introduction aux méga-fonctions de Quartus

Denis Rabasté 17/24 IUFM Aix-Marseille

Annexe 7 : notions de base sur Scilab

(extrait de « Introduction au traitement du signal avec Scilab » même auteur) Les outils logiciels sont devenus un élément indispensable en traitement du signal, que ce soit pour l’apprentissage ou le développement de système, en particulier depuis l’apparition des techniques numériques. Un signal numérisé peut être en effet vu comme une suite de valeurs, c’est à dire un vecteur. Un vecteur n’est qu’une matrice à une ligne ou une colonne. Dans le cas de traitement d’images par exemple, les signaux étant à deux dimensions, on arrive directement à la notion de matrices. On pourrait trouver de nombreux exemples où le signal à traiter présente une dimension supérieure encore. Il était donc naturel de se tourner vers des logiciels spécialisés en calcul matriciel, tel que Matlab (contraction de MAtrix LABoratory). Nous utiliserons pour notre part un logiciel quasiment similaire, Scilab (pour SCIentific LABoratoty), qui présente l’avantage par rapport au précédent d’être libre et gratuit. Scilab est développé par l’INRIA Rocquencourt (78). On peut le télécharger gratuitement avec sa documentation et de nombreuses applications, à l’adresse :

http://scilabsoft.inria.fr/ Les possibilités de Scilab sont très importantes, notre objectif est ici de passer en revue les fonctionnalités de base, ainsi que celles qui nous seront utiles pour le traitement du signal. Quelques règles pratiques Avant toutes choses, il faut comprendre que Scilab est un langage interprété (comme le Basic) et non compilé (comme le C ou le Pascal). Les premiers programmes seront écris ligne par ligne directement dans l’éditeur de Scilab ; lorsqu’on a un peu l’habitude, il est cependant plus efficace d’utiliser un éditeur de texte annexe, comme le bloc note de Windows ou WordPad, puis de faire ensuite des copier coller (attention le « ctrl V » ne fonctionne pas dans Scilab, on fera donc « clic droit » puis « paste »). Passons maintenant en revue quelques règles pratiques : - pour chaque fonction, une aide est disponible en tapant « help Nom_de_la_fonction » à l’invite. - en cas d’erreur, il est inutile de réécrire les instructions, les flèches du clavier permettant de se

déplacer dans le jeu des instructions précédemment entrées ; les touches de raccourci « Ctrl C » et « Ctrl V » pour le copier coller ne fonctionnent pas sous Scilab ; utiliser le menu contextuel accessible par un clic droit dans la fenêtre.

- Scilab fait la différence entre majuscules et minuscules. - il est fortement conseillé de définir en début de programme toutes les constantes de manière

littérale, afin de pouvoir modifier simplement l’une d’elle par la suite, si nécessaire. Initialiser Avant de commencer un nouveau programme, il est conseillé d’initialiser toutes les variables du logiciel par l’instruction « clear » (en minuscules), à moins que l’on souhaite garder des variables précédemment définies. Entrer un vecteur ligne Plusieurs syntaxes possibles : -->s=[0 1 2 3] s = ! 0. 1. 2. 3. !

-->s=[0,1,2,3] s = ! 0. 1. 2. 3. !

-->s=[0:1:3] s = ! 0. 1. 2. 3. !

-->s=[0:3] s = ! 0. 1. 2. 3. !

La troisième syntaxe se lit comme un vecteur allant de 0 à 3 par pas de 1, celui-ci étant 1 par défaut il peut être omis comme dans la quatrième syntaxe. Dans le cas d’un incrément, les crochets peuvent être omis, ou remplacés par des parenthèses :

étude d’un OCN, introduction aux méga-fonctions de Quartus

Denis Rabasté 18/24 IUFM Aix-Marseille

-->s=(0:3) s = ! 0. 1. 2. 3. !

-->s=0:3 s = ! 0. 1. 2. 3. !

Un point virgule à la fin de la ligne évite l’affichage du résultat. -->s=0:3; Entrer un vecteur colonne Plusieurs syntaxes possibles : -->s1=[0;1;2;3] s1 = ! 0. ! ! 1. ! ! 2. ! ! 3. !

-->s1=[0:3]' s1 = ! 0. ! ! 1. ! ! 2. ! ! 3. !

-->s1=[0:1:3]' s1 = ! 0. ! ! 1. ! ! 2. ! ! 3. !

-->s1=s' s1 = ! 0. ! ! 1. ! ! 2. ! ! 3. !

Mettre des vecteurs bout à bout, former des matrice s -->s2=[0 1 2 3; 0 1 2 3] s2 = ! 0. 1. 2. 3. ! ! 0. 1. 2. 3. !

-->s2=[s;s] s2 = ! 0. 1. 2. 3. ! ! 0. 1. 2. 3. !

-->s2=[s1';s1'] s2 = ! 0. 1. 2. 3. ! ! 0. 1. 2. 3. !

Accéder aux éléments d’une matrice -->s(0) !--error 21 invalid index

-->s(1) ans = 0.

-->s(1:2:4) ans = ! 0. 2. !

-->s2(2,3) ans = 2.

Les deux premières syntaxes montrent que le premier indice d’une matrice est toujours « 1 » dans Scilab, et non « 0 ». La troisième syntaxe permet d’accéder aux éléments de rang 1 à 4 de « s » par pas de 2. Matrices particulières -->zeros(2,3) ans = ! 0. 0. 0. ! ! 0. 0. 0. !

-->ones(3,2) ans = ! 1. 1. ! ! 1. 1. ! ! 1. 1. !

-->eye(3,4) ans = ! 1. 0. 0. 0. ! ! 0. 1. 0. 0. ! ! 0. 0. 1. 0. !

-->rand(3,2) ans = ! .0683740 .7263507 ! ! .5608486 .1985144 ! ! .6623569 .5442573 !

On précise à chaque fois, dans l’ordre le nombre de lignes et de colonnes souhaitées. La première écriture donne une matrice de « 0 », la seconde de « 1 », la troisième une matrice dont les éléments de la diagonale sont des « 1 » et les autres des « 0 », et la dernière donne des éléments aléatoire entre « 0 » et « 1 ». Données particulières Elles sont précédées du symbole « % ». Citons : - le nombre π, soit %pi ,

étude d’un OCN, introduction aux méga-fonctions de Quartus

Denis Rabasté 19/24 IUFM Aix-Marseille

- l’imaginaire pur, soit %i, - et très utiles pour lever certaines indéterminations, le plus petit nombre manipulable par Scilab

(2,22 10-16), soit %eps , ainsi que les type vrai, %t, et faux, %f. Opérations particulières On trouve évidemment : - les opérations d’addition « + » (les matrices doivent alors avoir même dimension), - de soustraction « - » (les matrices doivent alors avoir même dimension), - de multiplication « * » entre matrices (le nombre de colonnes de la première matrice doit alors être

égal au nombre de lignes de la seconde), de même que la multiplication de tous les éléments de la matrice par un nombre,

- de division « / », - la mise à puissance de 10, avec « e », par exemple 10e3 (soit 1000). A ne pas confondre avec ces deux dernières les multiplications et divisions éléments par éléments, notées respectivement « .* » et « ./ ». Les matrices doivent alors avoir même dimension. Observons l’exemple ci-après (à lire de gauche à droite) : -->A=[0,1;2,3] A = ! 0. 1. ! ! 2. 3. !

-->B=[4,5;6,7] B = ! 4. 5. ! ! 6. 7. !

-->C=A*B C = ! 6. 7. ! ! 26. 31. !

-->D=A .*B D = ! 0. 5. ! ! 12. 21. !

On trouvera le même mode de fonctionnement avec la fonction élévation à la puissance et les symboles « ^ » et « .^ ». Citons également quelques opérations spécifiques : - size (A) qui donne le nombre de ligne et colonnes de A, - length (A) qui donne le nombre d’éléments de A, - matrix (A, m, n) qui redimensionne A sur m ligne et n colonnes (la lecture se fait colonne par

colonne), - sum(A) qui renvoie un nombre correspondant à la somme de tous les éléments de la matrice, - sum(A,’r’) qui renvoie un vecteur ligne (‘r’ pour row) dont chaque élément est la somme des

éléments de la colonne correspondante de A, - sum(A,’c’) qui renvoie un vecteur colonne (‘c’ pour column) dont chaque élément est la somme

des éléments de la ligne correspondante de A, - triu(A) qui ne garde que la valeur des éléments du triangle (« tri » pour triangle) supérieur (« u »

pour up) de la matrice (diagonal comprise) et place des « 0 » ailleurs, - tril(A) qui ne garde que la valeur des éléments du triangle (« tri » pour triangle) inférieur (« l »

pour low) de la matrice (diagonal comprise) et place des « 0 » ailleurs, - A’ qui renvoie la matrice A transposée et conjuguée, - conj(A) qui renvoie la matrice A conjuguée. Fonctions particulières Citons les principales : - sqrt( ), la racine carrée, - sin( ), cos( ), tan( ) les sinus, cosinus et tangente, - asin( ), acos( ), atan( ) les fonctions inverses des précédentes, - exp( ), log( ) les fonctions exponentielle et logarithme népérien, - 10^( ), log10( ) les fonctions puissance de 10 et logarithme décimal, - real( ), imag( ) les fonctions partie réelle et imaginaire d’un complexe, - abs( ), phasemag( ) les fonctions module et phase d’un complexe. Exemple Voici un exemple de tracé de la représentation temporelle et fréquentielle d’une sinusoïde.

étude d’un OCN, introduction aux méga-fonctions de Quartus

Denis Rabasté 20/24 IUFM Aix-Marseille

clear // définition des constantes, nombre de points, période d’échantillonnage et fréquence du signal N=1000 ; Te=0.1e-3 ; F=100 ; // // description du vecteur temps t=Te*(0:N-1); // // description du vecteur signal s=5*sin(2*%pi*F*t); // // définition d'une variable fréquence pour l'affichage du spectre // le premier point correspond au continu, le dernier à la fréquence d'échantillonnage au pas près f=1/(N*Te)*( 0 : N-1) ; // // calcul du module de la transformée de Fourrier sf=1/N* abs(fft(s,-1)) ; // // initialisation de l'affichage xbasc(); xset("font size",4); // // affichage de la représentation temporelle // dans le coin en haut à gauche de la fenëtre graphique (coordonnées 0,0) // sur toute la largeur et sur une demi-hauteur xsetech([0,0,1,1/2]) ; plot2d(t,s); xtitle(“représentation temporelle”,”temps (s)”,”amplitude (V)”) // // affichage du module corrigé de 0 à fe/2 // à gauche à la moitié de la hauteur de la fenêtre graphique (coordonnées 0,1/2) // sur toute la largeur et sur une demi-hauteur xsetech([0,1/2,1,1/2]) ; plot2d3(f(1:N/2), sf(1:N/2)) ; xtitle("module corrigé en fonction de la fréquence de 0 à fe/2","fréquence (Hz)","amplitude (Vs)");

0 0.01 0.02 0.03 0.04 0.05 0.06 0.07 0.08 0.09 0.10-5-4-3-2-1012345

représentation temporelle

temps (s)

amplitude (V)

0 1e3 2e3 3e3 4e3 5e30

0.4

0.8

1.2

1.6

2.0

2.4

2.8module corrigé en fonction de la fréquence de 0 à fe/2

fréquence (Hz)

amplitude (Vs)

étude d’un OCN, introduction aux méga-fonctions de Quartus

Denis Rabasté 21/24 IUFM Aix-Marseille

Annexe 8 : Spectre d’un signal issu de la synthèse numérique directe

Le principe de la synthèse numérique directe consiste à lire les mots d’un mémoire, chaque mot correspondant à une valeur instantanée du signal synthétisé. L’adressage de la mémoire se fait comme nous l’avons vu par l’addition, à chaque front d’une horloge de référence de fréquence FCK , d’une valeur MF (incrément de fréquence) à la valeur de l’adresse précédente. Cet ensemble, additionneur et registre de mémorisation, est appelé registre à incrémentation. Ce signal sera ensuite filtré pour atténuer les harmoniques. Si L est le nombre de bits du registre à incrémentation, MF la consigne de fréquence (sur le bus FM) et FCK la fréquence du signal d’horloge, nous avons alors en sortie une fréquence F0 :

F0=MF . FCK / 2 L

Remarque : les L bits du registre à incrémentation n’adressent pas tous forcément la mémoire : seuls les bits de poids fort sont parfois utilisés pour cet adressage, ce qui ne change pas l’expression précédente. Si les mots mémorisés correspondent à une sinusoïde, le signal en sortie de la mémoire peut être vu comme un signal sinusoïdal, de fréquence F0, échantillonné et bloqué à la fréquence FCK. Le classique théorème de Shannon s’applique donc à ce signal, la fréquence F0 ne doit pas dépasser FCK /2. Dans la pratique, le filtrage réalisé n’étant pas parfait, on ne dépasse pas 0,2 à 0,4.FCK. Voici l’exemple de la génération d’un signal, à partir d’une fréquence d’horloge de 20 MHz, pour L=12 et MF=29 . La fréquence de sortie vaut alors 1,25 MHz.

0 0.2 0.4 0.6 0.8 1.0 1.2 1.4 1.60

40

80

120

160

200

240

280

sinusoïde en sortie du CNA

temps en µs

amplitude

Comme on peut le voir sur le chronogramme, le signal comprend cette fois un nombre d’harmoniques important, mettant en évidence le problème du filtrage et du repliement de spectre. Ce signal est le résultat d’un blocage d’ordre 0 d’une sinusoïde à 1,25 MHz multipliée dans le domaine temporel par un peigne de Dirac de 20 MHz (échantillonnage). Dans le domaine fréquentiel, cela se traduit par la convolution d’une raie à 1,25 MHz par un peigne de Dirac à 20 MHz (spectre du signal en sortie du bloqueur), le résultat multiplié par la réponse en sinus cardinal du bloqueur.

étude d’un OCN, introduction aux méga-fonctions de Quartus

Denis Rabasté 22/24 IUFM Aix-Marseille

-1e6 0 1e6 2e6 3e6 4e6 5e6 6e6 7e6 8e6 9e60

2e84e86e88e8

10e812e814e816e8

spectre du signal de sortie (sans le blocage)

fréquence (Hz)

amplitude

-1e6 0 1e6 2e6 3e6 4e6 5e6 6e6 7e6 8e6 9e60

2e-84e-86e-88e-8

10e-812e-814e-816e-8

réponse fréquentielle du bloqueur

fréquence (Hz)

amplitude

-1e6 0 1e6 2e6 3e6 4e6 5e6 6e6 7e6 8e6 9e60

20406080

100120140

spectre en sortie du CNA

fréquence (Hz)

amplitude

Nous retrouvons bien sur le spectre du signal de sortie du CNA une raie en continu (notre signal est centré sur 127), ainsi que la raie à 1,25 MHz. L’amplitude de cette dernière est environ 127/2 (il s’agit d’un spectre bilatéral), atténué légèrement par la réponse du bloqueur. Les autres raies à k.FCK +/- F0 (k étant un entier), dues à l’échantillonnage du signal (à 10 MHz) sont fortement atténuées par le blocage. Entre le fondamental à 1,25 MHz et le premier harmonique à 8,75 MHz, il y a une atténuation d’environ19 dB. Nous pouvons voir sur ces représentations que notre signal doit vérifier le théorème de Shannon et ne pas avoir une fréquence supérieure à FCK/2, ce qui limite MF à 7FF en hexadécimal.

étude d’un OCN, introduction aux méga-fonctions de Quartus

Denis Rabasté 23/24 IUFM Aix-Marseille

Annexe 9 : Modulations angulaires

Rappels théoriques L’expression ci-après rappelle l’équation d’un signal modulé en fréquence :

]tm(t))K(Fsin[2πU(t)u F0Pm += La fréquence instantanée vaut alors :

)t(mKF)t(f F0 +=

tandis que la phase instantanée vaut :

∫π+π=ϕ dtm(t)K2tF2(t) F0

L’indice de modulation δ est défini comme l’écart de phase ∆ϕ autour de la phase 2πF0t de la porteuse. Dans le cas d’un signal modulant sinusoïdal, soit m(t)=Ui sin(2π fi t), l’intégration due au passage de la fréquence à la phase du signal, nous amène à l’expression :

i

iF

fUK=δ

Comme on peut le constater, l’indice de modulation dépend de l’amplitude et de la fréquence du signal informatif. Lorsque plusieurs fréquences sont mises en jeu, on prend la plus élevée pour définir cet indice (qui sera alors d’autant plus faible). L’expression d’un signal modulé en phase est la suivante :

]m(t)KtFsin[2πU(t)u P0Pm += La fréquence instantanée a pour expression :

dt

)t(mdK

21

F)t(f P0 π+=

tandis que la phase instantanée vaut : )t(mKtF2(t) p0 +π=ϕ

L’indice de modulation, toujours défini comme l’écart de phase autour de la phase de la porteuse, a pour expression dans le cas du signal informatif sinusoïdal précédent :

iP UK=δ Ce bref rappel permet de mettre en évidence que pour faire une modulation de phase avec un modulateur de fréquence, il suffit de dériver d’abord le signal informatif. De même, pour faire une modulation de phase avec un modulateur de fréquence, il faut d’abord intégrer le signal modulant.

Transmission d’informations numériques

Modulation à déplacement de fréquence MDF ou FSK (F requency Shift Keying)

Le principe consiste à associer autour de la fréquence porteuse FP une fréquence FP+∆F pour le niveau logique 1 et FP-∆F pour le niveau logique 0. Si D est le débit binaire, l’indice de modulation est généralement défini par δ=2∆F/D. Les valeurs de cet indice classiquement utilisées pour leur bon compromis « débit numérique / encombrement spectral » sont 2/π et 1/2.

Modulation à déplacement de phase MDP ou PSK (Phase Shift Keying)

Le principe consiste à associer une phase (0 et π) particulière de la porteuse pour chaque niveau logique. Ce principe se prête bien à la transmission de plusieurs bits par phase, ce qui peut être représenté par une constellation comme celle qui suit où 3 bits sont envoyés par phase.

étude d’un OCN, introduction aux méga-fonctions de Quartus

Denis Rabasté 24/24 IUFM Aix-Marseille

axe desréels

axe desimaginaires

000

001

111

110

100

101

010

011

Chaque point représente l’extrémité du vecteur de Fresnel de la porteuse, en fonction du « tribit » envoyé. La modulation est généralement de type différentiel, la référence n’étant pas une phase absolue, mais celle du symbole précédent ; dans la constellation de l’exemple, un écart de phase de +3π/4 par rapport au symbole précédent correspond au tribit 100. Le passage d’un symbole au symbole le plus proche sur la constellation se fait par un code Gray (un seul bit change à la fois), de manière à limiter les erreurs en cas de confusion entre deux symboles voisins.

Modulation d’amplitude en quadrature MAQ ou QAM (Qu adrature Amplitude Modulation)

La modulation à déplacement de phase devient peu performante lorsque le nombre de bits transmis par phase augmente, la lecture des phases devenant problématique. Aussi utilise t-on aussi une modulation d’amplitude en plus, pour obtenir par exemple la constellation suivante où 4 bits sont transmis à chaque symbole :

axe desréels

axe desimaginaires

Ce type de modulation peut être vu comme la somme de deux modulations d’amplitude, dont les porteuses de même fréquence, serait en quadrature. On en déduit alors le schéma du modulateur.

Horloge bitHB

signalmodulé

registreà décalage

D

données

division par 4de fréquence

déphaseur90°

+

X

Xregistreparallèle

Oscillateur(fréquence porteuse)

CNA2 bits

CNA2 bits

Q3

Q2

Q0

Q1

Q3

Q2

Q0

Q1

D3

D2

D0

D1

Ck Ck