TD ARCHITECTURE DES EQUIPEMENTS INFORMATIQUES COMBINATOIRE...

Transcript of TD ARCHITECTURE DES EQUIPEMENTS INFORMATIQUES COMBINATOIRE...

IUT1 GRENOBLE RT Architecture des équipements informatiques TD 2013/2014 p.1/1

TD ARCHITECTURE DES EQUIPEMENTS INFORMATIQUES COMBINATOIRE ET SEQUENTIELLE

TD1: les nombres Numération:

écrire en base 16:

%1001.0101.1101

%1110.0110.1010

écrire en base 2

0xE0BD217A

0xA0E15B

Écrire en base 10

0xFD4

%1011.0110.0010

Écrire en base 16

1234

54865

Faire les opérations suivantes:

binaire: 1101.1111.1010 + 1010.1111.0110

1011.0110.0010 + 0111.1101.0110

hexadécimal:

0x2578 + 0xAB45

0x7748 + 0x3AA7

210 = 1024 = 1K

1Ko signifie 1 kilo octet

un octet est constitué de 8 bits

1Ko comporte donc 1024 octets, c'est-à-dire 8192 bits

Combien y a t'il de bits dans 2Mo ?

IUT1 GRENOBLE RT Architecture des équipements informatiques TD 2013/2014 p.2/2

TD2: ALGEBRE BINAIRE

1 - Simplifier les expressions logiques suivantes :

. S0 = A+B+/B

. S1 = A+(B./B)

. S2 = A + /A

. S3 = A.(B + /B)

. S4 = A + A./B

. S5 = A.B+B.C+A.B.C

. S6 = A.B+/A

2 - Développer:

. S7 = (A + B).(A + /B)

. S8=A.B+A.B

IUT1 GRENOBLE RT Architecture des équipements informatiques TD 2014/2015 p.3/3

TD3: Tables de vérités:

1. Faire le tableau de vérité de S1 à S5 :

S1 = /E1 + E2

S2 = E1./E2

S3 = /E1

S4 = E1.E2+/E1

S5= E1.E2 E1.E2 (ajouter une colonne pour /S5)

2. Donner les équations des sorties S6 à S8 en fonction des entrées E3 et E4

Entrées sorties

E3 E4 S6 S7 S8 S9 S10

0 0 0 0 1 0 1

0 1 0 1 1 1 0

1 0 1 0 0 1 0

1 1 0 1 1 0 1

Déterminer l'équation d'un OU EXCLUSIF :

sans utiliser de OU

sans utiliser de ET

3. Établir les tables de vérité des fonctions G1, G2 et G3 en fonction des entrées A, B et C:

G1= /A.B + /B./C G2 = C .(/B +A) G3 = /A.C + A./C

4. Chronogramme:

Compléter le chronogramme suivant

d'après ce tracé, déterminer ce que vaut s, en fonction de b :

. pour a=0

. pour a=1

a

b

s =

1

a

b

s

1

1

1

0

0

0 t

t

t

IUT1 GRENOBLE RT Architecture des équipements informatiques TD 2014/2015 p.4/4

TD4. Combinatoire: analyse et synthèse

1. Donner les équations de S et de R en fonction de A et B.

Puis simplifier ces équations.

2. Réaliser avec des fonctions de bases les fonctions S7, S8 et S9

S7 = /(A+/B).C

S8 = A + B + C

S9 = /A + B.(C + /D)

en utilisant des portes à une ou 2 entrées au choix.

3. Donner l'équation de s et compléter son chronogramme.

IUT1 GRENOBLE RT Architecture des équipements informatiques TD 2014/2015 p.5/5

5. Analyse de schéma :

Donner les équations logiques des signaux E, F et G en fonction de A, B, C et D

Obtenir les mêmes signaux de sorties (E, F et G) en utilisant :

seulement des OU et des NON

puis seulement des ET et des NON

6. Donner les équations de S, E et I en fonction de A et B.

IUT1 GRENOBLE RT Architecture des équipements informatiques TD 2014/2015 p.6/6

TD5 Bascules

1. compléter les chronogrammes 1 et 2 d'une bascule D.

Chronogramme 1:

Chronogramme 2:

C

D

Q

C

D

Q

IUT1 GRENOBLE RT Architecture des équipements informatiques TD 2014/2015 p.7/7

2, Déterminer les chronnogrammes des sorties S0 et S1

Tracer S0, D1 et S1 en supposant S0=0 et S1=0 à t=0.

1D

C1

Q

/Q

& D

S0

D1

CK

1D

C1

S1

CK

D

S0

D1

S1

IUT1 GRENOBLE RT Architecture des équipements informatiques TD 2014/2015 p.8/8

Déterminer les signaux des sorties des bascules :

on suppose Q1=0 et Q2=0 à t=0

3. Tracer les chronogrammes: NIVEAUX ELECTRIQUES

>C1

1D

CK

/Q

Q

CK

Q

D = /Q

Q2 >C1

1D /Q2

>C1

1D

CK

/Q1

Q1

Data

CK

Data

Q1

Q2

IUT1 GRENOBLE RT Architecture des équipements informatiques TD 2014/2015 p.9/9

TD 6: Exercices de logique séquentielle. Compléter les chronogrammes suivants:

EXERCICE 2

Faire le chronogramme des sorties du système suivant en prenant Qa = Qb = 0 à t=0

Qa

Qb

Db

1D

>C1

1D

>C1

Qa

Qb

Ck

Db

IUT1 GRENOBLE RT Architecture des équipements informatiques TD 2014/2015 p.10/10

EXERCICE 3

Pour étudier le plus simplement possible ce type de circuits il est préférable d'en faire la

table d'évolution à partir de laquelle on pourra facilement obtenir le chronnogramme.

Table d'évolution:

dans cette table le passage d'une ligne à la suivante à lieu au front actif de l'horloge:

Q1 Q2 D1 D2

0 0

Pour compléter cette table il faut connaître les équations de D1 et D2 et déterminer D1 et

D2 pour les valeurs de Q1 et Q2 sur la ligne considérée.

puis ces valeurs de D1 et D2 deviennent celles de Q1 et Q2 après le front, c'est-à-dire à

la ligne suivante,

on peut alors déterminer à nouveau D1 et D2 …

Quelles séquences réalisent Q2 et Q1 (Q1 poids fort) d'une part, et D2 et Q1 d'autre

part?

>C1

>C1

1D

1D =1

CK Q2

D1

Q1

D2

IUT1 GRENOBLE RT Architecture des équipements informatiques TD 2014/2015 p.11/11

EXERCICE 4

Donner les équations combinatoires et séquentielles des signaux, puis faire la table

d'évolution des signaux (à t=0 toutes les sorties sont à 0).

1D

>C1

1D 1D

>C1 >C1

&

Q0

Q1 Q2

CK

IUT1 GRENOBLE RT Architecture des équipements informatiques TD 2014/2015 p.12/12

T.D 7 décodage d'adresse des boîtiers mémoires

On veut utiliser 4 circuits mémoires pour un système à microprocesseur. Établir les liaisons :

Quelles sont les capacités des circuits mémoires ? Quelle est la capacité d’adressage du microprocesseur ?

DONNER UN TABLEAU AVEC LES ADRESSES A COMPLETER

IUT1 GRENOBLE RT Architecture des équipements informatiques TD 2014/2015 p.13/13

Placer les circuits mémoires RAM0 et RAM1, à partir de l’adresse 0. Déterminer leurs adresses de début et de fin. Donner les équations des CS. Comment attribuer à RAM1 l’espace mémoire qui commence à l’adresse 0x300 et à RAM2 celui qui débute en 0x400 ? Faire alors un plan mémoire indiquant la totalité de la mémoire adressable et les zones attribuées à chacun des boîtiers.

On veut utiliser 4 circuits mémoires pour un système à microprocesseur. Établir les liaisons :

A0-A6

D0-D7

R/W

CS

A0-A6

D0-D7

R/W

CS

A0-A6

D0-D7

R/W

CS

A0-A6

D0-D7

R/W

CS

A0-A10

D0-D7

R/W

D0-D15

A0-A7

A0-A7

A0-A7

A0-A7

IUT1 GRENOBLE RT Architecture des équipements informatiques TD 2014/2015 p.14/14

Étude à partir d'un schéma et de chronogramme

on considère la portion de circuit suivante, le microprocesseur n'est pas représenté: il génère les signaux R/W et les bits d'adresses (A0 à A4) et communique avec les circuits par le bus de données non représenté.

On a relevé les signaux indiqués à gauche du schéma. Indiquer dans le tableau ci dessous, pour chaque étape du chronogramme: la case mémoire adressée dans un circuit (adresse dans le boitier mémoire) le circuit mémoire adressé: C1, C2 ou C3 le sens de l'échange, mode lecture ou écriture pour le microprocesseur R/W = 0 pour l'écriture R/W=1 pour la lecture

Donner les équations des CS0 à CS3 afin d’obtenir des adresses mémoires contiguës à partir de

l’adresse 0x400

&

&

&

1 2 3 4 5

C1 A0/A2

R/W

CS

C2 A0/A2

R/W

CS

C3 A0/A2

R/W

CS

A0/A2

R/W

A3

A0

A1

A2

A3

A4

R/W

A4

IUT1 GRENOBLE RT Architecture des équipements informatiques TD 2014/2015 p.15/15

Etape Case mémoire Circuit mode 1

2

3

4

5

IUT1 GRENOBLE RT Architecture des équipements informatiques TD 2014/2015 p.16/16

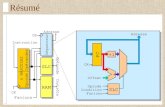

TD 8. Unité logique et accumulateur L'objectif de ce TP est de construire un embryon de microprocesseur, la structure

proposée n'est évidemment pas la seule possible.

Pour notre processeur rudimentaire le bus de données transmet en parallèle un certain

nombre de bits :

Des bits indiquant l’opération à effectuer (code instruction)

Des bits indiquant la donnée à traiter par l’opération

(pour concevoir notre système complet il faudrait ajouter une mémoire dans laquelle se

trouve les codes successifs composant notre programme. Il faut alors ajouter un circuit

mémoire)

Cette structure, pour laquelle chaque instruction du programme contient un code

d’instruction et une donnée, n’est pas la seule possible, ni la plus employée en réalité.

1. Unité logique:

On propose le schéma suivant pour réaliser une unité de calcul logique :

A

=1 A'

z0

& S'

B =1 S

=1 B'

z1 z2

rappel sur le OU EXCLUSIF : 𝑆 = 𝐴⊕ 𝐵 = �̅�. 𝐵 + 𝐴. �̅�

Table de vérité : Table de vérité réduite :

A B S

0 0 0

0 1 1

1 0 1

1 1 0

selon les valeurs respectives de z0, z1 et z2, on obtient les valeurs:

A ou /A pour A' (selon la valeur de z0) et

B ou /B pour B' (selon z1) et enfin

S' ou /S' pour S (selon z2).

on a toujours S' = A' . B'

par exemple pour z0= 0, z1=1 et z2=0, on obtient:

z0=0 => A'=A

z1=1 => B'=/B

z2=0 => S=S' donc S=A./B

A S

0 B

1 /B

IUT1 GRENOBLE RT Architecture des équipements informatiques TD 2014/2015 p.17/17

écrire, en appliquant le même raisonnement, les équations de S’ et S en fonction de A et

B pour chacune des combinaisons de z0, z1 et z2:

Z0 Z1 Z2 S' S

0 0 0

0 0 1

0 1 0 A./B A./B

0 1 1

1 0 0

1 0 1

1 1 0

1 1 1

2. Décodeur d'instructions:

Le circuit précédent peut être considéré comme l'embryon d'une Unité Logique puisque

selon le code de commande placé sur z0, z1 et z2 on peut obtenir 8 équations logiques

(on ne peut cependant pas obtenir S= A, S= B, S=/A , S=/B ainsi que les

OUEXCLUSIFS).

Le système peut être également représenté ainsi:

z2

z1

z0

A

UL

S

B

z0, z1 et z2 permettent de choisir la fonction réalisée par le système, on dit aussi

l’INSTRUCTION.

A et B sont les entrées de données du système.

S est donc le résultat de l’instruction codée sur z2, z1 et z0, sur les données A et B.

On désire utiliser seulement les 4 instructions: OU, NON OU, ET et NON ET.

Le choix entre ces 4 instructions est donc possible avec seulement deux signaux (ZD0 et

ZD1)

Le système complet devient:

ZD0 z2

décodeur z1

ZD1 z0

S

A

B UL

IUT1 GRENOBLE RT Architecture des équipements informatiques TD 2014/2015 p.18/18

ZD0 et ZD1 sont les bits qui contiennent le code de l’instruction. On a choisi d’utiliser

les codes suivants pour ZD1 et ZD0:

ZD1 ZD0 z0 z1 z2

0 0 A OU B

0 1 NON (A ET B)

1 0 NON (A OU B)

1 1 A ET B

Compléter la table de vérité en fonction des équations trouvées à la question 1, et en

déduire les équations de z0, z1 et z2 en fonction de ZD0 et ZD1.

3. Evolution du format des données:

Une unité de calcul (généralisation d'une unité logique obtenue en ajoutant des

possibilités de calcul arithmétique, de décalages…) peut être représentée de la façon

suivante:

X est la donnée à traiter et C le code de l’opération à réaliser : bus de données

Y est le second opérande (donnée) et R le résultat

En comparaison avec le circuit précédent :

l’opération est réalisée sur des mots de 3 bits :

X est composée de x2, x1 et x0

De même pour Y et R : y2, y1, y0 et r2 ,r1 ,r0

Le code, C, est au format 2 bits : pour coder les 4 opérations logiques de base.

Les opérations logiques sont effectuées bit à bit :

Par exemple pour un ET :

R= X . Y => r2 =y2.x2 r1 = y1.x1 r0 = y0.x0

Cette unité de calcul est purement combinatoire: pour une combinaison de X, Y et C on

obtient une valeur de R, toujours la même.

4. Accumulateur

Puisque le système doit transmettre le code de l’instruction et un opérande en même

temps cela oblige, pour les opérations à 2 opérandes, d’avoir mémorisé un des opérandes

(Y). Cette mémoire s’appelle registre accumulateur.

Par exemple pour réaliser l’opération 010 ET 011 (2 ET 3) il faut:

Charger 010 dans l’accumulateur

Faire un ET entre 011 et l’accumulateur

(Stocker résultat)

Il y a donc 2 opérations (instructions) à exécuter : CHARGEMENT puis ET

3

X

R

2

Y

C

3 Unité de calcul

IUT1 GRENOBLE RT Architecture des équipements informatiques TD 2014/2015 p.19/19

Le registre accumulateur est réalisé avec des bascules D.

Sur le bus de données parviennent en même temps le code de l’instruction (C) et

l’opérande (X).

Les opérations sont faites entre X, donnée transmise avec le code de l’opération sur le

bus de données, et Y, valeur précédemment mémorisée dans l’accumulateur (par une

instruction de chargement, ou résultat d’une opération précédente).

Pour chaque instruction il y a deux temps :

Présentation code et opérande : le résultat est immédiatement obtenu en R

Front sur clock pour mémoriser le résultat dans l’ACCU

Travail demandé: Réaliser les connexions sur le schéma suivant :

Bus de données

les instructions possibles, par l’UL, sont les suivantes:

Code héxa Code c1 c0 binaire Instruction mnémonique

0 00 R = X LOAD_ACCU

1 01 R = X OU Y OU_ACCU

2 10 R = X ET Y AND_ACCU

3 11 R = X OUEX Y OUEX_ACCU

Pour réaliser une instruction il faut procéder ainsi :

Placer la donnée (code et opérande) sur le bus de données (inters)

Faire une impulsion sur clock (mémorisation du résultat dans l’accumulateur)

Donner les codes de la suite d’opérations suivante puis indiquer la suite des contenus de

l’accumulateur obtenue lors de l’exécution de cette suite d’instructions:

LOAD_ACCU 4

Unité de calcul

X

Y = ACCU

R

C

Registreaccumulateur

clock

ACCUBUS DE DONNEESBUS DE DONNEES

33

3

2

C1

R2

R1

R0

R3

X0

X1

X2

Y0

C0

X3

Y1

Y2

Y3

D0

D1

D2

D3

D4C0

D5C1

IUT1 GRENOBLE RT Architecture des équipements informatiques TD 2014/2015 p.20/20

OUEX_ACCU 7

LOAD_ACCU 6

AND_ACCU 3

LOAD_ACCU 2

OU_ACCU 4

IUT1 GRENOBLE RT Architecture des équipements informatiques TD 2013/2014 p.21/21

TD 8 nombres signés, nombres fractionnaires

Nombres signés (format 8 bits)

donner la valeur décimale des nombres signés (8 bits en complément à 2 )

suivants :

%0110.1100 %1110.1000 0x25 0xEE

0x30 0x60 0x90 0xE0

Calculer, en hexa, au format 8 bits :

0x30+0x60 0x30+0x90 0x90+0x90 0xE0+0xE0

Donner dans chaque cas le résultat et si il est correct ou non.

Nombres fractionnaires

1. Déterminer l’équivalent décimal de A = %0,1010

2. Virgule flottante :

écrire les nombres 2 et 0,1

au format float

3. Décoder les nombres 32 bits en virgule flottante suivants :

0xE0BD217A

0x2C791AFE

remplir le tableau en respectant le format 8 bits:

Des opérations de

la

Nombre ou

résultat hexadéci

mal

Valeur décimale en non signé

Valeur décimale en

signé

Résultat décimal non

signé

attendu

Résultat décimal signé

attendu

retenue overflow

X 0x30 x x x x

X 0x60 x x x x

X 0x90 x x x x

x 0xE0 x x x x

0x30 + 0x30 0 0

0x30 + 0x60 0 1

0x30 + 0xE0 1 0

0x30 + 0x90 0 0

0x90 + 0x90 1 1

0xE0+ 0xE0 1 0

IUT1 GRENOBLE RT Architecture des équipements informatiques TD 2013/2014 p.22/22

Compléter la 2° colonne en plaçant le résultat en héxadécimaldes opérations indiquées

dans la 1° colonne

indiquer dans la 3° colonne la valeur décimale de la 2° colonne en considérant des

nombres signés

idem pour la 4° colonne en considérant des nombres non signés

indiquer dans la 5° colonne la valeur décimale attendue en effectuant les opérations de la

1° colonne en considérant des valeurs non signées

idem dans la 6° colonne en considérant des valeurs signés

indiquer dans les colonnes suivantes si l'opération a généré une retenue et/ou un

overflow