Systèmes logiques et électronique associée

Transcript of Systèmes logiques et électronique associée

1

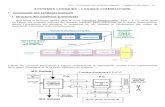

Systèmes logiques et

électronique associée

Michel MATHIEU

122 janvier 2004 Supélec : Michel MATHIEU

Plan

Systèmes logiques et électronique associée

Algèbre de Boole et fonctions de commutationCircuits de logique et réalisation des fonctions

Systèmes séquentiels synchrones et basculesAspects temporels des systèmes

Électronique des systèmes logiquesFamilles logiques

Systèmes particuliers

230 janvier 2004 Supélec : Michel MATHIEU

2

Plan

Système de logique séquentielle

3Supélec : Michel MATHIEU

Principes des systèmes synchrones

Bascules synchrones

Automates synchrones

Registres synchrones

Compteurs synchrones

Systèmes complexes synchrones29 janvier 2004

Définition des systèmes séquentiels

Approche asynchrones et bascules asynchrones

Système de logique séquentielle

Système de logique séquentielle synchrone

417 février 2003 Supélec : Michel MATHIEU

Système où la connaissance du vecteur d’entrée ne suffit plus pour la détermination du vecteur de sortie.

On peut obtenir des vecteurs de sortie différents pour un même vecteur d'entrée.

Pour un vecteur d’entrée donné, le vecteur de sortie dépend, non seulement de ce vecteur, mais aussi d'une certaine succession de vecteurs appliqués à l'entrée

L’état actuel est généralement fonction de la séquence des vecteurs appliqués antérieurement.

Il y a un effet mémoire.

3

Système de logique séquentielle

Système de logique séquentielle synchrone

517 février 2003 Supélec : Michel MATHIEU

Deux grandes catégories de système de logique séquentielle :

les systèmes asynchrones- systèmes asynchrones à réaction directe, - systèmes asynchrones à bascules asynchrones

à réaction directe, - …

les systèmes synchrones- systèmes totalement synchrones, - …

Séquentiel asynchrone à réaction directe

Système de logique séquentielle asynchrone

629 janvier 2004 Supélec : Michel MATHIEU

Entrées Sorties Systèmecombinatoire

(l , L)

variablesinternes

excitationssecondaires

4

Notion de système séquentiel : mémoire

Système de logique séquentielle asynchrone

729 janvier 2004 Supélec : Michel MATHIEU

0

0

0

1

S

R

Q

Q'

1

0

1

1

1

1

1

0

0

1

0

1

1

0mémoire

Bascules asynchrones (Latches)

Bascule

qRSQ .∨=+

S.R = 0

8Supélec : Michel MATHIEU

RS

0

q1

Q+

00

11

SR

Table de vérité

état mémoire

1

Q+1

01

001

0

10

ne pas utiliser

Q-

S RQ

Q'

S

R

29 janvier 2004

5

Bascules asynchrones (Latches)

Bascule SR

qRSQ .∨=+

S.R = 0

9Supélec : Michel MATHIEU

0

q1

SR

Q+

11

00

Table de vérité

état mémoire

0

Q+0

10

110

1

10

ne pas utiliser

Q-

S RS

R

Q

Q'

29 janvier 2004

Bascules asynchrones (Latches)

Bascule SR,

10Supélec : Michel MATHIEU29 janvier 2004

Q

Q'

S

R

Q

Q'

S

R

RS

0

Q+R0

S

10

110

1

10

Q-

S

1

Q+

101

001

0

10

Q-

R

S.R = 0

6

Bascule SR asynchrone à validation (SRE)

Bascules asynchrones à validation (Enable Latch)

1129 janvier 2004 Supélec : Michel MATHIEU

Q

Q'

S

R

E0

Q+R

0

S

10

110

1

10

E

11

11

XX 0

S.R.E = 0

Q-Q-

E= 0 mémoire isolée

Bascule D asynchrone à validation (DE)

Bascules asynchrones à validation (Enable Latch)

Supélec : Michel MATHIEU 12

D

E

Q

Q’

29 janvier 2004

s Q

Q'r

D

E

S

R

1

Q+E0

D

0X

1101

Q-E= 0 mémoire isolée

7

Mode d’utilisation recommandé

Bascules asynchrones à validation (Enable Latch)

13Supélec : Michel MATHIEU

E

S

R

Q

Q'

30 janvier 2004

Mode d’utilisation fortement déconseillé

Bascules asynchrones à validation (Enable Latch)

14Supélec : Michel MATHIEU

E

S

R

Q

Q'

29 janvier 2004

8

Système séquentiel totalement synchrone

Système de logique séquentielle synchrone

1517 février 2003 Supélec : Michel MATHIEU

Système échantillonné.Instants d’échantillonnage définis par un signal H(très généralement périodique).

Les transitions du système se font uniquement aux instants d’échantillonnage.

Entre deux instants d’échantillonnage le système est parfaitement stable.

Systèmes totalement synchrones

Système de logique séquentielle synchrone

1617 février 2003 Supélec : Michel MATHIEU

tH

Entrées et excitations des bascules

Sorties des bascules et du système

Εj

Εk

Ei

Sl

Sm

Sn

9

Systèmes totalement synchrones

Système de logique séquentielle synchrone

1717 février 2003 Supélec : Michel MATHIEU

tH

ϕ0

ϕ1

ϕ2

ϕ3

2 30 1 n-1n-2

ϕn-1

ϕn-2

État d’un système de logique séquentielle

Système de logique séquentielle synchrone

1817 février 2003 Supélec : Michel MATHIEU

État d’un système : ensemble des variables qui le décrivent complètement

variables d’états.

Variables d’état d’un système séquentiel : • variables (primaires, externes, entrées),• variables internes.

10

Système de logique séquentielle synchrone

Système de logique séquentielle synchrone

19Supélec : Michel MATHIEU

Variables internes mémorisées dans des mémoires(bascules) et ne varient pas pendant au moins toute une phase d’horloge.

Naturel et aisé de définir un état interne du système par l’ensemble des valeurs de ses variables internes.

Évolution du système (ϕn à ϕn+1) dépend des valeurs à l’instant d’échantillonnage • des variables internes, • des variables externes d’autre part.

état global du système

26 janvier 2004

Graphe d’évolution des états

Système de logique séquentielle synchrone

2015 mai 2003 Supélec : Michel MATHIEU

un noeud représente un état interne particulier, caractérisé par les valeurs des variables internes (il peut recevoir une désignation, par exemple ici i, en rapport direct ou pas avec les valeurs des variables internes).

[VP]

[VP]

- une branche orientée reliant deux noeuds(ou revenant au noeud de départ) représente l’évolution du système vers un nouvel état interne qui ne dépend que de l’état interne initial et des valeurs des variables externes à l’instant d'échantillonnage.

11

Graphe d’évolution des états

Système de logique séquentielle synchrone

2129 janvier 2004 Supélec : Michel MATHIEU

i

i j[VP] k[VP]

Un système séquentiel synchrone peut parfaitement évoluer alors que ses entrées ne varient pas.

Si NE entrées, épanouissement d’un maximum de branches à partir d’un nœud quelconque.

EN2

Système de logique séquentielle synchrone

Graphe d’évolution des états

état interne présent

état global présent

états internes futurs

i

( )−−+ = EVIfVI ,( )EVIgS ,=

2217 février 2003 Supélec : Michel MATHIEU

12

Tableau d’évolution des états

Système de logique séquentielle synchrone

2315 mai 2003 Supélec : Michel MATHIEU

Le graphe peut se traduire par un tableau

EN2

états internes présentsphase n

états internes suivants

phase n+1

Valeurs vecteur d’entrée présent n

Systèmes totalement synchrones

Système de logique séquentielle synchrone

2415 mai 2003 Supélec : Michel MATHIEU

"top d’horloge" ou "coup d’horloge "

tetr

t

Excitation

Sortie

0

0

échantillonnageModèle d’horloge

13

Mémoire élémentaire

Système de logique séquentielle synchrone

2515 mai 2003 Supélec : Michel MATHIEU

Q

D

H

Échantillonnage et mémoire élémentaire

Constatation : Qn+1=Dn

D

H

Q

Q’

Mémoire élémentaire

Système de logique séquentielle synchrone

2615 mai 2003 Supélec : Michel MATHIEU

D0 1 D

État nprésent

État n+1suivant

01 0

0 11

DnQn

Qn+11,0 1,110

0,1

0,0

01 1

Qn0

Qn+1Dn

Bascule DQn+1=Dn

D,Q

14

Évolution des sorties

Système de logique séquentielle synchrone

2730 janvier 2004 Supélec : Michel MATHIEU

[VP]2

i[VP]5

[VP]4

[VP]3

[VP]1[S]1

[S]4

[S]2

[S]3

[S]5

Sorties dépendantes du vecteur d’entrée

C’est le cas le plus général.

À chaque branche issue d’un même nœud donné, correspond un vecteur de sortie particulier dont la valeur est liée à la valeur du vecteur d’entrée.MELAY

Évolution des sorties

Système de logique séquentielle synchrone

28Supélec : Michel MATHIEU

Sorties indépendantes du vecteur d’entrée

Le vecteur de sortie peut être toujours le mêmequelque soit la branche issue d’un même noeud. Alors ce vecteur est indépendant du vecteur d’entrée et ne dépend que de l’état interneconsidéré.

[VP]2

i[VP]5

[VP]4

[VP]3

[VP]1

[S]

MOORE

30 janvier 2004

15

Bascule D

Bascules synchrones (Flip Flop)

2915 mai 2003 Supélec : Michel MATHIEU

D0 1 D

État nprésent

État n+1suivant

01 0

0 11

DnQn

Qn+11,0 1,110

0,1

0,0

01 1

Qn0

Qn+1Dn

1

Qn+1Dn0

10

Table de vérité

Qn+1= Dn

D,Q

Bascule D

Bascules synchrones (Flip Flop)

3015 mai 2003 Supélec : Michel MATHIEU

Mémoire élémentaire

Bascule retard

Bascule si

D

H

Q

Q’D QQ ='

Qn+1= Dn

16

Bascule T

Bascules synchrones (Flip Flop)

3115 mai 2003 Supélec : Michel MATHIEU

T,Q

01 0

Qn1

Qn+1TnTable de

vérité

1,0 0,110

1,1

0,0 État nprésent

État n+1suivant

01 1

0 10

TnQn

Qn+1

0 1T

T

nnnnnnn QTQTQTQ ⊕=∨=+ ..11

Qn+1Tn0 nQ

nQ

état mémoire

Bascule T

Bascules synchrones (Flip Flop)

3215 mai 2003 Supélec : Michel MATHIEU

Bascule trigger

Diviseur par deux

T

H

Q

Q’

Q

T

H

17

Bascule JK

Bascules synchrones (Flip Flop)

3315 mai 2003 Supélec : Michel MATHIEU

JK,Q10,0

00,110

01,1

00,0 11,0

11,101,0 10,1

0JJ

KK1

JK

JKJ

H

Q

Q’K

État nprésent

État n+1suivant

01

0

JnKn

Qn

Qn+1

1 101 0 0 1

Bascule JK

Bascules synchrones (Flip Flop)

3415 mai 2003 Supélec : Michel MATHIEU

0JJ

KK1

JK

JK

Table de vérité

nnnnn QKQJQ ..1 ∨=+

0

Qn+1Kn0 nQ

nQ

Jn

10

110

1

10

00

Qn

1

JnKn

Qn+1

1 11

00

état mémoire

18

Bascules synchrones (Flip Flop)

Bascule SRSR,Q

État nprésent

État n+1suivant

01

0

SnRn

Qn

Qn+1

101 0 1

Condition à respecterS.R = 0

00,11000,0 10,0

01,101,0 10,1

S10

R S

R

S

H

Q

Q’R

3515 mai 2003 Supélec : Michel MATHIEU

Bascules synchrones (Flip Flop)

Bascule SR

Table de vérité

nnnn QRSQ .1 ∨=+

0

Qn+1Rn0 nQ

Sn

10

110

1

10

0

Qn

1

SnRn

Qn+1

11

00

S10

R S

R

ne pas utiliser

S.R = 0état mémoire

3629 janvier 2004 Supélec : Michel MATHIEU

(origine technologique)

19

Bascules synchrones (Flip Flop)

Bascules et variantes niveau « actif » H (ou 1)

bascules synchrones D, T, JK ou SR

niveau « actif » L (ou 0)bascules synchrones

niveau « actif » H ou L (1 ou 0)bascules synchrones

RSKJ,T,D ou

RSRS,KJ,KJ ou

0

Qn+1Kn

0 nQ

nQ

Jn

10

110

1

10

1

Qn+1

1 nQ

nQ

01

001

0

10

nKnJ

1

Qn+1

1 nQ

nQ

10

000

1

10

nKnJ

3715 mai 2003 Supélec : Michel MATHIEU

Transformations de bascules synchrones

Bascules synchrones (Flip Flop)

3815 mai 2003 Supélec : Michel MATHIEU

Toute fonction de bascule peut-être obtenue à partir d’une autre fonction de bascule

20

Transformations de bascules synchrones

Bascules synchrones (Flip Flop)

3915 mai 2003 Supélec : Michel MATHIEU

Toute fonction de bascule peut-être obtenue à partir d’une autre fonction de bascule

JK en D, D en JK, …

J

K

D Q

Q'H

J Q

Q'HK

D

Transformations de bascules synchrones

Bascules synchrones (Flip Flop)

4029 janvier 2004 Supélec : Michel MATHIEU

SR (ou JK) en D

JK en T

S Q

Q'

HR

D J Q

Q'

HK

T

21

Bascules synchrones (Flip Flop)

Transformations de bascules synchronesSR en JK

S Q

Q'

HR

J

K

nnnn QRSQ .1 ∨=+

( ) nnnnnnnnnnnnnnn QKQJQQKQJQQKQJQ .......1 ∨=∨∨=∨=+

4115 mai 2003 Supélec : Michel MATHIEU

Bascules synchrones (Flip Flop)

Transformations de bascules synchronesD en JK

J

K

D Q

Q'H

4215 mai 2003 Supélec : Michel MATHIEU

22

Bascules synchrones (Flip Flop)

Transformations de bascules synchronesT en JK

J

K

T Q

Q'H

4315 mai 2003 Supélec : Michel MATHIEU

Automate : spécification

Synthèse des systèmes totalement synchrones

Supélec : Michel MATHIEU 4430 janvier 2004

Entrée A (totalement synchrone)

Obtention d’un signal en sortie S, si et seulement si A reste au niveau haut pendant une seule phase d’horloge.

H

A

S

Phase fondamentale du projet

23

Description par graphe des états

Synthèse des systèmes totalement synchrones

Supélec : Michel MATHIEU 458 février 2003

0 1A

,SA

A2

0,0

1,00,1

1,0

1,0

0,0

État nprésent

État n+1suivant

01 0

0 12

An

2 0 2

Description par tableau des états

Synthèse des systèmes totalement synchrones

Supélec : Michel MATHIEU 468 février 2003

État nprésent

Sortie nprésente

01 1

0 00

An

2 0 0

État nprésent

État n+1suivant

01 0

0 12

An

2 0 2

0 1A

,SA

A2

24

Codage du tableau des états

Synthèse des systèmes totalement synchrones

Supélec : Michel MATHIEU 478 février 2003

État nprésent

Sortie nprésente

02 0

0 00

An

1 1 0

État nprésent

État n+1suivant

02 0

0 12

An

1 0 2

XY QQ XY QQnXnY QQ ,, nXnY QQ ,,

Tableau binaire des états

Synthèse des systèmes totalement synchrones

Supélec : Michel MATHIEU 488 février 2003

État nprésent

État n+1suivant

02 0

0 12

An

1 0 2

XY QQnXnY QQ ,,

XY QQ

An00 11

010000

01

1,1, ++ nXnY QQnXnY QQ ,,

25

Tableau binaire des états

Synthèse des systèmes totalement synchrones

Supélec : Michel MATHIEU 498 février 2003

1, +nYQXY QQ

An00 11

010000

01

1, +nXQXY QQ

An

001

00 0

XY QQ

An

011

00 1

XY QQ

An

000

01 0

nS

SortieVariables internes

Qn+1= Dn

Exemple : réalisation avec bascules D

Synthèse des systèmes totalement synchrones

Supélec : Michel MATHIEU 508 février 2003

A DQx

Q'xH

DQy

Q'yH

S

ADX = XY QAD .= YQAS .=

26

Chronogramme

Synthèse des systèmes totalement synchrones

Supélec : Michel MATHIEU 518 février 2003

QX

A

H

Q’X

DY

QY

Tables directes et inverses T et D

Synthèse des systèmes totalement synchrones

Supélec : Michel MATHIEU 5210 février 2003

1

Qn+1Tn0 nQ

nQ 0

Qn+10

Tn

10

110

1

Qn0

11

0

0

Qn+10

Dn

10

110

1

Qn0

10

1

1

Qn+1Dn0

10

1+⊕= nnn QQT 1+= nn QD

27

Table directe et inverse JK

Synthèse des systèmes totalement synchrones

Supélec : Michel MATHIEU 5310 février 2003

0

Qn+1Kn0 nQ

nQ

Jn

10

110

1

10

0

Qn+1 Kn0

Jn

10

110

1

Qn

10

10

Table directe et inverse SR

Synthèse des systèmes totalement synchrones

Supélec : Michel MATHIEU 5410 février 2003

0

Qn+1Rn0 nQ

Sn

10

110

1

10

0

Qn+1 Rn0

Sn

10

110

1

Qn

10

100

0

S.R = 0

28

Synthèse JK : Excitations de la bascule X

Synthèse des systèmes totalement synchrones

Supélec : Michel MATHIEU 5510 février 2003

XY QQ

An

1, +nXQ

011

00 1

XY QQ

An

0-1

-- -

XnJXY QQ

An

-0-

11 0

XnK

AJ X = AK X =

Synthèse JK : Excitations de la bascule Y

Synthèse des systèmes totalement synchrones

Supélec : Michel MATHIEU 5610 février 2003

1, +nYQXY QQ

An

001

00 0

XY QQ

An

001

0- -

YnJXY QQ

An

---

-1 1

YnK

XY QAJ .= 1=YK

29

Validation (Enable)

Bascules synchrones à validation (Enable Flip Flop)

Supélec : Michel MATHIEU 5710 février 2003

Entrée qui permet • de valider le fonctionnement normal• d’inhiber le fonctionnement (état mémoire)

D

H

Q

Q’E

T

H

Q

Q’E

J

H

Q

Q’K

E

Bascule JK à validation (JKE)

Bascules synchrones à validation (Enable Flip Flop)

Supélec : Michel MATHIEU 5810 février 2003

0

Qn+1Kn

0 nQ

nQ

Jn

10

110

1

10

En

11

11

nQXX 0j Q

Q'

H

k

EJ

K

30

Bascule SR à validation (SRE)

Bascules synchrones à validation (Enable Flip Flop)

Supélec : Michel MATHIEU 5929 janvier 2004

s Q

Q'

H

r

ES

R0

Qn+1Rn

0 nQ

Sn

10

110

1

10

En

11

11

nQXX 0

S.R.E = 0(origine technologique)

Bascule D à validation (DE)

Bascules synchrones à validation (Enable Flip Flop)

Supélec : Michel MATHIEU 6010 février 2003

• E = 0 état mémoire• E = 1 bascule D

D

E

DQ

Q'H 1

Qn+1En0 nQ

Dn

1X

1010

31

Bascule D à validation (DE)

Bascules synchrones à validation (Enable Flip Flop)

Supélec : Michel MATHIEU 6110 février 2003

S Q

Q'

HR

D

E Et Q

Q'H

T

Autre commande : Remise à zéro synchrone

Bascules synchrones (Flip Flop)

Supélec : Michel MATHIEU 6229 janvier 2004

Dd

Q

Q'H

RAZ

0

Qn+10

Dn

10

110

10

nRAZ00

1