Examen Architecture SP 2011-2012

-

Upload

wajdi-bellil -

Category

Documents

-

view

56 -

download

0

Transcript of Examen Architecture SP 2011-2012

Ministre de lEnseignement Suprieur ******* Institut Suprieure des Sciences Appliques et de la Technologie de GafsaNom : Prnom : No CIN : Groupe : ..

No NoEXAMEN DARCHITECTURE SESSION PRINCIPALERemarque : - Document non autoris - Noublier pas dcrire la formule avant chaque calcule

Exercice n1 :(7.5 pts)

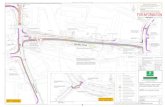

La figure ci-dessous prsente une mmoire vive (RAM) , une mmoire morte (ROM) et de deux priphriques (P1 et P2) qui sont accessibles un microprocesseur via les bus dadresse A15-A0(16 bits), de donne D7-D0 (8 bits) et de commande. Les mmoires et les priphriques sont compatibles en largeur avec le microprocesseur. Sachant que la RAM sera situe dans les adresses les plus faibles, viendront ensuite la ROM et les deux priphriques. 1. Donnez la taille du bus dadresse de chaque mmoire et de chaque priphrique (1.5 pts)

1

Ne Rien crire ici2. Calculer la capacit en octet de chaque mmoire et de chaque priphrique (1.5 pts) 3. Donner, pour chaque mmoire et chaque priphrique, la plage dadresses quil occupe dans lespace dadressage du microprocesseur. (1.5 pts) . 4. Pour la suite, on dsire ajouter un priphrique P3 de taille 1 ko. Dterminer le nombre de bus dadresse ncessaire pour ce priphrique. (1.5 pts) 5. Complter le schma de cblage de P3 sur la figure ci-dessus. (1.5 pts)

2

Exercice n2 :( 7.5pts)Une instruction peut sexcuter en 6 phases (6 instructions lmentaires) : LI DI LR EX AM ER

LI : accs au cache instructions (lecture de linstruction) DI : Dcode LR : Lecture des oprandes dans le banc de registres EX : Calculs des oprations arithmtiques et logiques AM : accs au cache donnes ER: Ecriture du rsultat dans le banc de registres

Donnes:Dure dune instruction lmentaires = 1 cycle dhorloge. Nombre dinstructions excuter = 10 instructions.

1. Exprimer la dure totale dexcution des 10 instructions en nombre de cycles dhorloges selon le modle squentielle (architecture classique). ( 1.5 pts)

2. Exprimer la dure totale dexcution des 10 instructions en nombre de cycles dhorloges selon le modle pipelin. ( 1.5 pts) 3. Exprimer la dure totale dexcution des 10 instructions en nombre de cycles dhorloges selon le modle pipeline et superscalaire avec 2 units de traitements. (1.5 pts) 4. Dterminer le nombre dinstructions qui peuvent tre effectu, si on dispose dune dure gale 30 cycles. a-selon le modle classique : (1.5 pts) b-selon le modle pipelin 6 tages : (1.5 pts)

3

QCM : (5 pts) 1. Le bus de donne permet de transmettre les donnes du Processeur la mmoire centrale et vice versa Registre la mmoire centrale et vice versa Processeur la mmoire 2. Combien dadresse peut-on gr si le bus dadresse est de dimension 20 bits? 20 adresses 20-1 adresses 2 20 adresses 2 20 -1 adresses 3. Les priphriques dentre sortie sont? Clavier Processeur CDROM Moniteur Cl USB 4. Larchitecture RISC des microprocesseurs est une architecture : Simple o chaque instruction effectue une seule opration complexe. Son jeu d'instruction est reduit Qui ncessite un compilateur complexe Qui ncessite un nombre important de registres 5. Les processeurs pipelines prsentent les problmes suivants : Problme de conflit Alas de donnes Alas structurels Excution des micro-instructions en parallle

Bon Travail4