chap 2.pdf

-

Upload

tarikmlilas -

Category

Documents

-

view

56 -

download

7

Transcript of chap 2.pdf

Chapitre 2 : Présentation des éléments du langage VHDL

Vhsic Hardware Description LanguageVhsic : Very High Speed Integrated Circuit

Langage de description de systèmes matériels

L’abréviation VHDL signifie VHSIC Hardware Description Language(VHSIC : Very High Speed Integrated Circuit). Ce langage a été écrit dans les années 70 pour réaliser la simulation de circuits électroniques.

On l’a ensuite étendu en lui rajoutant des extensions pour permettre la conception (synthèse) de circuits logiques programmables (P.L.D. Programmable Logic Device).

Auparavant pour décrire le fonctionnement d’un circuit électronique programmable les techniciens et les ingénieurs utilisaient des langages de bas niveau ou plus simplement un outil de saisie de schémas.

Actuellement la densité de fonctions logiques (portes et bascules) intégrée dans les PLDs est telle (plusieurs milliers de portes voire millions de portes) qu’il n’est plus possible d’utiliser les outils d’hier pour développer les circuits d’aujourd’hui.

2. Présentation des éléments du VHDL2.1. Qu’est ce que le VHDL?

28/10/2014 11:18 R. EL ALAMI 2

Les sociétés de développement et les ingénieurs ont voulu s’affranchir des contraintes technologiques des circuits. Ils ont donc créé des langages dits de haut niveau à savoir VHDL et VERILOG.

Ils permettent au code écrit d’être portable, c’est à dire qu’une description écrite pour un circuit peut être facilement utilisée pour un autre circuit.

Il faut avoir à l’esprit que ces langages dits de haut niveau permettent de matérialiser les structures électroniques d’un circuit.

En effet les instructions écrites dans ces langages se traduisent par une configuration logique de portes et de bascules qui est intégrée à l’intérieur des circuits. C’est pour cela qu’on préfère parler de description VHDL ou VERILOG que de langage.

2. Présentation des éléments du VHDL2.1. Qu’est ce que le VHDL?

28/10/2014 11:18 R. EL ALAMI 3

Le schéma structurel que l'on utilise depuis si longtemps et si souvent n'est en fait qu'un outil de description graphique.

Aujourd'hui, l'électronique numérique est de plus en plus présente et tend bien souvent à remplacer les structures analogiques utilisées jusqu'à présent.

Ainsi, l'ampleur des fonctions numériques à réaliser nous impose l'utilisation d'un autre outil de description.

Il est en effet plus aisé de décrire un compteur ou un additionneur 64 bits en utilisant l'outil de description VHDL plutôt qu'un schéma.

2. Présentation des éléments du VHDL2.2. Pourquoi un langage de description?

28/10/2014 11:18 R. EL ALAMI 4

Le VHDL (Very High Speed Integrated Circuit, Hardware Description language) est le fruit du besoin de normalisation des langages de description de matériel (Première norme IEEE 1076-87 en décembre 1987).

Auparavant, chaque fournisseur de CAO proposait son propre langage de modélisation (GHDL chez GENRAD, BLM ou M chez Mentor Graphics, Verilog chez Cadence etc...) mais aussi un autre langage pour la synthèse et encore un autre pour le test. Au début des années 80, le ministère de la défense des Etats Unis (D.O.D) confiait le soin à Intermetrics, IBM et Texas Instruments de mettre au point ce langage.

L'objectif était bien sûre de s'assurer une certaine indépendance vis à vis des fournisseurs de matériels et de logiciels et ainsi une assurance de maintenabilité des équipements.

2. Présentation des éléments du VHDL2.3. Historique

28/10/2014 11:18 R. EL ALAMI 5

En 1994 la version IEEE 1076-93 suivie du standard IEEE 1164 fut établie (Normalisation des signaux logiques multivaleurs)

Il y aura aussi la norme IEEE 1076.3 (Numeric Standart pour la synthèse). Implantation d ’un nombre signé

En 1995, afin de normaliser les méthodes de modélisation des retards des circuits ASIC ou FPGA, de grands industriels se sont associés, fournissant des bibliothèques normalisées. Ceci est concrétisé par la norme IEEE 1076.4

Récemment, le VHDL a connu une nouvelle extension avec la première norme IEEE-1076.1-1999 du langage de modélisation mixte et multi-technologique VHDL-AMS

2. Présentation des éléments du VHDL2.3. Historique

28/10/2014 11:18 R. EL ALAMI 6

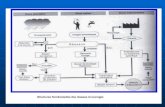

En VHDL, une structure logique est décrite à l'aide d'une entité et d'une architecture de la façon suivante :

2. Présentation des éléments du VHDL2.4. Structure d’une description VHDL

28/10/2014 11:18 R. EL ALAMI 7

2. Présentation des éléments du VHDL2.4. Structure d’une description VHDL

28/10/2014 11:18 R. EL ALAMI 8

Toute description VHDL utilisée pour la synthèse a besoin de bibliothèques. L’IEEE (Institut of Electrical and ElectronicsEngineers) les a normalisées et plus particulièrement la bibliothèque IEEE1164. Elles contiennent les définitions des types de signaux électroniques, des fonctions et sous programmes permettant de réaliser des opérations arithmétiques et logiques,...

La directive Use permet de sélectionner les bibliothèques à utiliser.

2.4. Structure d’une description VHDL2.4.1. Déclaration des bibliothèques

28/10/2014 11:18 R. EL ALAMI 9

Bloc AIn 1 Out 1

In 2In 3 Out 2

Vue externe : Définition de l'entité

Bloc B

Bloc D Bloc E

Bloc A

Out 1

Out 2

In 1

In 2

In 3

Bloc C

Vue interne : Définition de l'architecture

2.4. Structure d’une description VHDL2.4.2 Déclaration de l’entité (entity) et des entrées/sorties

28/10/2014 11:18 R. EL ALAMI 10

. Port : . Signal d ’interface entre l’entité et l’extérieur. Chaque port est associé à un nom, un mode et un type. Ordre de la déclaration des différents signaux : aucune importance. Ordre conservé lors d’une utilisation à un plus haut niveau de cette entité

- Instanciation d'un composant (component) . Mode :

. Définition du sens du signal

. VHDL interdit l’association de deux ports de mode contre nature

. 4 modes sont définis- in : Signal d’entrée monodirectionnel- out : Signal de sortie monodirectionnel- inout : Signal d’entrée/sortie bidirectionnel- buffer : Signal de sortie/entrée monodirectionnel

. Utile lorsqu’il y a rebouclage (sortie considérée comme une entrée)

. Peu utilisé (remplacé par une sortie associée à un signal interne)

2.4. Structure d’une description VHDL2.4.2 Déclaration de l’entité (entity) et des entrées/sorties

28/10/2014 11:18 R. EL ALAMI 11

. Mode : 4 modes de ports. Out

Erreur

MémoireDonnées

. Inout

R/W

Adresse

CS

. In

Busy

. Buffer

2.4. Structure d’une description VHDL2.4.2 Déclaration de l’entité (entity) et des entrées/sorties

28/10/2014 11:18 R. EL ALAMI 12

. Déclaration :

ENTITY nom_entite ISPORT ( entrees : IN type_entrees;

sorties : OUT type_sorties;entreessorties : INOUT type_entreessorties;entreessorties_buffer : BUFFER type_entreessorties_buffer)

END nom_entite;

2.4. Structure d’une description VHDL2.4.2 Déclaration de l’entité (entity) et des entrées/sorties

28/10/2014 11:18 R. EL ALAMI 13

2.4. Structure d’une description VHDL2.4.2 Déclaration de l’entité (entity) et des entrées/sorties

a) Le NOM_DU_SIGNAL.Il est composé de caractères, le premier caractère doit être une lettre, sa longueur est quelconque, mais elle ne doit pas dépasser une ligne de code. VHDL n’est pas sensible à la « casse », c’est à dire qu’il ne fait pas la distinction entre les majuscules et les minuscules.

28/10/2014 11:18 R. EL ALAMI 14

2.4. Structure d’une description VHDL2.4.2 Déclaration de l’entité (entity) et des entrées/sorties

b) Le SENS du signal

- in : pour un signal en entrée.- out : pour un signal en sortie.- inout : pour un signal en entrée sortie- buffer : pour un signal en sortie mais utilisé comme entrée dans la description.

28/10/2014 11:18 R. EL ALAMI 15

2.4. Structure d’une description VHDL2.4.2 Déclaration de l’entité (entity) et des entrées/sorties

c) Le TYPE

Le TYPE utilisé pour les signaux d’entrées / sorties est :- le std_logic pour un signal.- le std_logic_vector pour un bus composé de plusieurs signaux.

Par exemple un bus bidirectionnel de 5 bits s’écrira :

LATCH : inout std_logic_vector (4 downto 0) ;

Où LATCH(4) correspond au MSB et LATCH(0) correspond au LSB.Les valeurs que peuvent prendre un signal de type std_logic sont :

- ‘0’ ou ‘L’ : pour un niveau bas.- ‘1’ ou ‘H’ : pour un niveau haut.- ‘Z’ : pour état haute impédance.- ‘-‘ : Quelconque, c’est à dire n’importe quelle valeur.

28/10/2014 11:18 R. EL ALAMI 16

Exercices Exercice 1 : Définirl’entité décrivant unadditionneur de deux fois un bit.

Exercice 2 : Définirl’entité décrivant unadditionneur de deux mots de quatre bits.

17

ENTITY adder_pip ISPORT( clk : IN bit;

a,b : IN bit_vector(7 DOWNTO 0);cin : IN bit;s : OUT bit_vector(7 DOWNTO 0);cout : OUT bit)

END adder_pip;

. Exemple additionneur 8 bit:

2.4. Structure d’une description VHDL2.4.2 Déclaration de l’entité (entity) et des entrées/sorties

28/10/2014 11:18 R. EL ALAMI 18

. décrit le fonctionnement souhaité pour un circuit ou une partie du circuit.

. Plusieurs architectures peuvent être définies pour le même modèle

. Déclaration

ARCHITECTURE nomdelarchitecture OF nomdelentité ISdéclarations de procédures, de types, de constantes, de composants, de signaux

BEGINdéfiniton de processus

et/oud'instances de composants, ...

END nomdelarchitecture;

2.4. Structure d’une description VHDL2.4.3 Architecture

28/10/2014 11:18 R. EL ALAMI 19

ARCHITECTURE comportementale OF adder_pip ISBEGINPROCESS(clk)

VARIABLE carry : bit;VARIABLE sum : bit_vector (7 DOWNTO 0);

BEGINIF (CLK = '1') THEN

carry := cin; FOR i IN 0 TO a'length-1 LOOP

sum(i) := a(i) XOR b(i) XOR carry;carry := (a(i) AND b(i)) OR (a(i) AND carry) OR (b(i) AND carry);

END LOOP;cout <= carry;s <= sum;END IF;END PROCESS;

END comportementale;

. Exemples

2.4. Structure d’une description VHDL2.4.3 Architecture

28/10/2014 11:18 R. EL ALAMI 20

-- Décodeurs 7 segmentsentity DEC7SEG4 is

port (DEC :in std_logic_vector(3 downto 0);SEG:out std_logic_vector(6 downto 0));

end DEC7SEG4;architecture DESCRIPTION of DEC7SEG4 isbegin

SEG <= "1111110" when DEC = 0else "0110000" when DEC = 1else "1101101" when DEC = 2else "1111001" when DEC = 3else "0110011" when DEC = 4else "1011011" when DEC = 5else "1011111" when DEC = 6else "1110000" when DEC = 7else "1111111" when DEC = 8else "1111011" when DEC = 9else "-------";

end DESCRIPTION;

. Exemples

2.4. Structure d’une description VHDL2.4.3 Architecture

28/10/2014 11:18 R. EL ALAMI 21

. 3 Types de description :

. Description comportementale- Description purement fonctionnelle du circuit- Portabilité, lisibilité, maintenance, évolutivité- Description flot de données pour traduire une table de vérité

. Description structurelle- Traduction d’une représentation schématique- Efficacité, compacité, clarté

. Description mixte- Au sein d’une même architecture, il est possible d ’utiliser des modules décrits de manière comportementale ou structurelle

2.4. Structure d’une description VHDL2.4.3 Architecture

28/10/2014 11:18 R. EL ALAMI 22

ARCHITECTURE bas_niveau OF adder ISBEGIN

S(0) <= '1' WHEN A(0)!= B(0) ELSE '0';S(1) <= '1' WHEN ( A(0)!=B(0) AND A(1)!=B(1) OR

A(1)=B(1) AND A(0)=B(0)=1) ORA(1)!=B(1) AND A(0)=B(0)=0 ) ELSE '0';

END bas_niveau;

ARCHITECTURE niveau_equations_logiques OF adder ISBEGIN

S(0) <= A(0) XOR B(0);S(1) <= A(0) AND B(0) XOR A(1) XOR B(1);

END niveau_equations_logiques;

ARCHITECTURE haut_niveau OF adder ISBEGIN

S <= A + B;END haut_niveau;

. Description haut niveau

. Description niveau équations logiques

. Description bas niveau

2.4. Structure d’une description VHDLA. Architecture : Description comportementale

28/10/2014 11:18 R. EL ALAMI 23

. Exemple : Description comportementale d'une bascule D sur niveaux

HorlogeDQ

Q

HD Q

0

1

0

1

X X Q-1

2.4. Structure d’une description VHDLA. Architecture : Description comportementale

28/10/2014 11:18 R. EL ALAMI 24

LIBRARY ieee;USE ieee.std_logic_1164.all;USE ieee.std_logic_arith.all;

ENTITY basculed ISPORT( d,clk : IN bit;

q: OUT bit);END basculed;

ARCHITECTURE comportementale OF basculed ISBEGIN

PROCESS(clk)BEGINIF (clk='1') THEN q<=d;END IF;END PROCESS;

END comportementale;

. Exemple : Description comportementale d'une bascule D

2.4. Structure d’une description VHDLA. Architecture : Description comportementale

28/10/2014 11:18 R. EL ALAMI 25

. Traduction d'une représentation schématique

ARCHITECTURE structurelle OF adder ISCOMPONENT xor2

port(e1,e2 : in bit;s : out bit); end COMPONENT and2

port(e1,e2 : in bit;s : out bit); end COMPONENTSIGNAL inter1,inter2 :bit;BEGIN

u1 : PORT MAP xor2 (e1=>A(0),e2=>B(0),s=>S(0));u2 : PORT MAP xor2 (e1=>A(1),e2=>B(1),s=>inter1);u3 : PORT MAP and2 (e1=>A(0),e2=>B(0),s=>inter2);u4 : PORT MAP xor2 (e1=>inter1,e2=>inter2,s=>S(1));

end structurelle;

VHDLA(0)B(0)A(1)B(1)A(0)B(0)

S(1)

S(0)

2.4. Structure d’une description VHDLA. Architecture : Description structurelle

28/10/2014 11:18 R. EL ALAMI 26

. Au sein d'une même architecture, il est possible d'utiliser du comportemental et du structurel ENTITY integration IS PORT(

a : IN bit_vector(0 to 1);reset,clk : IN bit;s : OUT bit_vector(0 to 1));

END integrationARCHITECTURE mixte OF integration ISSIGNAL b,s_inter :bit_vector(0 to 1);COMPONENT adder

PORT(a,b : IN bit_vector(0 to 1);s : OUT bit_vector(0 to 1); END COMPONENT;

BEGINPROCESS(clk)

IF rising_edge(clk) THENIF reset = "1" THEN b <= '00';ELSE b <= s_inter;END IF;

END IF;END PROCESS;u1 : PORT MAP adder (a,b,s_inter);s <= s_inter;

END mixte;

VHDL

reset

Adder

D clk

sa

S_inter

b

2.4. Structure d’une description VHDLA. Architecture : Description mixte

28/10/2014 11:18 R. EL ALAMI 27

2.4. Structure d’une description VHDLExemple : un décodeur 1 parmi 4

28/10/2014 11:18 R. EL ALAMI 28

2.4. Structure d’une description VHDLExemple : un décodeur 1 parmi 4

28/10/2014 11:18 R. EL ALAMI 29

2.4. Structure d’une description VHDLExemple : Additionneur 1 bit

28/10/2014 11:18 R. EL ALAMI 30

2. Présentation des éléments du VHDL2.4. Structure d’une description VHDL

L'entité donne les informations concernant les signaux d'entrées et de sorties de la structure ainsi que leurs noms et leurs types.

L'architecture décrit le comportement de l'entité.

Il est possible de créer plusieurs architectures pour une même entité. Chacune de ces architectures décrira l'entité de façon différente.

28/10/2014 11:18 R. EL ALAMI 31

2.4. Structure d’une description VHDLExemple : description comportementale

28/10/2014 11:18 R. EL ALAMI 32

2.4. Structure d’une description VHDLExemple : description comportementale

Dans ce type de description, le comportement de la structure est directement inscrit dans l'architecture à l'aide d'instructions séquentielles ou sous forme de flot de données.

28/10/2014 11:18 R. EL ALAMI 33

2.4. Structure d’une description VHDLExemple : description structurelle

28/10/2014 11:18 R. EL ALAMI 34

2.4. Structure d’une description VHDLExemple : description structurelle

28/10/2014 11:18 R. EL ALAMI 35

3 types d’objets :

Constantes : valeur fixe après initialisation

Variables : valeur modifiable par affectation (affectation instantanée)

Signaux : spécifiques aux langages de description de matériel modélisent les informations qui circulent sur les fils ou bus

2. Présentation des éléments du VHDL2.5. Les Objets

28/10/2014 11:18 R. EL ALAMI 36

Constantes :

. Utilisation des constantes et des variables : proche des langages traditionnels

. Constantes (Constant). Objets internes à valeurs fixes et définitives. Synthèse : Mise à VCC ou au GND Surface nulle. Déclaration : constant nom : type := valeur;. Exemple :

CONSTANT pi : real:=3.141592 ;

2. Présentation des éléments du VHDL2.5. Les Objets

28/10/2014 11:18 R. EL ALAMI 37

Variables :

. Variables (Variable)

. Objets permettant de conserver une valeur pendant un certain temps

. Utilisable qu'au sein d'un processus (définition dans le process)

. Peu utilisé en synthèse logique

. Exemple:

VARIABLE octet1 : std_logic_vector(0 TO 7) := "00000001";

2. Présentation des éléments du VHDL2.5. Les Objets

28/10/2014 11:18 R. EL ALAMI 38

2. Présentation des éléments du VHDL2.5. Les ObjetsSignaux : (signal)• ils sont la base des langages de description de matériel• ils véhiculent les informations entre composants• ils ne sont pas de type pointeur, pas de type fichier• Utilisation en mode concurrent et séquentiel• Signaux internes, temporaires• Synthèse (représentation matérielle : un fil ou une mémoire)• Synthèse d'une VARIABLE ≠ Synthèse d'un SIGNAL• Une valeur courante et une valeur future

28/10/2014 11:18 R. EL ALAMI 39

ARCHITECTURE ex_sig OF exemple ISSIGNAL tmp : bit;BEGIN

PROCESS(a,b,c)BEGIN

tmp <= a and b;y <= tmp or c;

END PROCESS;END ex_sig;

Signaux : (signal). Synthèse d'une VARIABLE ≠ Synthèse d'un SIGNAL

ARCHITECTURE ex_sig OF exemple ISBEGIN

PROCESS(a,b,c)VARIABLE tmp : bit;BEGIN

tmp := a and b;y <= tmp or c;

END PROCESS;END ex_sig;

ab c

Tmp (fil)y

ab c

Tmp (fil)y

2. Présentation des éléments du VHDL2.5. Les Objets

28/10/2014 11:18 R. EL ALAMI 40

Affectation des signaux :VHDL permet de spécifier des délais dans les affectations.

2 modes de fonctionnement : mode inertiel :

• filtre les impulsions de longueur insuffisante mode transmission :

• transmission de toutes les impulsions

2. Présentation des éléments du VHDL2.5. Les Objets

28/10/2014 11:18 R. EL ALAMI 41

Mode inertielutiliser pour les composants dont le temps de traversé est non

nul (tous les composants décrits de façon réaliste)

2. Présentation des éléments du VHDL2.5. Les Objets

28/10/2014 11:18 R. EL ALAMI 42

Mode transport

toutes les transitions en entrée sont transmises en sortie avec un décalage égal au temps de propagation.

2. Présentation des éléments du VHDL2.5. Les Objets

28/10/2014 11:18 R. EL ALAMI 43

Mode inertiel vs mode transport

Le type inertiel permet de "filtrer" les variations de S trop courtes par rapport au délai de la transaction.

Par exemple si S est à 1 pendant 5 ns, l'affectation S1 <= S after10 ns; ne changera pas la forme d'onde de S1 qui restera à 0.

Contrairement au mode inertiel , le type transport n'opère pas de "réjection des parasites". Il respecte les temps de propagation.

2. Présentation des éléments du VHDL2.5. Les Objets

28/10/2014 11:18 R. EL ALAMI 44

Différences entre variables et signaux

Les variables sont toujours locales à un processus: il n’y a pas de variables globales

Les signaux peuvent être déclarés n’importe où dans le programme, sauf à l’intérieur d’un processus. S’ils sont déclarés au début de l’architecture, ils sont communs à toute l’architecture

Contrairement aux signaux, les variables sont mises à jour de façon instantanée, au moment de l’affectation, sans retard possible

2. Présentation des éléments du VHDL2.5. Les Objets

28/10/2014 11:18 R. EL ALAMI 45

Le VHDL est un langage fortement typé. Chaque objet doit être déclaré et appartenir à un type connu (ensemble de valeurs possibles). Type = ensemble de valeurs + opérateurs associés Sous-type = type dérivé d'un type de base (type parent) avec

contraintes 4 classes de types

Types scalaires: entier, réel, énuméré, physique Types composites: tableaux, enregistrements Pointeurs Fichiers

Déclaration de type:

Déclaration de sous-type:

2. Présentation des éléments du VHDL2.6. Types et sous-types

28/10/2014 11:18 R. EL ALAMI 46

2. Présentation des éléments du VHDL2.6. Types et sous-types

28/10/2014 11:18 R. EL ALAMI 47

. Types entiers : -231 + 1 ≤ entier ≤ 231 - 1

. Types flottants :

Approximation discrète de l'ensemble des réels dans un intervalle donné

-1E38 ≤ Flottant ≤ 1E38Opérateurs

• Arithmétiques: + – * / absmod rem (seulement pour types entiers)** (puissance entière)• Relationnels: = /= < <= > >=

TYPE chiffre_ascendant IS RANGE 0 TO 9;TYPE chiffre_descendant IS RANGE 9 DOWNTO 0;

TYPE tension IS RANGE 0 TO 5;

2. Présentation des éléments du VHDL2.6.1 Types : scalaire

28/10/2014 11:18 R. EL ALAMI 48

2. Présentation des éléments du VHDL2.6.1 Types : scalaire. Types énumérés :

Ensemble de valeurs désignées par des identificateurs ou des caractères

TYPE boolean IS (false, true);

TYPE bit IS ('0','1');

TYPE std_logic IS ('U', ’X', ’O', ’1' ’Z', ’W', ’L', ’H' , ’-');

TYPE jour IS (lundi, mardi, mercredi, jeudi, vendredi, samedi, dimanche);Remarques :

. Chaque caractère ou chaîne de caractères au sein d'un même type doit être distinct

. Possibilité d'utiliser le même caractère dans 2 types distinctsOpérateurs

• Relationnels: = /= < <= > >=• Logiques: and or nand nor xor xnor not (types bit & boolean seulement)

28/10/2014 11:18 R. EL ALAMI 49

2. Présentation des éléments du VHDL2.6.1 Types : scalaire. Types physiques :

Valeurs numériques de quantités physiques

TYPE resistance IS RANGE 0 TO 1E8;UNITS ohms;

kohms = 1000 ohms;Mohms = 1E6 ohms;

END UNITS;

un type physique est caractérisé par : son unité par des sous unités on peut effectuer des calculs sur ces types

♦ Opérateurs• Arithmétiques: + – * / abs• Relationnels: = /= < <= > >=

28/10/2014 11:18 R. EL ALAMI 50

2. Présentation des éléments du VHDL2.6.2 Types : composés

Tableaux et enregistrements (array & record) : tableau : éléments homogènes, de même type enregistrements : éléments hétérogènes, types différents

Les tableaux : dimensions multiples les indices sont de type discret (énuméré ou entier) 2 sortes de tableaux :

• contraint : on spécifie le sens de variation des indices• non contraint : on repousse la définition de la taille à plus tard

28/10/2014 11:18 R. EL ALAMI 51

2. Présentation des éléments du VHDL2.6.2.1 Type : tableauxExemples de types non prédéfinistype word is array (31 downto 0) of bit; -- intervalle descendanttype memory is array (0 to 255) of word; -- intervalle montanttype truth_table is array (bit, bit) of bit;L'indice peut-être un type entier défini par déclarationTYPE adresse IS RANGE 0 TO 255;type memory is array (adresse) of octet;

Accès aux éléments d'un tableau-- soit W un objet de type word, M de type memory, et TT de type truth_tableW(15) --bit d'indice 15M(122) --mot d'indice 122M(122)(8) -- bit d'indice 8 du mot d'indice 122TT(’0’, ’1’) -- bit à la ligne 1 et colonne 2-- tranchesW(31 downto 16) -- 16 bits les plus significatifsM(129 to 255) -- portion haute de la mémoire

28/10/2014 11:18 R. EL ALAMI 52

Les tableaux non contraint : permet de repousser la définition de la taille à plus tard. la manipulation de ces tableaux demande l’utilisation d’attributs

range <>

Types prédéfinis

type bit_vector is array (natural range <>) of bit;type string is array (positive range <>) of character;

2. Présentation des éléments du VHDL2.6.2.1 Type : tableaux

28/10/2014 11:18 R. EL ALAMI 53

♦ Opérateurs

• Relationnels: = /= < <= > >=• Logiques*: and or nand nor xor xnor not• Décalage et rotation*: sll srl sla sra rol ror

(* tableaux à 1 dimension de types bit ou boolean seulement;opérations logiques effectuées bit à bit)

• Concaténation: & (tableaux à 1 dimension seulement)

2. Présentation des éléments du VHDL2.6.2.1 Type : tableaux

28/10/2014 11:18 R. EL ALAMI 54

2. Présentation des éléments du VHDL2.6.2 Types : composés

Un type enregistrement définit une collection d'éléments (ou de champs) nommés dont les valeurs peuvent être de types différents. Chaque nom d'élément doit être unique.♦ Exemples de types non prédéfinis

♦ Accès aux éléments d'un enregistrement

type memory_bus is recordaddr : bit_vector(15 downto 0);data : bit_vector(7 downto 0);read, write: bit;enable : boolean;

end record memory_bus;type complex is record

real_part, imag_part: real;end record complex;

-- soit MB1 et MB2 deux objets de type memory_bus et Z de type complexMB1.addr -- tout le tableau addrMB1.addr(7 downto 0) -- tranche du tableau addrMB1.data(7) -- élément d'indice 7 du tableau addrZ.real_part, Z.imag_part -- nombres réelsAffectation par champs ou globaleMB1:=MB2MB1.addr:=MB2.addr

28/10/2014 11:18 R. EL ALAMI 55

2. Présentation des éléments du VHDL2.6.3 Types : Accès Allocation dynamique de mémoire Pointeur sur un objet de type prédéfini Instructions :

new deallocate

Exemple :

type article is recordchamps1 : integer;champs2 : bit;

end record;type pointeur is access article;variable p, q : pointeur;p:= new pointeur ;

28/10/2014 11:18 R. EL ALAMI 56

2. Présentation des éléments du VHDL2.6.4 Types : FichierLes fichiers (FILE) sont très utilisés pour stocker des données telles que Mémoires ROM, Données de test.♦ Type prédéfini (dans paquetage TEXTIO)

L'usage du paquetage TEXTIO requiert la déclaration de la clause use suivante:

use STD.TEXTIO.all;

♦ Exemples de types non prédéfinis

type text is file of string ;

type word is bit_vector(7 downto 0);type word_file is file of word;type real_file is file of real;

28/10/2014 11:18 R. EL ALAMI 57

2. Présentation des éléments du VHDL2.6.4 Sous-TypesUn sous-type reste compatible avec son type d’origine contrairement à un type nouvellement créé.

SUBTYPE narurel IS integer RANGE 0 TO integer’high

naturel reste compatible avec integer

TYPE nouvel_entier IS RANGE 0 TO 99

nouvel_entier est un type différent

28/10/2014 11:18 R. EL ALAMI 58

Time

Prédéfinis

Integer bit Boolean Real

Natural Positive Bit-vector

2. Présentation des éléments du VHDL2.6.5 Types prédéfinis

28/10/2014 11:18 R. EL ALAMI 59

. Remarque : Le VHDL est un langage développé initialement pour lamodélisation et la simulation, par conséquent certains opérateurs sont à déconseiller en synthèse

. Opérateurs logiques

AndNandOrNorXorXnorNot

EtNon et

OuNon ou

Ou exculsifEgalNon

SignificationNom Type opérandes

BooleanBit ou Bit_vector

2. Présentation des éléments du VHDL2.7 Opérateurs standards

28/10/2014 11:18 R. EL ALAMI 60

. Opérateurs logiques

gd

fe

c(0)a(0)b(0)

c(1)a(1)b(1)

. Exemple 2

SIGNAL d, e, f, g : bit;g <= (d AND e) AND f; Synthèse

SIGNAL a,b,c : bit_vector(0 TO 1);c <= a AND b; Synthèse

. Exemple 1

2. Présentation des éléments du VHDL2.7 Opérateurs standards

28/10/2014 11:18 R. EL ALAMI 61

. Opérateurs relationnels

=/=<<=>>=

EgalNon égalInférieur

Inférieur ou égalSupérieur

Supérieur ou égal

SignificationNom Type opérandes

Entrées : Tout scalaireSortie : Boolean

. Exemple

SIGNAL a,b : bit_vector(1 DOWNTO 0);SIGNAL s : bit;

IF a > b THEN s <= "1";END IF;

Synthèse

a0

!b0

a1

a0

!b0

!b1

a1

!b1

s

2. Présentation des éléments du VHDL2.7 Opérateurs standards

Ils permettent de modifier l’état d’un signal ou de signaux suivant le résultat d’un test ou d’une condition

28/10/2014 11:18 R. EL ALAMI 62

. Opérateurs de décalages

Sll Sla

Srl Sra

Rol

Ror

Décalage à gauche

Décalage à droite

Rotation gauche

Rotation à droite

SignificationNom Type opérandes

Bit_vector

SIGNAL a,b : BIT_VECTOR(0 TO 3);...

b <= a sll 1; --b = a décalé de 1 bit à gauche...

Synthèse

a0

a1 b0

a2 b1

a3 b2

'0' b3

clk

. Exemple

2. Présentation des éléments du VHDL2.7 Opérateurs standards

28/10/2014 11:18 R. EL ALAMI 63

Opérateurs arithmétiques

Autres opérateurs

& ConcaténationSignificationNom Type opérandes

Bit, Bit_vector

+-*/

abs**

Incrémentation de 1 ou additionDécrémentaion de 1 ou soustraction

MultiplicationDivision

Valeur absolueExponentiel

SignificationNom Type opérandes

Integer, Real

rem Restemod ModuloInteger

2. Présentation des éléments du VHDL2.7 Opérateurs standards

28/10/2014 11:18 R. EL ALAMI 64

. Exemple : addition

S = (A + B) + (C - 1)T = ((A + B) + C - 1)

Synthèse - 1

A

BC

S

- 1

A

BC

T

2. Présentation des éléments du VHDL2.7 Opérateurs standards

Remarque : Pour pouvoir utiliser les opérateurs ci-dessus il faut rajouter les bibliothèques suivantes au début du fichier VHDL:

Use ieee.numeric_std.all ;Use ieee.std_logic_arith.all ;

28/10/2014 11:18 R. EL ALAMI 65

. Opérateur de concaténation

& ConcaténationSignificationNom Type opérandes

Bit, Bit_vector

ARCHITETCURE ...SIGNAL A : BIT_VECTOR(2 DOWNTO 0 );SIGNAL B : BIT;SIGNAL C : BIT_VECTOR(5 DOWNTO 0 );

BEGINC <= not B & "101" & not A(2 DOWNTO 1);

A(1) C(0)

A(2) C(1)

VDD C(2)GND C(3)VDD C(4)

B C(5)

2. Présentation des éléments du VHDL2.7 Opérateurs standards

« bon » & « jour » produira « bonjour » ; « 101 » & « 10 » produira « 10110 »

28/10/2014 11:18 R. EL ALAMI 66

. Opérateur de concaténation

2. Présentation des éléments du VHDL2.7 Opérateurs standards

Utilisation de l’opérateur de concaténation pour réaliser des décalages logiques en synthèse logique :

Décalage à droite :

-- Si A est de type std_logic_vector(7 downto 0)S1 <= ‘0’ & A(7 downto 1); -- décalage d’un bit à droiteS1 <= "000" & A(7 downto 3); -- décalage de trois bits à droite

Décalage à gauche :

-- Si A est de type std_logic_vector(7 downto 0)S1 <= A(6 downto 0) & ‘0’; -- décalage d’un bit à gaucheS1 <= A(4 downto 0) & "000" ; -- décalage de trois bits à gauche

28/10/2014 11:18 R. EL ALAMI 67

• L’affectation simple : <=

2. Présentation des éléments du VHDL2.7 Opérateurs standards

Dans une description VHDL, c’est certainement l’opérateur le plus utilisé. Permet de modifier l’état d’un signal en fonction d’autres signaux et/ou

d’autres opérateurs.

Exemple avec des portes logiques : S1 <= E2 and E1 ;

Pour les signaux composés de plusieurs bits on utilise les guillemets " … "

Les bases numériques utilisées pour les bus peuvent être :

BINAIRE, exemple : BUS <= "1001" ; -- BUS = 9 en décimalHEXA, exemple : BUS <= X"9" ; -- BUS = 9 en décimalOCTAL, exemple : BUS <= O"11" ; -- BUS = 9 en décimal

Remarque : La base décimale ne peut pas être utilisée lors de l’affectation de signaux.

28/10/2014 11:18 R. EL ALAMI 68

2. Présentation des éléments du VHDL2.7 Opérateurs standards

Exemple:Library ieee;Use ieee.std_logic_1164.all;entity AFFEC isport (

E1,E2 : in std_logic;BUS1,BUS2,BUS3 : out std_logic_vector(3 downto 0);S1,S2,S3,S4 : out std_logic)

end AFFEC;architecture DESCRIPTION of AFFEC isbegin

S1 <= '1'; -- S1 = 1S2 <= '0'; -- S2 = 0S3 <= E1; -- S3 = E1S4 <= '1' when (E2 ='1') else ‘S4'; -- S4 = 1 si E1=1 sinon S4BUS1 <= "1000"; -- BUS1 = "1000"BUS2 <= E1 & E2 & "10"; -- BUS2 = E1 & E2 & 10BUS3 <= x"A"; -- valeur en HEXA -> BUS3 = 10(déc)

end DESCRIPTION;

28/10/2014 11:18 R. EL ALAMI 69

2. Présentation des éléments du VHDL2.8 Attributs

28/10/2014 11:18 R. EL ALAMI 70

Un attribut est une caractéristique associée à un type ou un objet. Chaque attribut est référencé par son nom consistant en un préfixe, une apostrophe et l´attribut lui-même. Le préfixe doit être un type, sous-type, tableau, ou bloc.

Attribut = information sur un élément du langageUtilisation : toto'att avec toto un objet ou un type et att un attribut

• Par exemple: longueur d'un signal bus = bus'length

ils permettent de connaître les caractéristiques : des signaux des tableaux des types

. Attributs d'un scalaireT'left -> Limite gauche de TT'right -> Limite droite de TT'low -> Limite basse de TT'high -> Limite haute de T

. Attributs d'un ensemble discret

T'pos(X) -> Numéro de la position de X dans TT'val(N) -> Valeur à la position N dans TT'leftof(X) -> Valeur à une position à gauche de X dans TT'rightof(X) -> Valeur à une position à droite de X dans TT'pred(X) -> Valeur à une position au dessous de X dans TT'succ(X) -> Valeur à une position au dessus de X dans T

28/10/2014 11:18 R. EL ALAMI 71

2. Présentation des éléments du VHDL2.8 Attributs

. Exemples - Attributs d'un scalaireType adr is integer range 7 downto 0;

adr ’left = 7adr ’right = 0adr ’low = 0adr ’high = 7

. Exemples - Attributs d'un ensemble discretType MVL4 is (‘ U ’, ’0 ’, ‘ 1 ’, ‘ Z ’);

MVL4'pos(‘ 1 ’) = 2MVL4'val(0) = ‘ U ’MVL4 ’rightof(‘ 1 ’) = ‘ Z ’MVL4 ’leftof(‘ 1 ’) = ‘ 0 ’MVL4 ’succ(2) = ‘ Z ’ MVL4 ’succ(‘1’) = ‘ Z ’ MVL4 ’prec(2) = ‘ 0 ’

28/10/2014 11:18 R. EL ALAMI 72

2. Présentation des éléments du VHDL2.8 Attributs

. Attributs d'un tableau

A'left(N) -> Limite gauche de l'intervalle des indices de la dim. N de AA'right(N) -> Limite droite de l'intervalle des indices de la dim. N de AA'low(N) -> Limite basse de l'intervalle des indices de la dim. N de AA'highof(N) -> Limite haute de l'intervalle des indices de la dim. N de AA'range(N) -> Intervalle des indices de la dim. N de AA'reverse_range(N) -> Intervalle inverse des indices de la dim. N de AA'length(N) -> Longueur de l'intervalle des indices de la dim. N de A

28/10/2014 11:18 R. EL ALAMI 73

2. Présentation des éléments du VHDL2.8 Attributs

. Exemples : Attributs d'un tableautype word is bit_vector(31 downto 0);type memory is array(7 downto 0) of word;variable mem : memory;

mem'left = 7mem'left(3) = 31mem'right = 0mem'low = 0mem'high = 7mem ’high(5) = 31mem'range = 7 downto 0mem ’range(3) = 31 downto 0mem'reverse_range = 0 to 7mem'length = 8mem ’length(3) = 32

28/10/2014 11:18 R. EL ALAMI 74

2. Présentation des éléments du VHDL2.8 Attributs

Attributs de signalPour cette catégorie d’attribut, le préfixe doit être un signal. Le type du résultat peut être signal ou fonction.

• Objets signaux implicites:S'delayed (T) Signal ayant même valeur que S mais retardé de

T unités de temps (T ≥ 0 ns)S'stable(T) Signal de type boolean valant TRUE si aucun

événement n'est arrivé sur S durant T unités de temps (T ≥ 0 ns), et FALSE sinon

• Fonctions:S'event Fonction à valeur de type boolean valant TRUE

si un événement est arrivé sur S durant le cycle de simulation courant, et FALSE sinon

S'last_event Fonction à valeur de type time valant le tempsécoulé depuis le dernier événement sur S

S'last_value Fonction à valeur du type de S valant la valeur de S avant le dernier événement sur S

28/10/2014 11:18 R. EL ALAMI 75

2. Présentation des éléments du VHDL2.8 Attributs

Attributs de signal

S’active :• boolean• true si il y a eu une transaction (affectation) sur le signal dans le cycle de simulation en cours

S’quiet(T) :• boolean• true si le signal a eu ni transaction ni événement pendant un temps T

S’transaction :• signal• c’est un signal de type bit qui change d’états pour chaque transaction du signal

S’last_active :• time• rend le temps écoulé depuis la dernière transaction

28/10/2014 11:18 R. EL ALAMI 76

2. Présentation des éléments du VHDL2.8 Attributs

Utilisation des attributs de signaux : détection d'un front montant :

détection d'un front descendant :

28/10/2014 11:18 R. EL ALAMI 77

2. Présentation des éléments du VHDL2.8 Attributs

. Exécution parallèle . Exécution par défaut . Les instructions au sein d'une architecture sont exécutées en parallèle ou de

manière concurrente. Exécution concurrente = Exécution combinatoire. Chaque opération dans une architecture est exécutée à chaque instant

. Exécution séquentielle. Nécessité d'utiliser un PROCESS. Le process est exécuté à chaque fois qu'un signal déclaré dans sa liste de sensibilité change de valeur.

. Les instructions sont exécutées séquentiellement

. Les modifications des signaux (signal) sont effectives à la fin du process

. Particularisme du VHDL : Exécution parallèle ou séquentielle

2. Présentation des éléments du VHDL2.9 Exécution parallèle et séquentielle

28/10/2014 11:18 R. EL ALAMI 78

. Exécution mixte. Possibilité d'associer dans une même architecture des modules à exécution parallèle et séquentielle. Exemple : Comparateur synchrone à une horloge clk

LIBRARY ieee;USE ieee.std_logic_1164.all;ENTITY comp_synch IS PORT (

a, b, clk, reset : IN std_logic;qs : OUT std_logic);

END comp_synch;ARCHITECTURE archi_mixte OF comp_synch ISSIGNAL q : std_logic;BEGIN

q<='1‘ WHEN a=b ELSE '0';PROCESS(clk, reset)BEGIN

IF reset='0' THEN qs<='0';ELSIF (clk'event AND clk='1') THEN qs <= q;END IF;

END PROCESS;END archi_mixte;

ab clk

Reset

qsq

Comparateur

2. Présentation des éléments du VHDL2.9 Exécution parallèle et séquentielle

28/10/2014 11:18 R. EL ALAMI 79

. Deux types d'exécution : Deux familles d'instructions

. Instructions réservées au mode d'exécution parallèle ou concurrente- Toutes les opérations sont exécutées simultanément- L'ordre d'écriture n'a aucune importance

I1 I2 I3I1

I2

I3. Instructions réservées au mode d'exécution séquentielle- Chaque opération est effectuée l'une après l'autre- L'ordre d'écriture a une grande importance

2. Présentation des éléments du VHDL2.10 Instructions

28/10/2014 11:18 R. EL ALAMI 80

. Assignation inconditionnellesignal <= expression

. Assignation conditionnellesignal <= {expression WHEN condition} ELSE expression

ARCHITECTURE flot_de_donnees OF xor ISBEGIN

c <= '0' WHEN a = '0' AND b = '0' ELSE'1' WHEN a = '0' AND b = '1' ELSE'1' WHEN a = '1' AND b = '0' ELSE'0' WHEN a = '1' AND b = '1' ELSE'0';

END flot_de_donnees;

2.10 Instructions2.10.1 Instructions de type parallèle

28/10/2014 11:18 R. EL ALAMI 81

. Assignation sélective

WITH sélecteur SELECTsignal <= {expression WHEN valeur_sélecteur1,

expression WHEN valeur_sélecteur2, expression WHEN OTHERS};

ARCHITECTURE flot_de_donnees OF mux ISSIGNAL selection : std_logic_vector(0 TO 1);SIGNAL a,b,c,d,s : std_logic_vector(0 TO 7);BEGIN

WITH selection SELECTs <= a WHEN "00",

b WHEN "01",c WHEN "10",d WHEN OTHERS;

END flot_de_donnees;

2.10 Instructions2.10.1 Instructions de type parallèle

28/10/2014 11:18 R. EL ALAMI 82

. Assignation d'un composantlabel : nom_du_composant PORT MAP (association des ports)

ARCHITECTURE arch_full OF full_adder ISSIGNAL inter : bit;COMPONENT half_adder PORT (a,b,cin : IN bit;

cout,s : OUT bit);END COMPONENT;BEGIN

u1 : half_adder PORT MAP (a=>a(0),b=>b(0),cin=>cin,cout=>inter,s=>s(0));u2 : half_adder PORT MAP (a(1),b(1),inter,cout,s(1));

END arch_full;

2.10 Instructions2.10.1 Instructions de type parallèle

28/10/2014 11:18 R. EL ALAMI 83

Instanciation de multiples composants. Instruction GENERATE

label : FOR variable_boucle IN val_initiale TO val_finale GENERATE{instructions parallèles}END GENERATE label

label : IF condition GENERATE{instructions parallèles}END GENERATE label

2.10 Instructions2.10.1 Instructions de type parallèle

28/10/2014 11:18 R. EL ALAMI 84

Notez que :• le ELSE n'existe pas (oubli de VHDL ?) et qu'il faut refaire un 2ème IF.

• Les deux instructions IF GENERATE et FOR GENERATE ont besoin obligatoirement d'une étiquette

. Instruction PROCESS

- Un processus est un ensemble de phrases séquentielles- Un modèle VHDL peut être vu comme un ensemble de processusexécutés en parallèle- Toutes les instructions comprises dans le PROCESS sont exécutées séquentiellement- Tous les PROCESS sont exécutés en parallèle- Les signaux sont utilisés pour contrôler l’activation des processus- Activation d'un PROCESS : 2 possibilités

[label] : PROCESS(liste_signaux)-- Partie déclarative du process

BEGIN-- Corps du process-- phrases séquentielles

END PROCESS [label]

[label] : PROCESS-- Partie déclarative du process

BEGIN-- Corps du process-- phrases séquentiellesWAIT ON (liste_signaux)

END PROCESS [label]

2.10 Instructions2.10.2 Instructions de type séquentiel

28/10/2014 11:18 R. EL ALAMI 85

. Instruction PROCESS

Phrases wait:wait on A, B; -- changement de A ou Bwait for délai; -- une certaine duréewait until condition;wait on ListeDeSignaux until condition

N.B : L'instruction WAIT n'est pas synthétisable avec la condition de durée. Elle est très utile pour les testbench pour la simulation.

2.10 Instructions2.10.2 Instructions de type séquentiel

28/10/2014 11:18 R. EL ALAMI 86

Exemple avec des variables:entity toto isend toto;architecture var of toto is

signal trigger, sum : integer := 0;begin

processvariable var1 : integer := 1;variable var2 : integer := 2;variable var3 : integer := 3;begin

wait on trigger;var1 := var2 + var3;var2 := var1;var3 := var2;sum <= var1 + var2 + var3;

end process;end var;

Si trigger change à t=10, alors var1=5, var2=5, var3=5 et à t=10+D, sum=15

2.10 Instructions2.10.2 Instructions de type séquentiel

28/10/2014 11:18 R. EL ALAMI 87

Exemple avec des signaux:entity toto isend toto;architecture var of toto is

signal trigger, sum : integer := 0;signal sig1 : integer := 1;signal sig2 : integer := 2;signal sig3 : integer := 3;

beginprocess

beginwait on trigger;sig1 <= sig2 + sig3;sig2 <= sig1;sig3 <= sig2;sum <= sig1 + sig2 + sig3;

end process;end var;

Si trigger change à t=10, tous les signaux sont mis à jour à t=10+D : sig1=5, sig2=1, sig3=2 et sum=6

2.10 Instructions2.10.2 Instructions de type séquentiel

28/10/2014 11:18 R. EL ALAMI 88

Un port de sortie ne peut être utilisé que comme destination d’une expression. Exemple:

entity nonet isport (a, b : in bit;

z, zbarre : out bit);end nonet;architecture fausse of nonet isbegin

z <= a and b;zbarre <= not z;

end fausse;architecture correcte of nonet is

signal resultat : bit;beginresultat <= a and b;z <= resultat;zbarre <= not resultat;

end correcte;

2.10 Instructions2.10.2 Instructions de type séquentiel

28/10/2014 11:18 R. EL ALAMI 89

. Instruction PROCESS : Attribut event

. But : Savoir si le signal auquel il est associé a été modifié

. Très utile dans un PROCESS déclenchable par plusieurs signaux distincts

. Exemples :

IF CLK'event THEN exécution; END IF; - Exécution si CLK passe à 0 ou à 1 IF CLK'event AND CLK='1' THEN exécution; END IF; - Déclenchement sur front montant

2.10 Instructions2.10.2 Instructions de type séquentiel

28/10/2014 11:18 R. EL ALAMI 90

. Ces instructions sont uniquement utilisées dans un Process. Assignation inconditionnelle de variables et de signaux

Même traitement que pour le mode parallèle

. Instruction IFIF condition THEN

instructions_sequentiellesELSIF condition THEN

instructions_sequentiellesELSE instructions_sequentiellesEND IF;

IF up_down = "1" THENs <= s + 1;

ELSEs <= s - 1;

END IF;

SIGNAL sig : integer;PROCESS(clk)

VARIABLE var : integer := 0;BEGIN

sig <= sig + 1;var := var + 1;

END PROCESS;

2.10 Instructions2.10.2 Instructions de type séquentiel

28/10/2014 11:18 R. EL ALAMI 91

. Instruction CASECASE expresssion is

{WHEN valeur_expression => instructions_sequentielles};{WHEN OTHERS => instructions_sequentielles};

END CASE;CASE selection IS

WHEN '0' => s <= a;WHEN '1' => s <= b;WHEN OTHERS => NULL;

END CASE;. Instruction LOOPinstruction_pour_iteration LOOP

instructions_sequentiellesEND LOOP;

VARIABLE indice,resultat : INTEGER := 0;Boucle1 : WHILE indice < 10 LOOP

indice := indice + 1;resultat := resultat + adresse(indice);

END LOOP boucle1;

VARIABLE indice,resultat : INTEGER;Boucle2 : FOR indice IN 0 TO 9 LOOP

resultat := resultat + adresse(indice);END LOOP boucle2;

2.10 Instructions2.10.2 Instructions de type séquentiel

28/10/2014 11:18 R. EL ALAMI 92

. Instruction NEXTNEXT label_boucle WHEN condition

VARIABLE indice,resultat : integer := 0;Boucle1 : WHILE indice < 10 LOOP

indice := indice + 1;NEXT boucle1 WHEN indice = 5;resultat := resultat + adresse(indice);

END LOOP boucle1;

VARIABLE indice,resultat : integer;Boucle2 : FOR indice IN 0 TO 9 LOOP

NEXT boucle2 WHEN indice = 5; resultat := resultat + adresse(indice);

END LOOP boucle2;

. Instruction EXITEXIT label_boucle WHEN condition

VARIABLE indice,resultat : integer := 0;Boucle1 : WHILE indice < 10 loop

indice := indice + 1;EXIT boucle1 WHEN indice = 5;resultat := resultat + adresse(indice);

END LOOP boucle1;

VARIABLE indice,resultat : integer;Boucle2 : FOR indice IN 0 to 9 LOOP

EXIT boucle2 WHEN indice = 5; resultat := resultat + adresse(indice);

END LOOP boucle2;

2.10 Instructions2.10.2 Instructions de type séquentiel

28/10/2014 11:18 R. EL ALAMI 93

. Instruction NULLInstruction sans aucun effet

CASE commande_moteur ISWHEN avant => marche_avant;WHEN arriere => marche_arriere;WHEN statuquo => NULL;

END CASE;

. Instruction ASSERTVérification d'une condition spécifiqueInformation d'une éventuelle violation de cette conditionASSERT condition REPORT message SEVERITY {note/warning/error/Failure}

PROCESS(clk) BEGIN IF clk='1' THEN

ASSERT d'STABLE(15 ns);REPORT "setup non respecté" SEVERITY warning;…END IF;

END PROCESS;

2.10 Instructions2.10.2 Instructions de type séquentiel

28/10/2014 11:18 R. EL ALAMI 94

. Multiplexeur 8 bits : 4 vers 11ère phase : définition des entrée/sorties (ENTITY)

Multiplexeur 8 bits4 vers 1 SortiesEntrées

Multiplexeur 8 bits4 vers 1

8Entree1

8Entree4

Sel1 Sel2

8Sortie

8Entree2

8Entree3

2.10 Instructions2.10.3 Exemples

28/10/2014 11:18 R. EL ALAMI 95

. Multiplexeur 8 bits : 4 vers 1

2ème phase : définition du fonctionnement ou de la structure (ARCHITECTURE)

- Solution 1 : Instruction IF

- Solution 2 : Instruction CASE

2.10 Instructions2.10.3 Exemples

28/10/2014 11:18 R. EL ALAMI 96

. Multiplexeur 8 bits : 4 vers 1

- Solution 1 : Instruction IF

LIBRARY ieee;USE ieee.std_logic_1164.all;ENTITY mux41 IS

PORT(entree1,entree2,entree3,entree4: IN std_logic_vector(0 TO 7);sel: IN std_logic_vector(0 to 1);sortie : OUT std_logic_vector(7 DOWNTO 0));

END mux41;ARCHITECTURE comportementale OF mux41 ISBEGIN

PROCESS(sel)BEGIN

IF (sel="00") THEN sortie<=entree1;ELSE IF (sel="01") THEN sortie<=entree2;END IF;ELSE IF (sel="10") THEN sortie<=entree3;END IF;ELSE sortie<=entree4;END IF;

END PROCESS;END comportemental;

2.10 Instructions2.10.3 Exemples

28/10/2014 11:18 R. EL ALAMI 97

. Multiplexeur 8 bits : 4 vers 1

- Solution 2 : Instruction CASE

LIBRARY ieee;USE ieee.std_logic_1164.all;ENTITY mux41 IS

PORT(entree1,entree2,entree3,entree4: IN std_logic_vector(0 TO 7);sel: IN std_logic_vector(0 to 1);sortie : OUT std_logic_vector(7 DOWNTO 0));

END mux41;ARCHITECTURE comportementale OF mux41 ISBEGIN

PROCESS(sel)BEGINCASE sel IS

WHEN "00" => sortie<=entree1;WHEN "01" => sortie<=entree2;WHEN "10" => sortie<=entree3;WHEN OTHERS => sortie<=entree4;

END CASE;END PROCESS

END comportementale;

2.10 Instructions2.10.3 Exemples

28/10/2014 11:18 R. EL ALAMI 98

. Descriptions plus simples

. Rapidité de simulation et donc rapidité de mise au point

. Réutilisation de sous-ensembles

. Concepts : COMPONENT, GENERIC, PACKAGE, PROCEDURE ET FONCTIONLIBRARY, CONFIGURATION

. Utilisation d'un objet décrit à l'extérieur de la description utilisatrice :- 2 fichiers VHDL distincts

. Compilation distincte :- le composant- l'entité utilisatrice de ce composant

. Entité compilée : Stockage dans la bibliothèque WORK

2. Présentation des éléments du VHDL2.11 Description hiérarchique

28/10/2014 11:18 R. EL ALAMI 99

. Description structurelle

. Utilisation de composants2 phases : - Déclaration

- Instanciation

2.11 Description hiérarchique2.11.1 Description hiérarchique : Component

28/10/2014 11:18 R. EL ALAMI 100

DéclarationLa syntaxe est presque identique à celle de l'entité :

component AND_2port (

a : in bit;b : in bit;s : out bit);

end component;

2.11 Description hiérarchique2.11.1 Description hiérarchique : Component

28/10/2014 11:18 R. EL ALAMI 101

Instanciation :L'instanciation d'un composant se fait dans le corps de l'architecture de cette façon :NOM_INSTANCE : NOM_COMPOSANT port map (LISTE DES CONNEXIONS);

entity AND_3 isport(

e1 : in bit;e2 : in bit;e3 : in bit;s : out bit);

end entity;

architecture arc of AND_3 issignal z : bit;component and2port (

a : bit;b : bit;s : bit);

end component;begin

inst1 : and2 port map (a=>e1, b=>e2 , s=>z);inst2 : and2 port map (z, e3, s);

end arc

2.11 Description hiérarchique2.11.1 Description hiérarchique : Component

28/10/2014 11:18 R. EL ALAMI 102

Dans cet exemple , 2 instances de composant "and2" sont appelées pour créer une porte ET à 3 entrées.

L'association des ports du composants aux signaux de l'instance se fait à l'aide de la clause port map.

La syntaxe des associations est soit :

par nom où chaque broche du composant est associée à un signal : cas de inst_1

positionnelle où l'ordre des signaux correspond à l'ordre des broches : cas de inst_2

Exemple additionneur

Adder1.vhd

ENTITY full_adder ISPORT(

a,b : IN bit_vector(1 DOWNTO 0);cin : IN bit;cout : OUT bit;s : out bit_vector(1 DOWNTO 0));

END full_adder

ARCHITECTURE arch_full OF full_adder ISSIGNAL inter : bit;COMPONENT half_adder PORT (a,b,cin : IN bit;

cout,s : OUT bit);END COMPONENT;BEGIN

u1:half_adder PORT MAP(a(0),b(0),cin,inter,s(0));

u2:half_adder PORT MAP (a(1),b(1),inter,s(1));END arch_full;

Adder2.vhdENTITY full_adder ISPORT(

a,b : IN bit_vector(1 DOWNTO 0);cin : IN bit;cout : OUT bit;s : out bit_vector(1 DOWNTO 0));

END full_adderARCHITECTURE arch_full OF full_adder ISSIGNAL inter : bit;COMPONENT half_adder

PORT (a,b,cin : IN bit;cout,s : OUT bit);

END COMPONENT;BEGIN

u1:half_adder PORT MAP(a(0),b(0),cin,inter,s(0));

u2:half_adder PORT MAP(a(1),b(1),inter, cout,s(1));

END arch_full;

ENTITY half_adder ISPORT( a,b,cin : IN bit;

cout,s : OUT bit);END half_adder

ARCHITECTURE arch_half OF half_adderISBEGIN

s <= a XOR b XOR cin;cout <= (a AND b) OR (a AND cin)

OR (b AND cin);END arch_half;

2.11 Description hiérarchique2.11.1 Description hiérarchique : Component

28/10/2014 11:18 R. EL ALAMI 103

En résumé :Trois opérations sont nécessaires :- Le couple entité-architecture du sous-ensemble doit être créé et annexé à

une librairie de l’utilisateur, par défaut la librairie « work ».- Le sous-ensemble précédent doit être déclaré comme composant dans

l’ensemble qui l’utilise, cette déclaration reprend les éléments principaux de l’entité du sous-ensemble.

- Chaque exemplaire du composant que l’on souhaite inclure dans le schéma en cours d’élaboration doit être connecté aux équipotentielles de ce schéma, c’est le mécanisme de l’instanciation.

- Au moment de la déclaration : (exemple de add)

2.11 Description hiérarchique2.11.1 Description hiérarchique : Component

28/10/2014 11:18 R. EL ALAMI 104

component nom_composant -- même nom que l’entitéport ( liste_ports ) ; -- même liste que dans l’entitéend component ;

. Possibilité d'utiliser un même objet plusieurs fois avec des tailles différentes

. La clause generic map dans l'instanciation du composant ADD permet de fixer la valeur du paramètre. . Possibilité d'instancier des entités/architectures fonctionnellement identiques mais de taille différente

. Déclaration d'un additionneur

ENTITY adder isGENERIC (largeur : integer :=8); -- valeur par défaut PORT( a,b: IN signed_vector(largeur-1 DOWNTO 0);

s : OUT signed_vector(largeur DOWNTO 0);END adder;

ARCHITECTURE arch_adder OF adder ISBEGIN

s <= a + b;END arch_adder;. Instanciation avec

une largeur de 16 bits

2.11 Description hiérarchique2.11.2 Description hiérarchique : Généricité

28/10/2014 11:18 R. EL ALAMI 105

U0 : adder GENERIC MAP (16)PORT MAP (a,b,s);

La généricité est un moyen de transmettre une information à un bloc ou à un couple entité-architecture.

Cette information est statique pour le bloc.

Vue de extérieur, c´est un paramètre.

En fait, il s´agit d´une constante qui sera fixée au moment de l´instanciation du bloc ou du composant.

Les associations de paramètres (generic map) et de ports (port map) définissent des associations locales entre les noms utilisés dans la déclaration de composant (paramètres et ports formels) et les paramètres et ports effectifs de l'instance.

28/10/2014 11:18 R. EL ALAMI 106

2.11 Description hiérarchique2.11.2 Description hiérarchique : Généricité

28/10/2014 11:18 R. EL ALAMI 107

2.11 Description hiérarchique2.11.2 Description hiérarchique : Généricité

28/10/2014 11:18 R. EL ALAMI 108

2.11 Description hiérarchique2.11.2 Description hiérarchique : Généricité Autre exemple : additionneur structurelle générique :

construit à partir d’un additionneur 1 bit assemblage des N additionneurs 1 bit afin de réaliser l’additionneur complet la valeur de N est inconnue avant l’instanciation du composant

28/10/2014 11:18 R. EL ALAMI 109

2.11 Description hiérarchique2.11.2 Description hiérarchique : Généricité On dispose de l’entité Add et son architecture :entity Add is

port (A, B, Cin : in std_logic;S, Cout : out std_logic);

end Add ; L’entité Additionneur générique s’écrit :

entity AdditionneurN isgeneric (N : Natural := 8);port (

X, Y : in std_logic_vector ( N-1 downto 0);Cin : in std_logic;S : out std_logic_vector (N-1 downto 0);Cout : out std_logic);

end AdditionneurN ;

architecture structurelle of AdditionneurN iscomponent Add

port (A, B, Cin : in std_logic;S, Cout : out std_logic);

end component;signal C : std_logic_vector(0 to N);

beginlabel: for I in 0 to N-1 generate

Instance : Add port map (X(I), Y(I), C(I), S(I), C(i+1));

end generate label;C(0) <= Cin;Cout <= C(N);

end structurelle ;

. Regroupement d'objets divers :- types- sous-types- constantes- sous-programmes- composants, …

. Accessibilité ou visibilité : le package se nomme mon_package et a été compilé et stocké dans la bibliothèque librairie1

. Possibilité d'utiliser plusieurs packages dans une même description

. Les standards IEEE 1164 et IEEE 1076.3 sont accessibles via des packages

LIBRARY librairie1 USE librairie1.mon_package.all

2.11 Description hiérarchique2.11.3 Description hiérarchique : Package

28/10/2014 11:18 R. EL ALAMI 110

. 2 parties :. Partie déclarative (spécification)

- Déclarations des éléments visibles à l'utilisateur du package. Corps du package (implantation)

- Chaque élément défini dans la partie déclarative est visible du corps

PACKAGE data_types ISSUBTYPES address is bit_vector(24 DOWNTO 0);SUBTYPES data is bit_vector(15 DOWNTO 0);CONSTANT vector_table_loc : address;FUNCTION data_to_int(value : data) RETURN integer;FUNCTION int_to_data(velue:integer) RETURN data;

END data_types;

PACKAGE BODY data_types isCONSTANT vector_table_loc : address := X"FFFF00";FUNCTION data_to_int(value : data) RETURN integer IS;

--body of data_to_intEND data_to_int;FUNCTION int_to_data(velue:integer) RETURN data IS;

--body of int_to_dataEND int_to_data;

end data_types;

2.11 Description hiérarchique2.11.3 Description hiérarchique : Package

28/10/2014 11:18 R. EL ALAMI 112

Il existe trois modes pour les paramètres des procédures:

in: le paramètre est passé en valeur et ne peut donc pas être modifié par la procédure

out: le paramètre est modifié par la procédure, inout: le paramètre est passé par référence et il peut donc être lu et

modifié

. Déclaration de procédures

. Appelinstruction formée du nom de la procédure et des paramètres effectifs

PROCEDURE nom (liste de paramètres) IS déclarationBEGIN instructions END nom;

28/10/2014 11:18 R. EL ALAMI 113

2.11 Description hiérarchique2.11.4 Description hiérarchique : Procédures

Exemple:

type byte is array (7 downto 0) of std_logic;•••

procedure ByteToInteger (ib: in byte; oi: out integer) isvariable result : integer := 0;begin

for i in 0 to 7 loopif ib(i) = '1' then

result := result + 2**i;end if;

end loop;oi := result;

end ByteToInteger;

28/10/2014 11:18 R. EL ALAMI 114

2.11 Description hiérarchique2.11.4 Description hiérarchique : Procédures

Tous les paramètres d’une fonction sont de mode in: en dehors de ses variables locales, une fonction ne peut modifier que la valeur retournée. En plus, les paramètres ne peuvent pas être de type variable: ils ne peuvent être que des constantes ou des signaux

. Déclaration des fonctions

Exemplefunction f (a, b, c : std_logic) return std_logic isvariable x : std_logic;beginx := ((not a) and (not b) and c);return x;end f;

N.B : Par rapport à la fonction, La procédure permet d'avoir plusieurs sorties, mais à condition de déclarer les entrées et les sorties comme dans une entité ou composant.

FUNCTION nom (liste de paramètres) RETURN type IS déclarationsBEGIN instructions end nom;Résultat d'une fonction : return expression;

28/10/2014 11:18 R. EL ALAMI 115

2.11 Description hiérarchique2.11.4 Description hiérarchique : Fonctions

Fonction de calcul de minimum et maximum en procédure.

28/10/2014 11:18 R. EL ALAMI 116

procedure MinMax( a,b : in unigned (7 downto 0);min : out unsigned(7 downto 0);max : out unsigned(7 downto 0)) is

beginif (a < b) then

min <= a; max <= b;else

min <= b; max <= a;end if;

end procedure MinMax;

MinMax(x, y, z, t);

function min (a,b : unsigned(7 downto 0)return unsigned(7 downto 0) isvaraiable min : unsigned(7 downto0);begin

if (a < b) thenmin := a;

elsemin := b;

end if;return min;

endfunction

...z := min(x, y);

Il faut 2 fonctions min et max pour avoir l'équivalent en fonction. Voici l'exemple de min :

Une librairie est une collection de modules VHDL qui ont déjà été compilés. Ces modules peuvent être des paquetages, des entités ou des architectures.

. Les programmes objets sont placés dans des bibliothèques

. Eléments d'une bibliothèque :. Définitions de types, constantes, procédures PACKAGE. Architecture de circuits ARCHITECTURE. Associations composants/architectures CONFIGURATION

. 2 types de bibliothèque. Bibliothèque de l'utilisateur (user library). Bibliothèque système

28/10/2014 11:18 R. EL ALAMI 117

2.11 Description hiérarchique2.11.5 Description hiérarchique : Library

28/10/2014 11:18 R. EL ALAMI 118

2.11 Description hiérarchique2.11.5 Description hiérarchique : Library

Les librairies Facilite la tâche du concepteur Rajout de fonctionnalités supplémentaires

La librairie IEEE A mettre au début de votre description Pour rajouter les types étendues std_logic et std_logic_vector

use IEEE.STD_LOGIC_1164.all; DORENAVANT nous remplacerons SYSTEMATIQUEMENT

BIT par STD_LOGIC BIT_VECTOR par STD_LOGIC_VECTOR

Pour utiliser des fonctions arithmétiques sur ces STD_LOGIC_VECTOR USE IEEE.NUMERIC_STD.ALL; Et aussi USE IEEE.std_logic_arith.all;

• Q<=Q+1; -- Q étant par exemple un std_logic_vector et 1 est un entier!! • A<B -- A et B des std_logic_vector

28/10/2014 11:18 R. EL ALAMI 119

Complément sur les opérations arithmétiques Le rajout de use IEEE.numeric_std.all; permet

De travailler avec des valeurs signées et non signées• signal A,B: signed(3 downto 0);• signal tempo: unsigned(3 downto 0);

De convertir un std_logic_vector en signed ou unsigned• A<= signed(SW(3 downto 0));• B<=unsigned(RES);

De convertir des signed ou unsigned en std_logic_vector• LEDG(3 downto 0)<=std_logic_vector(tempo);

De travailler avec les opérateurs arithmétiques standard• >, >=, =<,<, + ,- etc….

Le rajout de use IEEE.std_logic_unsigned.all; permet De travailler avec les opérateurs arithmétiques standard de mélanger des entiers avec des std_logic_vector: A<= A +1;

. Bibliothèque WORK- En réalité : Un espace de travail- Tous les éléments créés par l'utilisateur au sein d'un même projety sont rangés- Ces éléments sont réutilisables à tout instant dans le projet aprèsles avoir déclarés

. Exemple d'utilisation d'un package issu de la bibliothèque WORK- L'utilisateur a créé un package operateur_arithmetique dans WORK- Pour y avoir accès

USE WORK.operateur_arithmetique.ALL

- Pour utiliser l'élément mult de ce package

FOR ALL : multiplieur USE ENTITY WORK.mult(comportementale)

28/10/2014 11:18 R. EL ALAMI 120

2.11 Description hiérarchique2.11.5 Description hiérarchique : Library