TP n°2 Timer PWM F446 - ENSEA · Architecture des systèmes à microprocesseur TP n°2 : Timer /...

Transcript of TP n°2 Timer PWM F446 - ENSEA · Architecture des systèmes à microprocesseur TP n°2 : Timer /...

M1-Archi 2016-2017 Page1

___________________________________________________________________________

ArchitecturedessystèmesàmicroprocesseurTPn°2:Timer/générationdesignalPWM

___________________________________________________________________________

Objectifsdelaséance-CompréhensiondufonctionnementduTimer-ProgrammationdesregistresduTimer-SavoirgénérerunsignalPWMàpartirduTimer

___________________________________________________________________________

Matérielrequis: -Uneplateformenucleo-boardSTM32F446REparbinôme___________________________________________________________________________Organisationdelaséance:

1) DescriptionduTimeretdesesregistres2) ConfigurationduprojetsousSTM32CubeMX3) Générationd’unsignald’horloge4) Générationd’unsignalPWM5) Conclusion/Bilan

ToutaulongdeceTP,desquestionsvoussontposées.Prenezletempsd’yrépondreetdeprendredesnotes.___________________________________________________________________________I. Introduction

Lors de cette séance, vous allezmettre enœuvreunpériphérique incontournable des

microcontrôleurs,letimer.Letimerestuncompteurconfigurablede16ou32bitspermettantdedélivrerunebasedetemps,servantgénéralementderéférencedanstoutessortesd’applications.LeSTM32F446REpossède17timers;dont12de16bitset2de32bits,les3restantsétantdédiésauSysTicketà2watchdog1.

1DocumentationcomplèteduSTM32F446REdisponibleici(débutpage446):http://www.st.com/content/ccc/resource/technical/document/reference_manual/4d/ed/bc/89/b5/70/40/dc/DM00135183.pdf/files/DM00135183.pdf/jcr:content/translations/en.DM00135183.pdfDocumentationdestimersdesSTM32:http://www.st.com/content/ccc/resource/technical/document/application_note/group0/91/01/84/3f/7c/67/41/3f/DM00236305/files/DM00236305.pdf/jcr:content/translations/en.DM00236305.pdf

M1-Archi 2016-2017 Page2

• LestimersLestimerspeuventêtreutilisésdansplusieursmodes: -inputcapture:mesurerladuréed’unpulsed’unsignalenentrée -outputcompare:générationdesignauxpériodiques

-PWM(PulseWidthModulation):modulationdelargeurd’impulsiondesignaux-Onepulse:générationd’unpulseensortie

Laduréedessignauxgénéréspeuts’étendretypiquementdequelquesmicrosecondesàquelquesmillisecondes.Eneffet,l’ajustementdeladurées’effectueparlasélectiondelasourced’horloged’entréedutimeretdesvaleursdeprescaling.Auniveaudutimeretducontrôleurderesetetdesd’horloges(RCC),cesblocsdeprescalingpermettentdediviserunefréquenced’horlogeparunevaleurspécifiqueconfigurable.Parexemple,leTimer1possèdeunprescalersur16-bits.

Questions:-Parquelfacteurpeut-ondiviserlafréquenced’horlogeàl’aided’unprescalersur16bits?[1à].

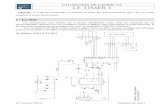

Figure1:blocdiagrammedutimer1

M1-Archi 2016-2017 Page3

Onpeutnotersurlafigure1,queTimer1possède4canauxindépendants(TIM_CH1àTIM_CH3)pouvantfonctionnerdanslesdifférentsmodesdécritsprécédemment.

• LesprincipauxregistresdestimersL’unitédecomptagedutempssebaseessentiellementsur4registres:

-Counterregister(TIMx_CNT)-Prescalerregister(TIMx_PSC)-Auto-reloadregister(TIMx_ARR)-Repetitioncounterregister(TIMx_RCR)

LeTIMx_CNTestleregistredecomptage,leTIMx_PSCestleregistrepermettantdediviserl’horlogederéférence,TIMx_ARRpermetdedéfinirunevaleurseuildéclenchantlaremiseà0ducompteurouledécomptageparexemple.Pourfinir,leregistreTIMx_RCRestutilisépourlarépétition.Lecontenuduregistreindiquecombiendefois(TIMx_RCR+1)doitêtrerépétélecomptageavantdegénérerunUpdateEvent(UEV).SinonunUEVestgénéréàchaquefoisquelecompteurgénèreunoverflow.

• Définitiondel’horlogederéférenceL’horlogederéférencequiestfournieauprescalerestnotéeCK_PSC.L’horlogeissue

duprescalerestl’horlogedutimeretelleestnotéeCK_CNT(cf.lafigure1).L’horlogederéférenceCK_PSCpeutprovenirdeplusieurssources:

è Horlogeinterne(CK_INT)è D’unebroched’entréeexterne(Externalclockmode1)è D’untriggerexterned’entréeETR(Externalclockmode2)è Deplusieurstriggersinternes(ITRx).Parexemple,danslecasoùuntimer

serviraitdediviseurd’horloged’unautretimer.

• LestypesdecomptageLesregistresdecomptagepeuvents’incrémenter,sedécrémenter,oubienlesdeux.Ilsse

rechargentautomatiquementàl’aideduregistreTIMx_ARR.

o UpcountingDans cemode, le compteur compte de 0 jusqu’à la valeur définie dans le registre

TIMx_ARR.Puisilrecommenceà0etgénèreunévènementd’overflow(UpdateEVent-UEV).Dans le cas d’un compteur à répétition, cet UEV après que le compteur est effectuéTIMx_RCR+1boucledecomptage.Sinon,l’UEVestgénéréàchaqueoverflow.Unflagd’interruptionpeutaussiêtregénéré.

M1-Archi 2016-2017 Page4

Figure2:Upcountingmodeavecseuilà0x36(TIMx_ARR)

etprescalingd’horlogeà1

o DowncountingMêmeprincipequedanslecasprécédentoùcettefois-ci,lecompteurdécrémentede

la valeur seuil (TIMx_ARR-1) jusqu’à 0, puis recommence si la répétition est activée.L’événementestaussigénéréàlafindeladécrémentation.

o Center-alignedmode(up/downcounting)Danscemode,lecompteurvade0àlavaleurduregistreTIMx_ARR–1,génèreun

événementd’overflow,puisdécomptejusqu’à1etgénèreunévénementd’underflow.Puislecompteurrecommencelecomptageàpartirde0.

Figure:Illustrationdutimerenmodecenter-aligned

(Prescaling=1etTIMx_ARR=?)Question:QuelleestlavaleurinscritedansleregistreTIMx_ARRdansl’exempleprésentéenfigure3?

o RepetitioncounterNous avons vu qu’il était possible de compter/décompter demanière répéter un certainnombredefoisindiquéparleregistreTIMx_RCR,avantdegénérerunUEV.CeciesttrèsutilepourlagénérationdesignauxdetypePWMparexemple.Surlafiguresuivante,onpeutobserverl’impactduchoixdelavaleurdunombrederépétitionindiquédansTIMx_RCRsurlagénérationdesUEV.

M1-Archi 2016-2017 Page5

Impact

• ModeCapture/CompareDans ce mode, l’objectif est l’acquisition d’un signal (Capture), son filtrage puis la

détectiondefrontavecsélectiondepolaritévialeregistreTIxFPx.Ladétectiondefrontpeutservirdetriggerd’entréeouordredecapture.L’étagedesortie(capture/compareblock)estconstituédedeuxregistres,uncomparateuretunregistredesortiedecontrôle.Danscemode,ilestpossibledemesurerdeslargeursoudesfréquencesd’impulsion.

• ModeInputCaptureDanscemode,lesregistresTIMx_CCRxpermettentderécupérerlavaleurducompteur

aprèsqu’unetransitionaitétédétectéesurlesignald’entréeICx.Danscecas,leflagCCXIFduregistreTIMx_SRestmisà1etuneinterruption(ourequêteDMA)estgénérée(siellessontautorisées).Ceflagestremisà0lorsdelalectureduregistredecomptageTIMx_CCRx.Atitred’exemple,onpourraitutilisercemodepourmesurerl’intervalledetempsentredeuxfrontsmontantsdétectésconsécutivementsuruneentrée.

• OutputCompareMode(cf.p262[1])

Cette fonction permet le contrôle et la génération de signaux. Elle peut aussi êtreutiliséepourindiquerlorsqu’unepériodedetempsprécisevientdes’écouler,enpositionnantunesortieà0ou1parexemple.Commesonnom l’indique, l’objectifestdecomparer lavaleurducompteuraveccelleduregistredecapture/compare(TIMx_CCRx).Achaquedétectiondevaleurégale,l’étagedecomparaisonpeutalors:

-assignerensortieunevaleurdéfinievialesbitsOCxMduregistreTIMx_CCMRx,

M1-Archi 2016-2017 Page6

-changerlapolaritédelabrochesortieenmodifiantlebitCCxPduregistreTIMx_CCER-nepaschangerlavaleurdelabrochedesortie(OCxM=000),l’activer(001),ladésactiver(010)oulatoggler(011).

Unflagd’interruptionestmisà1(bitCCxIFduregistreTIMx_SR).Silemasqued’interruptionestactivé(bitCCXIEduregistreTIMx_DIER),alorsuneinterruptionestgénérée.UnerequêteDMApeutaussiêtreactivéesilebitCCxDEduregistreTIMx_DIERetlebitCCDSduregistreTIMx_CR2(sélection)sontactivés.

Figure:illustrationdumondeOutputcompare

• PWM(cf.p263[1])Letimerpeutaussipermettrelagénérationd’unsignaldontlafréquenceetlerapportcycliquesont contrôlables par des registres. On peut alors générer un signal dont la largeur desimpulsions est modulée (PWM). Le registre TIMx_ARR (compteur) permet de définir lafréquencetandisqueleregistreTIMx_CCRxcontrôlelerapportcyclique.

Figure:illustrationdelagénérationdesignauxpourdifférentsrapportscycliques(dutycycle)

M1-Archi 2016-2017 Page7

LasélectiondumodePWMestindépendantesurchaquecanal(jusqu’à4partimercommeindiquéenfigure1,avec1signalPWMparsortieOCx),ets’effectueendéfinissantlesbitsOCxMauxvaleurs‘110’(PWMmode1)ou‘111’(PWMmode2)duregistreTIMx_CCMRx.DanslesdeuxmodesPWM(1et2),lesregistresTIMx_CNTetTIMx_CCRxsontcomparéspourdéterminersisoitTIMx_CCRx≤TIMx_CNTouTIMx_CNT≤TIMx_CCRx(celadépendaussidusensdecomptage).

Le timer est capable de générer un signal PWM dans lemode ‘edge-aligned’ ou ‘center-aligned’.Cechoixs’effectueparlesbitsCMSduregistredeconfigurationTIMx_CR1.

a) b)Figure:edge-alignedmode(a)vscenter-alignedmode(b)(TIMx_ARR=8)

o PWMedge-aligned

§ Upcountingconfiguration(bitDIRà0deTIMx_CR1)LesignalPWMderéférenceOCxREFestàl’étathautaussilongtempsqueTIMx_CNT<TIMx_CCRx,étatbassinon.

§ Downcountingconfiguration(bitDIRà1deTIMx_CR1)

LesignalPWMderéférenceOCxREFestàl’étatbasaussilongtempsqueTIMx_CNT>TIMx_CCRx,étathautsinon.

o DifférenceavecunsignalPWMcenter-aligned

Center-aligned

Edge-aligned

M1-Archi 2016-2017 Page8

Unexemplepourrésumer:Sil’onsouhaitegénérerunsignalPWMdefréquence1kHz(PériodedeT=1ms)avec

unrapportcycliquede50%etquel’onsupposeunehorlogeenentréedutimerdefréquence10MHz(100ns).

1- définirlavaleurduprescalerPSC(attentionvaleurcodéesur16bits).OnpeutchoisirPSC=10.Ainsionauraunefréquencedecomptagede1MHz(1us)

2- définirlapériodedecomptage.Onchoisit1000car1000x1us=1ms.Lapériodeducompteurseradoncde1ms(1kHz).

3- DéfinirlePulse(largeurdel’impulsion)quiseradoncde500pouravoirunrapportcycliquede50%.

• One-Pulsemode(cf.p273[1])

Lefonctionnementdanscemodeestlégèrementparticulierparrapportauxprécédents.

Cemodepermetdedéclencher le compteur en réponse àun stimulus et de générer uneimpulsionpendantuneduréeprogrammableainsiqu’aprèsundélaiprogrammable.La sélection de cemode s’effectue enmettant le bit OPM à 1 du registre TIMx_CR1. Lecompteurs’arrêteraalorsàlagénérationduprochainévènement.Unexempleestdétaillédansledoc[1].

Figure:générationd’uneimpulsionàl’aidedutimer

• SynchronisationavectriggerexterneEnfonctiondel’utilisation,letimerpeutêtresynchronisésuivantsplusieursmodes:

-ResetMode-GatedMode-TriggerMode

o Slavemode:ResetLecompteuretsonprescalerpeuventêtreréinitialisésenréponseàunévénement

suruneentréedetrigger.Surlafiguresuivante,lorsdufrontmontantsurl’entréeTI1,lecompteurestremisàzéro.OnsupposeaussiqueTIMx_ARR=0x36.Onnotequeleflagdetriggerestaussimisà1.

M1-Archi 2016-2017 Page9

Figure:Modeesclave,lereset

o Slavemode:GatedmodeDanscetautremodeesclave,lecompteurpeutêtreactivéenfonctionduniveaud’une

entréesélectionnée.Dansl’exemplesuivant,lecompteurs’incrémenteuniquementlorsqueTI1estàl’étatbas.Onremarqueenplusquelecomptageestcontrôléparl’entréeCNT_ENquidoitêtreactive.LeflagTIFduregistreTIMx_SRestmisà1lorsquelecompteurcommenceets’arrêtedecompter.

Figure:Modeesclave,lemode‘gated’

o Slavemode:trigger

Dans cemode, le compteur est activé en réponse à unévénement sur uneentréesélectionnée.Dans l’exemple suivant, le compteur est activé lors de la détectiondu frontmontant sur l’entrée TI2. Le délai d’activation est lié au circuit de resynchronisation surl’entréeTI2.

Figure:Modeesclave,lemode‘trigger’

Danslemêmeprincipe,ilexistelemodetrigger+externalclockmode2(cf.p281[1]).Danscecas,enplusde l’activationducompteurà ladétectiond’unévénementsuruneentréedédiée,unehorlogeexterneestdélivréeaucompteur.Leprincipeest illustrésur la figuresuivante:

M1-Archi 2016-2017 Page10

Figure:Modeesclave,lemode‘trigger+externalclockmode2’

II. ProgrammesàréaliserEXERCICE1:ALLUMAGEPERIODIQUED’UNELED

Onsouhaiteutiliserletimer1enmodeinterruptionafindetogglerlaledLD2toutes

lessecondes(f=1Hz).Uneinterruptionseradoncgénéréetouteslessecondes.Pourcela,onvaconfigurerletimerpour: -définirlafréquenced’horlogeducompteur(Prescaler) -définirlapériodedecomptagepourgénéreruneinterruptionàuninstantdonné.Questions: -Quelleestlafréquenced’horlogeenentréedutimer(avantprescaler) -Parcombiendoit-ondiviserlafréquencedecettehorlogeauniveauduprescaler? -Jusqu’àcombiendoits’incrémenterlecompteuravantdegénérerl’interruption?

• ConfigurationduprojetsousSTM32CubeMX

Comme au TP précédent, on se propose d’utiliser l’outil STM32CubeMX pourconfigurergraphiquementlemicrocontrôleur.Onyspécifienotammentlessourcesd’horloge,lespériphériquesquel’onsouhaiteutiliser,lessourcesinterruptions,etc.

1. LancerSTM32CubeMX

M1-Archi 2016-2017 Page11

2. Créerunnouveauprojet.Chercheretsélectionnerensuitelaplateformequel’onsouhaiteutiliser(Nucleo64avecunMCUSTM32F446RETx)puisOK.

Vousarrivezsurl’écranprincipaldeconfigurationduMCU.

M1-Archi 2016-2017 Page12

3. Faireuneremiseàzérodesbrochesvial’ongletPinout/ClearPinouts

4. VouspouvezobserverdanslafenêtrePinout,l’ensembledespériphériquesquipeuvent être utilisés ainsi que les OS temps-réels et autres fonctionnalitéslogicielles.

5. AcôtédePinoutsetrouveclockconfiguration.

Danscettefenêtre,vouspouvezgraphiquementdéfinirlessourcesd’horlogepourconfigurerl’horlogeprincipale(SYSCLK)dumicrocontrôleur.Vousnoterezqu’ilexisteplusieursentréespossibles (HSI/HSE et PLLCLK). En d’autres termes, vous pouvez choisir entre une sourced’horloge interne (HSI - 16MHz), une sourced’horloge externe (HSE – 4 à 26MHz) et une

M1-Archi 2016-2017 Page13

horlogegénéréeparunePLL(PLLCLK).Deplus,vousremarquerezquel’horlogedesbusetdespériphériquesdépendentdeSYSCLK,hormisl’horlogepourl’USBainsiquepourl’audio(I2Sclock).Dans la fenêtre Pinout, indiquer comme source d’horloge HSE (High Speed Clock) que lasourced’horlogeprovientduCrystal/CeramicResonator.

Nous avons vu aussi qu’il existe un registre spécifique de contrôle au sein dumicrocontrôleurpermettantdeconfigurerlessourcesd’horloge.C’estleregistreRCC(ResetandClockControl).

Dans clock configuration, modifier certains éléments afin d’obtenir une horlogeSYSCLKde84MHZ.

Les horloges fournies aux timers sont définies à partir des horlogesAPB1_TIMER_Clocks (TIMER 2,3,4,5,6,7,12,14) et APB2_TIMER_Clocks (TIMER1,8,9,10et11).

6. Lecontrôleurderesetetd’horloge(RCC)permetaussideconfigurerles

différentessourcesdereset:o Systemreset(remiseàzérodesregistresviaNRSTpin)o Powerreset,o Backupdomainreset.

M1-Archi 2016-2017 Page14

Pourpermettreune interruptionde reset, il estnécessairede l’autoriserauniveau du contrôleur d’interruption NVIC comme indiqué sur la figure suivante,accessiblevialafenêtreconfiguration:

ApplyandOK.

7. Onsouhaiteaussipouvoircontrôler laLED.Celle-ciestconnectéeauPortA

d’E/S(GPIOA)etàlabroche5(PA5).VouspouvezlacherchervialeFind:

IlfautdoncladéfinirentantqueGPIO_Outputcommesuit:

Vousnoterezque labrochePA5possèdeplusieurs fonctionnalités (pouvantserviràd’autrespériphériquescommeleTIMER2,l’ADC,laliaisonSPI…).Une

M1-Archi 2016-2017 Page15

fois configurée, retourner dans la fenêtre configuration, puis GPIO. Vousnoterezcommentaétéconfiguréelabroche(push-pull…)Optionnel:delamêmefaçonquePA5,onpourraitconfigurerlabrochePC_13entantqu’entréed’interruptionGPIO_EXTI13.Onrappellequecettebrocheestdirectement reliée au bouton poussoir utilisateur. Dans la fenêtreconfiguration,puisGPIO,vousdevezobtenirl’imagesuivante:

8. Configurationdutimer(pourExo1)AjouterensuitedanslafenêtrePinout,letimer1.Onindiqueraseulementlasourced’horlogecommeétantinterne.

Danslafenêtreconfiguration,puisTIM1,onpeutobserverlesparamètressuivants:

M1-Archi 2016-2017 Page16

Modifier les paramètres du Prescaler et de Counter Period pour que lecompteurdupuisseavoirunepériodedecomptaged’1s.Dans l’ongletNVIC Settings, cochez la case Enable pour TIM1 update andTIM10 global interrupt. De cettemanière, une interruption sera générée àl’issuedechaquecycle.ApplyetOK.

9. GénérationducodeetduprojetpourKeiluVisionC’estladernièreétapedeconfigurationduprojet.AllerdansProject/Settings.

DansProjectNameindiquerlenomdevotreprojet.DansProjectlocation,indiquerlerépertoiredevotreprojetoùseragénérerlecode.DansToolchain/IDE,indiquerMDK-ARMv5.

M1-Archi 2016-2017 Page17

Dansl’ongletsuivant,CodeGenerator,sélectionner“Copyonlythenecessarylibraryfiles”.

PuisOK

M1-Archi 2016-2017 Page18

Enfin,dansl’ongletProject,GenerateCode.

CliquerensuitesurOpenProjectpourouvrirleprojetgénérésousµVision.

• Sousvision(Kiel)Compléterlecodegénérépourréaliserlafonctionnalitésouhaitée.

->Pourcela,regarderlesfonctionsdisponiblesdanslalibrairie.

Encasdeproblème,servez-vousdudebuggerafind’observerlesregistresdutimer.

EXERCICE2:GENERATIOND’UNSIGNALPWM

On souhaitemaintenant générerun signal constituéd’impulsions, dont la largeur sera

moduléepar logiciel.Nousavonsvuqu’unpériphériquecomme letimerpeutgénérerdessignauxPWM.Danslapremièrepartiedudocumentsontrappeléeslescaractéristiquesdecessignaux.

Voicilesspécificationsdusignalàgénéreràl’aidedutimer1:Fréquence=50kHz(T=20us)Rapportcycliquede30%.

Sous STM32CubeMx, créer un nouveau projet comme pour l’exercice précédent jusqu’àl’étape7incluse.L’étape8comprendralaconfigurationdutimer1pourgénérerlesignal.Unefoisquetoutestcorrectementconfiguré,générerlecodecommeprécédentetlancerµVision.

1. µVision

1ièreversion:

M1-Archi 2016-2017 Page19

CompléterlecodegénéréafindepouvoirobserversurlabrochePA8,unsignalPWMavecunefréquencede50kHzetunrapportcycliquede30%.Unoscilloscopepermettradevisualiseretvalidervotreconfiguration.-Fairevaliderparl’enseignant

2ndeversion:

Modifierlecodeafindepouvoirprendreencompteunsignald’interruptionprovenantduboutonpoussoir(PC_13).Unappuisurceboutondevrapermettred’incrémenterde10%lalargeurdel’impulsion,c’est-à-direaugmenterde10%lerapportcyclique.-Fairevaliderparl’enseignant

3ièmeversion:

Onsouhaitequeletimerpuisseêtredéclencherparl’intermédiaired’unsignalexternedecommande.Enfonctiondelavaleurdecesignal,onactiveralecomptageounon.Onémuleracesignaldecommandeparl’intermédiaireduboutonpoussoir.Vousvousréfèrerezàladocumentationpoursavoirsurquellebrochedoitêtreenvoyélesignaldecommande.Onpourraémulerunsignalprovenantdel’extérieuràl’aideduboutonpoussoir. Lors de l’appui, le timer sera activé, sinon il sera bloqué. Pour montrerl’activitédutimer,onseproposed’allumerparinterruptionlaledtouteslessecondes.-SousSTM32CubeMx,CréerunnouveauprojetetconfigurerleTimer1enMode‘Gated’,lesentréessortiesetlessourcesd’interruptions.-SousuVision,Modifierlecodesibesoin-Fairevaliderparl’enseignant.

III. Bilanetconclusion

Lors de ce TP, vous avez pu mettre en œuvre un périphérique indispensable aumicrocontrôleur.Des interruptionspériodiquespeuventainsi rythmer lecyclede réveildumicrocontrôleur, le déclenchement d’acquisition et de réceptionde signaux pour d’autrespériphériquescommelesconvertisseursA/NetN/A,encoderdesdonnées,…IV. Références

[1] STMicroelectronics,“STM32F446xxadvancedARMbased32-bitMCUs”,RM0390ReferenceManual,

Jan2016,http://www.st.com/content/ccc/resource/technical/document/reference_manual/4d/e