Session FLUPA LYON - Pitch l’UX Design à ta grand-mère… et sois convaincant !

ISSCC 2011 / SESSION 12 / DESIGN IN EMERGING TECHNOLOGIES … · 2012-03-24 · 12 † 2011 IEEE...

Transcript of ISSCC 2011 / SESSION 12 / DESIGN IN EMERGING TECHNOLOGIES … · 2012-03-24 · 12 † 2011 IEEE...

12 • 2011 IEEE International Solid-State Circuits Conference

ISSCC 2011 / SESSION 12 / DESIGN IN EMERGING TECHNOLOGIES / 12.4

12.4 A 3.9ns 8.9mW 4×4 Silicon Photonic Switch Hybrid Integrated with CMOS Driver

Alexander Rylyakov, Clint Schow, Benjamin Lee, William Green, Joris Van Campenhout, Min Yang, Fuad Doany, Solomon Assefa, Christopher Jahnes, Jeffrey Kash, Yurii Vlasov

IBM T. J. Watson Reseach Center, Yorktown Heights, NY

The emerging field of silicon photonics [1-3] targets monolithic integration ofoptical components in the CMOS process, potentially enabling high bandwidth,high density interconnects with dramatically reduced cost and power dissipa-tion. A broadband photonic switch is a key component of reconfigurable net-works which retain data in the optical domain, thus bypassing the latency, band-width and power overheads of opto-electronic conversion. Additionally, withWDM channels, multiple data streams can be routed simultaneously using a sin-gle optical device. Although many types of discrete silicon photonic switcheshave been reported [4-6], very few of them have been shown to operate withCMOS drivers. Earlier, we have reported two different 2×2 optical switches wire-bond packaged with 90nm CMOS drivers [7,8]. The 2×2 switch reported in [7]is based on a Mach-Zehnder interferometer (MZI), while the one reported in [8]is based on a two-ring resonator.

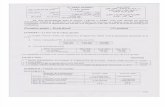

In this work we report a 4×4 silicon photonic switch composed of 6 MZI basedswitches actuated by integrated p-i-n diodes, 6 waveguide crossings and 8 I/Ofiber couplers as shown in Fig. 12.4.1. The switch is flip-chip bonded with aCMOS driver also shown in Fig. 12.4.1. Hybrid integration of photonic devicesand controlling electrical circuits is an important step towards a full monolithicintegration. It also offers significant advantages on its own by decoupling theoptimization, fabrication and test of the optical and electrical components,increasing the design exploration space and shortening turnaround times. Thedriver shown in Fig. 12.4.1 is an all-static CMOS circuit, fabricated in a standarddigital IBM 90nm process. The driver features an array of 6 output buffers, withpredrivers, controlled by a serial interface. Several versions of the driver chiphave been designed and evaluated. All variants operate with ample speed (50psto 100ps transition times) to drive ns-scale photonic switches. The photonicswitch electrical load was modeled as a forward biased p-i-n diode. The diodemodel (Fig. 12.4.1) includes a series resistance, a charge-dependent capacitanceand a current source of magnitude determined by carrier lifetime. The driver out-put inverter stages were sized to minimize the output impedance and to cover awide range of capacitive loads and steady state currents in the p-i-n diode result-ing from variations in carrier lifetime. The structure of the MZI based 2×2 switchis shown in Fig. 12.4.2. The optical signal, travelling in the on-chip waveguide,is split into two arms and then merged again. One arm contains a p-i-n diodethat implements an optical phase change through carrier injection. In the ONstate the input signal is routed to the T11 port, with T12 output attenuated by 21dB. In the OFF state the input is routed to the T12 port, while the T11 output isattenuated by 18dB within the 30nm optical bandwidth of the device (Fig.12.4.2). The 4×4 switch is composed of 6 2×2 switches as shown in Fig. 12.4.1,connecting each of the 4 inputs to any one of the other 3 outputs; note that inthis specific topology U-turns are not allowed, e.g., the West input (WIN) cannotbe routed to the West output (WOUT), etc. The 4×4 switch has a total of 9 differ-ent valid routing states, with each valid state requiring 0, 1, 2 or 4 2×2 switchesturned on.

A 4×4 switch can be built out of many different types of 2×2 switches. An inter-esting alternative to the MZI is a ring resonator based switch (Fig. 12.4.3). Thetwo-ring resonator switch is a smaller device, measuring only 25×50µm2, com-pared to 300x50µm2 of MZI. The device also offers significant savings in powerdissipation at the expense of narrower optical bandwidth and increased sensitiv-ity to temperature.

Measured optical transition times of the 2×2 MZI switch are shown inFig. 12.4.4. Testing was done with a continuous-wave 1530nm optical signalinjected into one input port at a time. A 100MHz PRBS7 switching signal wasapplied to a wirebonded single-channel CMOS driver circuit held at 1.0V supply.The extinction ratio and crosstalk were both measured to be better than 15dB.The measured OFF to ON and ON to OFF 10/90 transition times were 3.9ns and

1.4ns, respectively. The slower transient occurs during the carrier injectionphase. Power dissipation was measured with 50% duty cycle data and wasfound to be 2mW from a 1.0V supply. At speeds below 10MHz, typical for theswitch application, power dissipation is dominated by the steady-state contribu-tion of the injected carrier recombination in the switch.

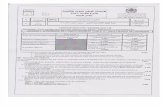

The 4×4 switch was tested with a flip-chip bonded CMOS driver. A customhybrid integration process was developed that included the following steps: NiAuplating of both photonic and CMOS bond pads, injection-molded solder process-ing to transfer PbSn solder balls to the CMOS chip and a flux-free flip-chip sol-der reflow to complete the assembly. The overall size of the micro-assembly was1×2×2mm3. Correct routing of each of the 4 inputs to any one of the other 3 wasverified by routing 40Gb/s data (Fig. 12.4.5). A 1531nm wave was modulatedwith a LiNbO3 modulator driven by a 40Gb/s PRBS7 data and edge-coupled tothe photonic chip with a lensed fiber probe. The output, also edge-coupled, wasamplified with an erbium-doped fiber amplifier (EDFA), wavelength filtered andreceived. A WDM transmission demonstration is shown in Fig. 12.4.6. In thisexperiment, 3 different wavelengths were passively combined and simultane-ously modulated with 40Gb/s PRBS7 data. One kilometer of standard single-mode fiber was used to decorrelate the wavelength channels in time via fiberchromatic dispersion. Three different routing states of the 4×4 switch were test-ed, routing the 3×40 Gb/s signal from the East input to each of the 3 possibleoutputs, as shown in Fig. 12.4.6. Power sensitivity curves were taken for eachstate and each wavelength, demonstrating BER < 10-12 at -10dBm average opti-cal power. All wavelength channels and all configurations were found to be with-in a 0.5 dB power spread at a BER of 10-12. Since each of the 2×2 switches dis-sipates 4mW in the ON state, the total power of the 4×4 switch depends on aparticular routing state and can be as high as 16 mW, when 4 of the 6 MZIswitches are turned on. Assuming uniform utilization of all 9 valid states and lowfrequency of routing state transitions, the average power of the 4×4 switchwould be 8.9mW. Insertion loss of the switch was in the range from 3 to 6dB,depending on the routing state. Off-chip coupler loss was around 1dB. In all 9valid states, the measured worst case crosstalk between channels was less than-10dB. The micrographs of the CMOS and the photonic dies are shown in Fig.12.4.7. CMOS drivers with predrivers occupied 144×520µm2. The total area ofthe 4×4 photonic switch was 300×1600 µm2.

Acknowledgements:The authors gratefully acknowledge support from DARPA under contractHR0011-08-C-0102. The views, opinions, and/or findings contained in this arti-cle are those of the authors and should not be interpreted as representing theofficial views or policies, either expressed or implied, of DARPA or theDepartment of Defense. Approved for public release, distribution unlimited.

References:[1] D. Kucharski, et al.,” 10Gb/s 15mW Optical Receiver with IntegratedGermanium Photodetector and Hybrid Inductor Peaking in 0.13µm SOI CMOSTechnology”, IEEE ISSCC Dig. Tech. Papers, pp. 360-361, Feb. 2010.[2] I.Young, et al., “Optical I/O Technology for Tera-Scale Computing”, IEEEISSCC Dig. Tech. Papers, pp. 468-469, Feb. 2009.[3] S. Assefa, et al., “Reinventing nanophotonic avalanche photodetector for onchip optical interconnects,” Nature, pp.84-88, March 2010.[4] Y. Vlasov, et al., “High-throughput silicon nanophotonic wavelength-insensi-tive switch for on-chip optical networks,” Nature Photonics, vol. 2, pp. 242–246,2008.[5] J. Van Campenhout, et al., “Low-power, 2×2 silicon electro-optic switch with110-nm bandwidth for broadband reconfigurable optical networks”, OpticsExpress 17(26), pp. 24020-24029, 2009.[6] B. G. Lee, et al., “High-Performance Modulators and Switches for SiliconPhotonic Networks-on-Chip,” IEEE JSTQE, vol. 16, no. 1, pp. 6-20, 2010.[7] B. G. Lee, et al., “Broadband silicon photonic switch integrated with CMOSdrive electronics,” in Proc. Conf. Lasers Electro-Optics (CLEO) 2010, paperCThJ1, 2010.[8] B. G. Lee, et al., “Comparison of Ring Resonator and Mach-Zehnder PhotonicSwitches Integrated with Digital CMOS Drivers”, IEEE Photonics Society AnnualMeeting, 2010.

©2011 IEEE

Session_12_Session_ 12/1/10 8:55 PM Page 12

13DIGEST OF TECHNICAL PAPERS •

ISSCC 2011 / February X, 2011 / X:XX XX

Figure 12.4.1: Block diagram of 4×4 photonic switch chip attached to CMOSdriver chip. Figure 12.4.2: Mach-Zehnder interferometer (MZI) based 2×2 switch.

Figure 12.4.3: Two-ring resonator based 2×2 switch.

Figure 12.4.5: Measured routing of 40 Gb/s data. Figure 12.4.6: Measured routing of 3 × 40 Gb/s WDM data.

Figure 12.4.4: Measured optical switching times of a 2×2 MZI switch.

12

Session_12_Session_ 12/1/10 8:56 PM Page 13

14 • 2011 IEEE International Solid-State Circuits Conference ©2011 IEEE

ISSCC 2011 PAPER CONTINUATIONS

Figure 12.4.7: CMOS and Silicon Photonic die micrographs.

Session_12_Session_ 12/1/10 8:56 PM Page 14