FPGAシステム FiCFPGA(Field Programmable Gate Array)...

Transcript of FPGAシステム FiCFPGA(Field Programmable Gate Array)...

慶應義塾大学天野研究室 CRESTプロジェクト「MEC用マルチノード統合システムの開発」

マルチFPGAシステム FiC

FiC, FiC-SW

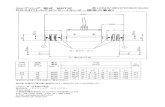

FiC SWボードの内部構成

現在のFiCの構成

FiC SWとは?FPGA(Field Programmable Gate Array)とは書き換え可能な大規模集積回路で、解法アルゴリズムをハードウェアで実行する高速計算用加速器(アクセラレータ)として注目されています。FiC(Flow-in Cloud)は、価格性能比に優れた中規模FPGAを9.9Gbpsの双方向リンクを32本により接続した大規模計算システムで、全体として巨大な回路を構成することができます。ネットワークには遅延と帯域が予測可能なSTDM(Static Time Division Multiplexing)型のサーキットスイッチング方式を採用し、要求を直接ハードウェアで処理することで、MEC(Multi-access Edge Computing)においてタイミングクリティカルな処理を行うことが期待されています。現在、慶應矢上キャンパスで稼働中の24枚のシステムをリモート環境で動かします。

ビデオのデモ環境

文献 http://www.am.ics.keio.ac.jpをご覧ください

現在のFiCシステムFiC SWボード

• FiC-SWは、コスト価格比に優れたKintexUltrascaleを利用、DDR-4 SD RAM 32GB、制御用Raspberry Pi 3を搭載

• FiCシステムは、FiC-SWボードを高速リンクで接続し、利用者からは一つの巨大なFPGAに見せかける

• 固定領域とユーザのプログラムが動く領域が分離されている

HLS

RasPi

HLS

RasPi

HLS

RasPi

HLS

RasPi

HLS

RasPi

HLS

RasPi

SW SW SW SW SW SW

Host Laptop Host Laptop上のFlow OSの指示により部分再構成スイッチの機能を維持したまま、HLS部の構成を変更 LeNetとパケット転送プログラム

FiC-SW6台利用

ネットワークは単純なループ

部分再構成可能

K.Musha, T.Kudoh, H.Amano, ”Deep Learning on High Performace FPGA Switching Boards: Flow-in-Cloud,” Proc. of Int.Symp. AppliedReconfigurable Computing, 2018 K.Azegami, et al, “An STDM (Static Time Multiplexing) Switch on a Multi-FPGA System” The 13th IEEE McSoC, 2019. など

Control Server

SW

ユーザはHLS(高位合成技術)を用いてC/C++でプログラム

FPGAの構成情報とネットワークの自動生成(*.json)

FPGA

FPGA

FPGA

FPGA

SW

SW

SW

SW

計算結果の転送

FiC制御ネットワーク入出力ネットワークは

独立

構成情報をRESTful API経由でラズパイに転送

Internet / Intranet

GUI control from remote terminals

FiC Network

デモの動作環境

• 深層学習による文字認識、CG法による行列計算、暗号化などのデモを実行します。

「MEC用マルチノード統合システムの開発」慶應大、熊本大、芝浦工大、NEC、東大、農工大、東海大、九州工大、東工大、アルプスアルパイン

戦略的創造研究推進事業(CREST) 研究領域「コンピューティング基盤」

Multi-access Edge Computing MECによるスマートシティの実現(西G)

Crust-Core型HUB(天野G、飯田G,若林G)

MEC(Multi-access Edge Computing)とは?

5Gをはじめとする高速ワイヤレス通信技術の発達により、従来クラウドで行われていた処理の一部を基地局の小規模なデータセンターで行うことで、工場制御、都市交通制御、電力制御などタイミングクリティカルな処理を効率的に実現する方式を、MEC(Multi-access Edge Computing)またはMEC(Mobile Edge Computing)と呼びます。このプロジェクトでは、アプリケーション、システムソフトウェア、CAD、FPGA、新デバイスの垂直統合研究グループにより、今年の10月から5.5年のプロジェクトでMEC向きのシステムを構築に挑戦します。

MEC用ソフトウェア(菅谷G)

省電力・情報のカプセル化・匿名化・低遅延化などのユビキタスソリューション

・位置情報サービス:位置情報をローカルにカプセル化、タイムクリティカルな衝突回避をローカルで解決

・健康・購買サービス:購買情報即時匿名化とカプセル化、健康情報匿名化と地域健康サービス(健康ポイント)

・家庭領域:家庭にける個人情報をローカルにカプセル化、ローカル電力需給の即時制御様々な標準化に対応

•MECとは?→エッジデバイスがつながる無線網の基地局近傍に計算資源を配置して行う処理

•基地局近傍に配置→性能・電力的に制限のあるエッジデバイスの処理をオフロード

•低遅延・無制御の輻輳が発生しない→通信性能の点では準リアルタイム処理が可能

•当該基地局につながる様々なデバイスを同時サポート→クラウド的共有資源

•基地局の消費電力削減が必要→低消費電力への要求が大きい

•工場制御、交通制御、電力制御などのタイミングクリティカルな処理への適用

センサ値 センサ入力

画像入力

フィルタ処理

PID制御停止判断

画像

フィルタ後データ

推論処理

モータ駆動モータ出力値

特徴量特徴量抽出

学習用画像選択学習用画像学習処理

推論結果学習結果

学習結果重み更新

マイクロ秒オーダの最大遅延要求

ミリ秒オーダの最大遅延要求

Crust VMM・OSを用いたヘテロジニアスなシステムの支援

・DSA/FPGAの仮想化→ヘテロジニアスなシステムの統一的な扱いが可能・MECコンポーネント・スケジューラ→ソフトウェアから複数DSA/複数FPGA間接続を効率よく使用可能・5Gネットワークによる仮想専用線通信を活用した三段構成の全体システム→暗号化によるセキュアなデータ通信

Crust-Core型再構成デバイス(複数 中規模デバイス)

AI-DB バッチ学習連携

Cloud Edge IoTDevice

認識処理

機械学習

最適化

匿名化処理

アクセラレータ

暗号化処理

様々な要求を持つデータ

パーソナルデータ

CrustVMM

ITOS

MECコントローラースケジューラ

仮想専用線通信(5G) ,遅延・帯域保証

大量のストリームデータ

学習データモデルレポジトリ

FPGA

DSA

FPGA

CPU

Switch

Core

DSA

FPGA

DSA

FPGA

MemoryCPU

Switch

Core

Sensor / Actuator

Crust-Core型再構成デバイス(小規模デバイス)

FPGA

DSA組込みRTOS

CrustVMM

準タイムクリティカル処理

ローカル通信、遅延・帯域保証

処理(MECコンポーネント)データ

操作

データフロー

IT OS

リアルタイムフィードバック(マイクロ秒)

MECコンポーネントによるシステムモデルからのプログラム生成

・ソフト/DSA/FPGAの区別無く表現→電力制約・リアルタイム性要求モデルによる最適化・処理をCloud/MEC/Edgeに自由に配置 →コンポーネント再利用による開発生産性向上

システムモデル例

・DNN推論処理のDSA/FPGAによる高エネルギー効率な実現→低消費電力エッジノードによるAI実行環境・大量のセンサデータを収集し効率よくバッチ学習用データを収集→高機能AI学習環境と低消費電力エッジAI実行環境の連携

タイムクリティカル処理

RTOS

ファームリアルタイムフィードバック(サブミリ秒)

省電力

mruby/C

ソフトリアルタイムフィードバック

(数百ミリ秒, ジッタ)

非リアルタイム

オンライン学習

Multi accessEdge (MEC)

クラウド

分散制御OS

スイッチ+細粒度再構成可能チップを新規開発

詳細はwebをご覧ください http://www.am.ics.keio.ac.jp/wp/links/crest-society5

初年度は、マルチFPGAシステムFiCをプロトタイプとして、ソフトウェア、アプリケーションを開発中→ 本日のデモ

![SIMフリースマートフォンneo.nuans.jp/files/NEOReloaded_Catalog_J.pdfNuAns NEO [Reloaded]を手にしてみると、その意外な軽さにも驚 くでしょう。厚くなってしまったのではなく、あえて薄さを追求せず、](https://static.fdocuments.fr/doc/165x107/5f56717798cbdb5c69024c97/simffffffffneonuansjpfilesneoreloadedcatalogjpdf-nuans.jpg)