Zhen LI RECONFIGURABLE COMPUTING …RESUME FRANCAIS 1. Introduction A l'ère de l'explosion des...

Transcript of Zhen LI RECONFIGURABLE COMPUTING …RESUME FRANCAIS 1. Introduction A l'ère de l'explosion des...

N° d’ordre : 2015-01 Année : 2015

THESE délivré par

L’ECOLE CENTRALE DE LYON

Spécialité : Electronique, micro et nano-électronique, optique et laser

Présentée et soutenue publiquement par

Zhen LI

Préparé à l’Institut des Nanotechnologies de Lyon (INL), UMR CNRS 5270

RECONFIGURABLE COMPUTING ARCHITECTURE EXPLORATION USING SILICON PHOTONICS

TECHNOLOGY

Ecole Doctoral E.E.A « Electronique, Electrotechnique, Automatique » de Université de Lyon

Sera soutenue le 28 janvier 2015 devant la Commission d’Examen Jury : M.Peter Bienstman Associate Professeur, Ghent University Rapporteur M.Lionel Torres Professeur, Univ.de Montpellier 2 Rapporteur M.Yannick Dumeige HDR, Univ.de Rennes 1 Examinateur M.Jacques-Olivier Klein Professeur, Université Paris-Sud XI Examinateur M.Sébastien Le Beux Maitre de conférence, ECL Examinateur Mme.Christelle Monat Maitre de conférence, ECL Examinateur M.Xavier Letartre Directeur de recherche, CNRS Examinateur M.Ian O'Connor Professeur, ECL Directeur de thèse

i

REMERCIEMENTS

Tout d’abord, je tiens à remercier Peter Bienstman et Lionel Torres pour avoir joué le

role essentiel de rapporteurs de cette thèse, en lisant avec sérieux et indulgence ce manuscrite

« double-disciplinaire ». Peter et Lionel a aussi contribué grandement non seulement à

l’amélioration de l’architecture je proposé, et encore à reconsidérer ce travail sous un autre

horizon. Je joins à ces remerciements Jacques-Olivier Klein et Yannick Dumeige pour avoir

ajouté des visions différentes à la variété des compétences de mon jury et aussi pour leurs

remarques, questions et conseils lors de ma présentation.

Les quatres personnes restant du jury ont contribué plus intensément à la réussite de

cette thèse, mon directeur de thèse Ian O’Connor, avec Sébastien Le Beux, Christelle Monat

et Xavier Letartre. Je tiens à exprimer ma profonde gratitude envers cette équipe

d’encadrement « fantastique » et « croisé le monde du système et du photonique », pour

m’avoir encadré, accompagné, conseillé et soutenu tout au long de ma thèse, pour leur aides

scientifiques, organisationnelles et énormément encouragements à défendre mes idées et

suivre le chemin je choisie, pour l’ensemble de nos échanges stimulants, de nos débats

agreables et passionants ainsi que pour ces nombreuses relecteurs de ce manuscrite.

Je voudrais remercier Guy Hollinger (directeur de l’INL), Catherine Bru-Chevallier

(directrice INL) et Christian Seassal (directeur adjoint INL, résponsable site-ECL) pour

m’avoir accueillie au sein de l’INL et m’avoir permis d’effectuer cette thèse dans ses murs.

Bien sûr, Xavier a joué un rôle essentiel qui est un peu comme « le roi physique »

dans ces traveaux de thèse. Combien de fois j’ai pu apprécier de discuter avec toi des

problèmes épineux et mes questions à la fois « informé » et « inprécisé », et l’ésprit prolifique

de sortir un solution élégant et satisfaite (plus qu’un compromis) pour des choses compliqués.

Souvent je me sens plutot comme jouer un petit jeu de raisonnement avec toi, avec les échos

« et alors » « et alors » « mais c’est bien sur » ou « on sent fou», on a trouvé finalment c’était

tout simple !… J’espère vraiment que je me montrerai aussi l’ésprit que toi dans ma carrière

de recherche de futur.

Egalement, Christelle est aussi joué un rôle comme « mère optique » dans mes

traveaux. Toujours vivant, jamais à dire « oui » facilement sans une réflexion profondu pour

ii

tous ce que je t’ai parlé et proposé, tu es toujours curieuse et passionné à apprendre les

nouveaux (plus que du côte physique, mais aussi du système), à décourir des petits choses

intéréssantes, à tenir les détails au cœur et pu faire le lien entre eux quand t’a besoin (par

exemple, pour me montrer les choses bizzares ou inraisonnables qui sont dans un coin caché

de ma thèse). Pour ces moments, le mieux je peux faire est de te dire « je ne sais pas, et je vais

le bien vérifier après ». Mais plus qu’une perfectionniste et parfois « exigente » en science, tu

es aussi très attentive et tolérante, je ne sais plus combien de fois je suis ému que tu tiens sur

ma position à considérer et/ou à montré un autre angle sur mes idées et mes traveaux. Tu es le

premier exemple du chercheur accompli qui me vienne à l’esprit.

Egalement, Sébastien prends le rôle comme « boss système ». C’est vraiment difficile

à croire que tu as des imaginations si riches et tu as pu inspirer des belles idées chaque fois

qu’on échange et discute. J’ai encore bien du mal à réaliser comment tu parviens d’avoir le

grande vue en même temps n’oublier pas tous les petites détails, parfois je ne sais pas

comment te faire plaisir quand tu m’a dit « c’est pas claire ». Mais ce qui est précieuse pour

moi, c’est tu m’as parlé souvent la difficulté sur ce sujet multi-disciplinaire qui est entre le

système et physique (la communication, la compromis), surtout quand on n’étais pas content

sur les résultats, ta tolérence et personnalité fait toi comme « mon frère ».

Et finalement j’ai eu la chance d’avoir Ian, le meilleur directeur de la thèse, cette thèse

n’aurait pas pu voir le jour sans l’implication de toi. Je n’a pas pu de trouver un mot ou une

phrase pour merci ton support, tes encouragements, tes idées, tes temps, ta

compherension…tu es le « père » de ma vie de la science.

Je tiens aussi à mentioner le plaisir que j’ai eu à travailler au sein de l’équipe

conception et l’équipe nanophotonique et j’en remercie ici tous les membres. Merci également

auxadministrateurs systèmes (Laurent Carrel et Rapheal Lopez) et aux secrétaires (Sylvie,

Patricia), qui font un travail formidable pour le labo.

Je passe ensuite une dédicace spéciale à tous les jeunes que j’ai eu plaisir de cotôyer

durant ces quelques années à INL, à savoir Felipe Frantz, Barakat Jean-Baptiste, Zhu Nanhao,

Feng Zhengfu, Yang Zhugeng, Sui Ning, Zhang Taiping, Meng Xianqing, Liu Huanhuan, Yin

Shi, Liu Qiang, Ding He, Li Hui, Guan Xin, Shi Liu… J’ai aussi voulu remercier ceux qui

sont déjà repartis qui m’a partagé des moments inoubliables dans la vie à Ecully, Tianli

Huang, Yu Zhang, Meng Jie, … Merci égalment à tous mes amis qui, bien que souvent à

iii

distance, m’ont soutenu au cours de cette aventure : Tang Qingshan, Ning Baozhu, Bing

jingyi, Shi Peiluo, Wang Weijia…

Enfin, je souhaiterais remercier l’ensemble de ma famille pour m’avoir soutenu

au cours de ma thèse, mon père, ma copine et mes frères et mes sœurs. Et merci maman

au ciel, tu m’appris heureux, courage, dignité, je sens ta presence chaque jours.

« Pour ma maman au ciel,

Le paradis est sous tes pieds »

v

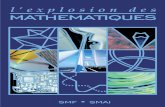

RESUME

Les progrès dans la fabrication des systèmes de calcul reconfigurables de type « Field

Programmable Gate Arrays » (FPGA) s’appuient sur la technologie CMOS, ce qui engendre

une consommation des puces élevée. Des nouveaux paradigmes de calcul sont désormais

nécessaires pour remplacer les architectures de calcul traditionnel ayant une faible

performance et une haute consommation énergétique. En particulier, optique intégré pourrait

offrir des solutions intéressantes. Beaucoup de travail sont déjà adressées à l’utilisation

d’interconnexion optique pour relaxer les contraintes intrinsèques d’interconnexion

électronique. Dans ce contexte, nous proposons une nouvelle architecture de calcul

reconfigurable optique, la « optical lookup table » (OLUT), qui est une implémentation

optique de la lookup table (LUT). Elle améliore significativement la latence et la

consommation énergétique par rapport aux architectures de calcul d’optique actuelles tel que

RDL (« reconfigurable directed logic »), en utilisant le spectre de la lumière au travers de la

technologie WDM. Nous proposons une méthodologie de conception multi-niveaux

permettant l'explorer l’espace de conception et ainsi de réduire la consommation énergétique

tout en garantissant une fiabilité élevée des calculs (BER~10-18). Les résultats indiquent que

l’OLUT permet une consommation inférieure à 100fJ/opération logique, ce qui répondait en

partie aux besoins d’un FPGA tout-optique à l’avenir.

vii

ABSTRACT

Advances in the design of high performance silicon chips for reconfigurable

computing, i.e. Field Programmable Gate Arrays (FPGAs), rely on CMOS technology and are

essentially limited by energy dissipation. New design paradigms are mandatory to replace

traditional, slow and power consuming, electronic computing architectures. Integrated optics,

in particular, could offer attractive solutions. Many related works already addressed the use of

optical on-chip interconnects to help overcome the technology limitations of electrical

interconnects. Integrated silicon photonics also has the potential for realizing high

performance computing architectures. In this context, we present an energy-efficient on-chip

reconfigurable photonic logic architecture, the so-called OLUT, which is an optical core

implementation of a lookup table. It offers significant improvement in latency and power

consumption with respect to optical directed logic architectures, through allowing the use of

wavelength division multiplexing (WDM) for computation parallelism. We proposed a multi-

level modeling approach based on the design space exploration that elucidates the optical

device characteristics needed to produce a computing architecture with high computation

reliability (BER~10-18) and low energy dissipation. Analytical results demonstrate the

potential of the resulting OLUT implementation to reach <100 fJ/bit per logic operation,

which may meet future demands for on-chip optical FPGAs.

ix

RESUME FRANCAIS

1. Introduction

A l'ère de l'explosion des données, les systèmes de calcul sont un facteur clé pour

l’innovation des technologies de l'informatique et de la communication. En raison des besoins

sans-cesse croissantes en puissance de calcul, en rentabilité économique, et en efficacité

énergétique, les méthodes traditionnelles reposant sur une évolution incrémentale des

architectures de calcul ne suffisent plus ; des nouveaux paradigmes de calcul s’appuyant sur

de nouvelles technologies sont désormais nécessaires pour relever les défis énergétiques et de

performance.

ITRS (the International Technology Roadmap for Semiconductors) prédit que les

interconnexions électriques ne seront plus capables de supporter les échanges de données

ultrarapides dans les systèmes de calcul parallèle (e.g. système sur puce multiprocesseurs,

MPSoC), du fait de leurs faibles efficacités énergétiques et de leur faible bande passante.

L’optique intégrée sur puce fait partie des alternatives susceptibles de répondre aux besoins

en vitesse et en faible consommation des circuits intégrés (IC), cela en leur conférerant

davantage de fiabilité. En effet, selon [12] and [17], l’optique permet d’augmenter la bande

passante, de diminuer la latence et la consommation associée aux interconnexions. De plus, la

compatibilité de l’optique avec les procédés de fabrication traditionnels CMOS permet de

réduire fortement les couts de développements et de fabrication tout en garantissant un accès

aux techniques d'assemblage hautement intégrés.

Au-delà de l'utilisation de la photonique sur silicium pour la réalisation

d’interconnexions dans les architectures multi-processeurs, cette technologie peut également

être exploitée pour effectuer des calculs en tout-optique, bénéficiant ainsi des avantages

intrinsèques de la lumière, cad une bande passante élevée et une consommation énergétique

plus faible. Cependant, il est illusoire de penser que l'optique peut directement concurrencer

l'électronique dans les système de calcul en raison de son immaturité technologique, qui induit

naturellement des problèmes d'intégration, de fiabilité et de coût de fabrication. Une première

étape consiste donc à rendre l'optique utile dans des fonctions de niche, cela afin d’améliorer

les futurs systèmes de calcul. Cela nécessite de repenser et d’imaginer de nouvelles

x

architectures de calcul adaptés à l’optique et capable de tirer profit de ses bonne propriété [3].

Une feuille de route permettant de développer des architectures de calcul exploitant l’optique

peuvent être résumés ainsi: a) le calcul doit rester autant que possible dans le domaine optique

afin de limiter l'utilisation d'interfaces électro-optiques couteuse; b) le spectre de la lumière

doit être utilisés via le multiplexage en longueurs d’onde (« wavelength division

multiplexing », WDM) afin de représenter et traiter l'information de manière efficace et

compacte; c) l’architecture optique doit être reconfigurable pour permettre plus de flexibilité

et d’adaptabilité selon les applications traitées; d) l'optique doit permettre d’améliorer

l'efficacité énergétique des systèmes de calcul.

Dans cette thèse, nous proposons une nouvelle architecture de calcul optique, la

« Optical LookUp table » (OLUT), qui est une implémentation optique de la Lookup table

(LUT). Les progrès dans la fabrication des systèmes de calcul reconfigurables de type « field

programmable gate arrays » (FPGA) s’appuient sur la technologie CMOS, ce qui engendre

une consommation des puces élevée. Dans la mesure où la technologie CMOS approche de

ses limites fondamentales, l’approche classique visant à densifier les ressources de calculs au

sein des FPGAs mènera à des puissances surfaciques élevées qui ne pourront être réduite que

par une limitation de l’activité. Continuer à réduire le nombre de pJ/bits avec chaque

génération de technologie n’est donc plus possible. La photonique sur silicium, quant à elle, a

le potentiel pour franchir cette barrière énergétique et augmenter le rapport

performances/puissance des FPGAs, permettant ainsi de réduire l'écart entre FPGAs et ASICs.

L'architecture OLUT proposée permet d’accélérer les calculs en utilisant le spectre de

la lumière au travers de la technologie WDM. Elle améliore significativement la latence et la

consommation énergétique par rapport aux architectures de calcul d’optique actuelles tel que

RDL (« reconfigurable directed logic »). Nous proposons une méthodologie de conception

multi-niveaux permettant l'explorer l’espace de conception et ainsi de réduite la

consommation énergétique tout en garantissant une fiabilité élevée des calculs (BER ~ 10-18).

Les résultats indiquent que l’OLUT permet une consommation inférieure à 100fJ par bit, ce

qui répondait en partie aux besoins d’un FPGA tout-optique.

Objectifs et plan de la thèse

Le travail décrit dans cette thèse a pur but d’aider à la conception d'une nouvelle

architecture de calcul reconfigurable reposant sur la photonique de silicium. Ce travail se situe

xi

à la frontière entre des domaines de la conception de systèmes de calcul et de la modélisation

de dispositifs photoniques. Le plan de cette thèse est le suivant:

Le chapitre 1 introduit les systèmes de traitement de l'information et offre un aperçu

des défis technologiques liés à l'utilisation de la technologie optique pour les communications

dans les systèmes sur puce électroniques. Il retrace ensuite l'évolution du calcul optique et

résumé les raisons de ses échecs pour sa diffusion. Enfin, ce chapitre identifie le rôle que

pourrait jouer l’optique dans les systèmes de calcul en tirant profit des ses bonnes propriétés.

Le chapitre 2 identifie les principaux types d'architectures de calcul existant et leurs

limites actuels ou à venir pour répondre aux défis de la réduction de la consommation

d'énergie et de l’augmentation de la puissance de calcul. Il présente ensuite les tendances

actuelles liées à l’utilisation des technologies émergentes pour la mise en œuvre des

architectures de calcul reconfigurables, tels que la technologie 3-D, les nano-mémoires et

l’optique. Un état de l’art portant sur les architectures de calcul optiques est ensuite adressé.

Le chapitre 3 décrit le principe de fonctionnement de l’OLUT. Dans un premier temps,

une implémentation optique équivalente à la LUT électrique est décrite. Nous montrons

ensuite comment le WDM est avantageusement utilisé pour réaliser des calculs en parallèles,

ce qui permet d’aboutir à une OLUT avec plusieurs sorties. Le principe de filtrage en

longueurs d’onde des OLUTs y est ensuite détaillé. Une évaluation préliminaire de gains

potentiels de l’OLUT est ensuite réalisée via l’exemple de l’additionneur complet 1-bit. Dans

la dernière partie, les sorties sont dupliquées afin de densifier plus encore les calculs. Cela est

réalisé par le biais de sorties complémentaire, qui permettent d’effectuer simultanément le

calcul d’une fonction logique et de son complément.

Le chapitre 4 propose une mise en œuvre des OLUTs reposant sur une technologie

photonique sur silicium existante. Il est consacré à la modélisation multi-niveaux de l’OLUT,

partant de sa brique de base principal qu’est un filtre « add-drop » contrôlé électriquement. Il

sert de base à l'évaluation des performances et de la consommation de l’OLUT au niveau du

système. Pour cela, la transmission du filtre « add-drop » est étudiée dans les régimes passifs

et actifs, cela en utilisant la théorie des modes couplés. Nous avons exploré plusieurs schémas

de modulation des signaux optiques sous la commande électrique, en prenant en compte les

porteurs au travers d’une jonction PIN. Les pertes optiques se produisant dans le layout du

circuit photonique du système OLUT sont ensuite étudiés. Enfin, le modèle d’énergétique

complet est décrit.

xii

Le chapitre 5 présente les résultats d’évaluation de performance de l’OLUT en

utilisant la méthodologie de conception multi-niveaux décrite dans le chapitre 4. Dans la

première partie, la consommation d’énergie de l’OLUT est évaluée en explorant l'espace de

conception des filtres « add-drop ». L'impact des dimensions d'entrée et de sortie d’OLUT sur

son efficacité énergétique est étudié. La deuxième partie quantifie les gains de l’OLUT avec

les sorties complémentaires sur les performances de calcul et l'efficacité énergétique. La

surface sur silicium et la puissance de laser optique d’entrée sont ensuite analysés.

Le chapitre 6 conclut la thèse et donne les perspectives de l’OLUT. En particulier, une

OLUT tout-optique reposant sur les interfaces d'entrée et de sortie tout-optique est proposée,

ce qui permet de passer à l’échelle et de traiter des fonctions de calcul plus complexes.

2. Utilisé la technologie optique dans les systèmes de calcul reconfigurables

Les solutions optiques ont été proposées pour réaliser les interconnexions sur puce et

les interfaces d'entrée/sortie (I/O) à haut débit, qui pourrait potentiellement influencer

significative le domaine de FPGA. Ils se concentrent sur l'augmentation de la bande passante

d'interconnexion en diminuant l'énergie par bit pour relaxer les limites intrinsèques imposées

par des pertes élevées dans les interconnexions électriques. Il a aussi promesse de rendre les

implémentations économique en tirant profit de bonne propriété de l’optique. Bien que ce ne

soit pas encore mature, des progrès importants continuent d'être reportés sur cette technologie.

Par exemple, Altera a démontré une interface optique en intégrant des lasers et des

photodétecteurs actuelle sur son FPGA en 2012. La figure 1 illustre l'architecture de ce FPGA

avec les interfaces optiques associées. Ce FPGA est intégré avec des sous-assemblées

d’émetteurs optiques (« TOSAS ») et sous-assemblées des récepteurs optiques (« ROSAS »),

tels que les liens de puce-à-puce entre les FPGAs peuvent être mise en œuvre au travers des

fibres optiques à haut débit au lieu de fils électriques. Cette interface optique donne un taux

de données maximum de 28Gbps sur le nœud de processus de 28nm, et probablement il peut

augmenter jusqu’au 40 Gbps sur le noeud de 22nm ou 14nm.

xiii

Fig.1 Une architecture de FPGA optique proposé par Altera[105]

La « Directed logic » (DL) est une architecture proposée pour réaliser du

« supercomputing » optique. Elle améliore la latence de calcul par rapport aux circuits

électronique en utilisant un réseau de commutateurs optiques interconnectés. L’architecture

DL a évolué avec les progrès technologiques récents de la photonique sur silicium, et en

particulier les modulateurs d’anneau silicium. Une preuve de concept reposant sur des

résonateurs en anneau en cascade a été démontrée expérimentalement. Des améliorations

significatives dans la reconfigurabilité et le passage à échèlle ont été apportées par

l’architecture reconfigurable DL (RDL). Une implémentation de l’architecture RDL

constitués d’une matrice 2 par 2 de interrupteurs a permit d’obtenir une vitesse de calcul de

0.5Gbits/s. Dans RDL, des fonctions logiques sont écrites sous la forme d’une somme de

produits, qui sont généralement implémentées dans le circuit photonique via un réseau

complet de type « cross-bar ». Ce circuit est constitué de micro-résonateurs électriquement

contrôlés, ce qui aboutit à des coûts d’implémentation relativement élevés et des

consommations énergétiques trop importantes. De plus, l’architecture RDL ne tire pas profit

du WDM, qui est pourtant un intérêt majeur de la photonique pour le calcul parallèle et

l’efficacité énergétique.

La capacité de calcul des FPGAs s’appuie sur la petite taille et le grand nombre de

LUTs. En électronique, une n-LUT prend n bits de donnée en entrée et fournit 1 bit de donnée

en sortie, c'est-à-dire qu’une seule opération est effectuée à chaque cycle. Plusieurs n-LUTs

doivent donc être mise en parallèle pour réaliser des calculs différents sur un même ensemble

d’entrées. Dans cette thèse, nous proposons une implémentation optique de la LUT, que nous

appelons OLUT. Au lieu de multiplexer des signaux électriques et de changer l’état de

transistors comme dans une LUT, l’OLUT route des signaux optiques au travers d’un réseau

de « démultiplexage » constitué de guides d’ondes et de commutateurs électro-optiques, selon

un chemin spécifié par les données d’entrée. En utilisant le WDM, une OLUT avec m

opérations (càd une n-m-OLUT) interface n bits de données d’entrée avec m bits de données

de sortie, en utilisant m signaux optiques aux longueurs d’onde distincts (λ0,..., λm-1), chacune

réalisant un calcul. De cette manière, les OLUTs permettent d’augmenter la capacité de calcul

par rapport aux LUTs traditionnelles, profitant ainsi des avantages de la technologie

photonique sur silicium.

3. Présentation de l’architecture de l’OLUT

De la LUT électrique à la LUT optique

xiv

Les OLUTs sont inspirées directement de la LUTs électriques. Une LUTà n entrées interface

n données d’entrée et 1 donnée de sortie à partir de la configuration stockée dans les 2n bits

de mémoire statique SRAM. Le calcul est réalisé en récupérant le résultat de l’opération

stockée dans la mémoire spécifique à laquelle on accède à partir de l’état des données d’entrée.

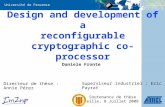

La Fig.2(a) montre un layout du circuit associé à une 2-LUT électrique. Il est construit à partir

de 4 bits de mémoire et d’un multiplexeur 4:1. Les LUTs sont utilisés dans les FPGA

électriques, en raison de leur temps de calcul constant et de leur capacité à réaliser toutes les

fonctions booléennes selon l'état de configuration des SRAM, ce qui conduit à la réalisation

d’architectures hautement flexibles et reconfigurables.

Le schéma d’une 2-OLUT qui fonctionne comme l’équivalent d’une 2-LUT électrique,

est présenté sur la Fig.2(b). La 2-OLUT utilise un signal optique à la longueur d’onde λ0,

comme l’équivalent d’une alimentation électrique. L’OLUT possède ses données d'entrée et

de sortie sous forme électrique. De façon similaire à la LUT électrique, l’OLUT est composée

de deux parties relativement indépendantes, qui sont dans le cas de la 2-OLUT :

1) La partie de routage : En fonction des données d’entrée électriques, un

ensemble de routeurs optiques interconnectés (pour une implémentation

possible, cf. la section suivante) for un réseau 1:4 de démultiplexage de

façon à acheminer le signal optique dans l’un des 4 guides d'ondes

horizontaux.

2) La partie de mémorisation : elle est composée de 4 filtres « add-drop »

contrôlés électriquement et interconnectés par 4 guides d’onde horizontaux,

Ce réseau produit le bit de donnée associé au résultat de l’opération

Booléenne effectuée sur les données d’entrée électriques. Comme pour les

LUTs électriques, la fonction booléenne exécutée dépend des bits de donnée

de configuration stockés dans les mémoires SRAM qui contrôlent l’état des

interrupteurs (ou filtres « add-drop »): un état logique «1» et logique «0»

dans la SRAM viennent respectivement commuter l’état de l’interrupteur

adjacent de façon à renvoyer l’état logique de sortie désiré jusqu’au photo-

détecteur (présence d’un signal optique : logique «1» et absence d’un signal

optique : logique « 0 »).

xv

0/1

y z0

λ0

λ0

λ0

λ0

D

SRAM Multiplexer

λ00/1

xy

Z0

xInput Data Input Data Output Data

Output Data

(b) Optical 2-LUT

SRAM

(a) Electrical 2-LUT

λ0 stage

0/1

0/1

0/1

Routing Memorization

λ00/1

λ00/1

λ00/1

0/10/1

y z0

λ0

λ0

λ0

λ0

D

SRAM Multiplexer

λ00/1 λ00/1

xy

Z0

xInput Data Input Data Output Data

Output Data

(b) Optical 2-LUT

SRAM

(a) Electrical 2-LUT

λ0 stage

0/10/1

0/10/1

0/10/1

Routing Memorization

λ00/1 λ00/1

λ00/1 λ00/1

λ00/1 λ00/1

Fig.2 Representation schematique d’une (a) 2-LUT electrique et (b) de l’OLUT équivalente.

Principe de base et l’opération du switch

Le composant clé de l’OLUT est le commutateur (ou filtre add-drop). Ces composants

permettent de sélectionner et de rediriger un signal optique en fonction de sa longueur d'onde.

Par souci de clarté, dans la figure 2, on utilise des symboles différents pour représenter les

routeurs optiques et les commutateurs optiques dans la partie de routage et de mémorisation,

respectivement, même si ces fonctions peuvent être physiquement implémentés par le même

composant optique, par exemple un filtre « add-drop » exploitant un micro-résonateur en

anneau (comme expliqué dans la section suivante). La pertinence de cette distinction

deviendra plus explicite lors de l'introduction de l'utilisation du WDM dans les architectures

OLUTs pour paralléliser les calculs.

Pour une géométrie et des paramètres matériaux donnés, le spectre de transmission

d’un filtre add-drop à micro-anneau est typiquement un peigne de raies qui peut être modifié

par un signal de contrôle, conduisant à la définition d’un état « Through » et d’un état

« Drop » :

« Etat Through»: la résonance du filtre add-drop (i.e. associé à un pic de transmission)

est désalignée spectralement avec la longueur d’onde du signal d’entrée, de sorte que le signal

optique continue sur le même guide d’onde, sans être perturbé par le filtre add-drop qu’il

croise.

«Etat Drop» : la résonance du filtre add-drop est alignée avec la longueur d’onde du

signal d’entrée, de sorte que ce dernier est redirigé du guide d’onde d’entrée vers le second

guide (dans l’exemple de la Fig.2, le guide orthogonal).

Le commutateur ainsi implémenté peut être considéré comme un routeur optique

spatial 1x2 contrôlé dynamiquement (i.e. le bloc de base dans la partie routage) ou bien

xvi

comme un interrupteur optique contrôlé statiquement qui peut changer la direction du signal

optique d’entrée en fonction de l’état de donnée stockée dans la mémoire adjacent (i.e. la

brique de base pour implémenter la partie de mémorisation). Noter que les cahiers des charges

pour ces deux fonctions sont cependant assez différents: le commutateur de la partie routage

doit pouvoir fonctionner en régime de modulation dynamique très rapide, pour être

compatible avec un débit de données (signale de contrôle) élevé, tandis que le commutateur

de la partie mémorisation n’impose aucune exigence sur la vitesse de modulation puisqu’il

fonctionne à l'état statique et n’est modifié que de manière ponctuelle si l’OLUT est

reconfigurée. Pour le reste du résumé, nous utilisons de manière équivalente le terme de filtre

«add-drop » pour désigner ces deux composants. Enfin, bien que le symbole choisi pour

représenter le commutateur optique ressemble à un micro-anneau, nous soulignons que cela

ne représente qu’un choix d’implémentation possible (probablement la plus mature

actuellement) pour construire les commutateurs composant l’architecture de l’OLUT.

1

0

0

0

0 1

0

AND

1

0

0

0

1 1

1

AND

D

1

λ0

λ0

λ0 0

0

0

λ0

1 1 1AND D

1

λ0

λ0

λ0 0

0

0

λ0

1 0 0AND

1

0

0

0

0 0

0

AND

D

1

λ0

λ0

λ0 0

0

0

λ0

0 0 0AND

1

0

0

0

1 0

0

AND

Electrical 2-LUT

2-1x2-OLUT

a) b) c) d)

e) f) g) h)D

1

λ0

λ0

λ0 0

0

0

λ0

0 1 0AND

1

0

0

0

0 1

0

AND

1

0

0

0

0 1

0

AND

1

0

0

0

1 1

1

AND

1

0

0

0

1 1

1

AND

D

11

λ0

λ0

λ0 00

00

0

λ0λ0λ0

1 1 1AND D

1

λ0

λ0

λ0 00

00

0

λ0

1 0 0AND

1

0

0

0

0 0

0

AND

1

0

0

0

0 0

0

AND

D

11

λ0

λ0

λ0 0

0

0

λ0

0 0 0AND

1

0

0

0

1 0

0

AND

1

0

0

0

1 0

0

AND

Electrical 2-LUT

2-1x2-OLUT

a) b) c) d)

e) f) g) h)D

11

λ0

λ0

λ0 0

0

0

λ0

0 1 0AND

Fig3. Example d’une fonction AND implementé par une 2-LUT et une 2-OLUT: (a-d) chemins d’entrée et sortie des données dans la 2-LUT pour différents scénarios de données d’entrée , (e-h) chemins corréspondants suivis par le signal optique pour la 2-OLUT.

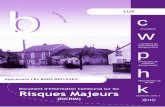

La figure 3 (a-d) illustre les chemins suivis par les données et les résultats obtenus en

sortie quand la LUT est configurée pour implémenter une opération logique « AND », un

signal de sortie associé à une logique « 1 » ou « 0 » est généré en fonction des signaux de

contrôle électrique, i.e. les données d’entrée. La Fig.3 (g-j) représente les scenarios

correspondants dans une 2-OLUT qui est configurée pour exécuter la même fonction logique

en utilisant un faisceau lumineux à la longueur d’onde λ0. Dans l’OLUTs, l’état logique de

sortie est obtenu selon que la lumière est présenté (scenario (e) : logique « 1 ») ou non

(scenario (f)-(h) : logique « 0 ») au niveau du photodetecteur positionné en haut de la colonne

de mémorisation. Pour plus de clarté, on représente les commutateurs en (hors) résonance, i.e

xvii

qui sont spectralement (des)alignés avec le signal optique incident par les contours des rings

en trait plain (pointillé).

Principe de fonctionnement de la n-m-OLUTs

Comme mentionné précédemment, en tirant le meilleur parti de la technologie

photonique silicium, l'utilisation du WDM est un vecteur fondamental pour la création

d’architectures de calcul puissantes. Bien que l’OLUT décrite sur la figure 2 (b) utilise un

signal optique à la longueur d'onde λ0 pour faire une seule opération, de manière équivalente

à une LUT traditionnelle, le WDM peut être avantageusement utilisé dans l’OLUT pour

réaliser des opérations logiques simultanées sur les mêmes données d'entrée. De cette façon,

l’OLUT permet potentiellement d'augmenter le rapport performance/consommation en

puissance par rapport à la LUT électrique.

Une OLUT avec m opérations (désigne si après n-m-OLUT) interface n bits de donnée

d’entrées électriques avec m bits de données de sortie, à l'aide de m signaux optiques aux

longueurs d'onde distinctes (λ0, ..., λm-1). Dans la partie de routage, les m signaux optiques λi

(i = 0 ... m-1) partagent le même chemin optique spécifié par les combinaisons des données

d'entrée électriques. Dans la partie de mémorisation, ils sont traités et routés successivement

dans m étages de mémorisation (représentés par m colonnes distinctes), composé chacun de 2n

filtres « add-drop » identiques et reliés entre eux par 2n guides d'ondes horizontaux. Chaque

étage de la partie de mémorisation exécute une fonction booléenne précise grâce à une

longueur d'onde spécifique, tous les étages fonctionnant en parallèle grâce au WDM. Un

exemple de 2-4-OLUT configuré pour exécuter simultanément les opérations logiques de ET,

OU, XOR et NXOR est illustré sur la figure 4. Dans cet exemple, les valeurs d'entrée x =

« 1 » et y =« 1 », redirigent, dans la partie routage, les signaux optiques vers le premier guide

d'onde en haut. Les signaux optiques sont ensuite routés sélectivement en fonction de leur

longueur d’onde, dans la partie de mémorisation, selon les états des commutateurs tels que

contrôlés par les configurations de SRAM. Chaque longueur d'onde continue ainsi sur le

même guide d'onde horizontal ou est sélectivement redirigé dans le guide d’onde vertical,

produisant une logique « 0 » ou « 1 » sur les sorties associées.

xviii

YX

1

Routing part Memorization part

1

1 1

1

1

0

0 1

0

0

0

1

0

λx

λx

D D D D

λ0

λ0

λ0

λ0

λ1

λ1

λ1

λ1 λ2

λ2

λ2

λ2

λ3

0 λ3

λ3

0 λ3

AND OR XOR Buffer

λ0λ1λ2λ3

Z0 Z1 Z2 Z3‘1’ ‘1’ ‘1’ ‘1’ ‘1’‘0’

λx

YX

1

Routing part Memorization part

1

1 1

1

1

0

0 1

0

0

0

1

0

λx

λx

D D D D

λ0

λ0

λ0

λ0

λ1

λ1

λ1

λ1 λ2

λ2

λ2

λ2

λ3

0 λ30 λ3

λ3

0 λ30 λ3

AND OR XOR Buffer

λ0λ1λ2λ3

Z0 Z1 Z2 Z3‘1’ ‘1’ ‘1’ ‘1’ ‘1’‘0’

λx

Fig.4 Représentation fonctionnelle d'une 2-4-OLUT configurée pour réaliser en parallèle 4 opérations logiques sur 4 longueurs d'onde distinctes.

Dans l'architecture de l’OLUT, le WDM est mis en œuvre à l'aide de deux schémas

distincts de filtrage en longueur d'onde (i) dans la partie de routage, où tous les signaux

optiques, indépendamment de leur longueur d'onde, se propagent le long du même chemin, et

(ii) dans la partie de mémorisation, où chaque signal optique (qui est spectralement distincte

des autres) est acheminé individuellement en fonction de la donnée de configuration. Pour

l'exemple de la 2-4-OLUT (Fig.4):

La partie de routage: Le comportement du commutateur dans la partie de routage est

illustré sur la Fig.5 (a) selon qu’il est dans l’état Drop (trait plein) ou dans l’état Through

(ligne pointillée). Les flèches représentent les quatre signaux optiques incidents pour lesquels

les longueurs d'onde λ0, λ1, λ2 et λ3 sont soit idéalement alignées avec les longueurs d'onde

de résonance du filtre add-drop (représentés par des pics dans le spectre de transmission) dans

l'état Drop, soit désaccordées avec un certain écart en longueur d'onde ∆λ dans l'état Through.

Les longueurs d'onde des signaux optiques injectés sont régulièrement espacées d’un écart

spectral correspondant au FSRx (« free spectral range ») du filtre add-drop. Ainsi, dans le cas

où le filtre « add-drop » est dans l'état DROP, tous les signaux sont redirigés vers un guide

d'onde donné, alors que dans l'état Through, tous les signaux se propagent le long de l'autre

guide d'onde.

La partie de mémorisation: Les Fig.5 (b) et (c) illustrent le fonctionnement des

filtres « add-drop » dans la partie de mémorisation ainsi que leur spectre de transmission. Par

rapport à ceux de la partie de routage, leur FSR est légèrement plus large (notés FSRm0 et

dans FSRm1 sur les Fig.5 (b) et (c)) de sorte qu’une seule longueur d'onde de résonance se

xix

trouve alignée avec l’une des longueurs d'onde des signaux optiques injectés: λ0 pour (b) et λ1

pour (c), respectivement. En outre, les FSRs des filtres add-drop constituant les différents

étages de mémorisations doivent être légèrement différents pour éviter le scénario indésirable

où les résonances des filtres « add-drop » se retrouveraient alignées par erreur avec la

longueur d'onde des autres signaux optiques après le processus de mise en accord/désaccord.

Des FSR différents et de longueurs d'onde de résonance distinctes pour les filtres add-drop

des différents étages de la partie de mémorisation peuvent être effectivement obtenus en

modifiant la géométrie du filtre (par exemple le rayon du micro-anneau) ou en utilisant un

contrôle thermique. Grâce à cette distinction, un seul signal est redirigé vers le guide d'onde

vertical lorsque le filtre « add-drop » est dans l'état Drop (trait plein), les autres signaux

continuant de se propager à travers le même guide d'onde, sans déviation. De manière

similaire au filtre add-drop utilisé dans la partie de routage, tous les signaux se propagent le

long du guide horizontal si le filtre « add-drop » est dans l'état Through (trait pointillé).

1λ0λ1λ2λ3λx

0

λx λ0λ2λ3

λ1

FSRx

λλ0 λ1 λ2 λ3

ON Resonance OFF Resonance

1

0

λ0

λ1λ2λ3

λ01

λ0λ1λ2λ3

λ00

FSRm0

λλ0 λ1 λ2 λ3

1

0

λ1

λ0λ2λ3

λ11

λ0λ1λ2λ3

λ10

FSRm1

λλ0 λ1 λ2 λ3

1

0

THROUGH

a) Router

b) λ0

λ1

Transmission Spectrum at Drop port

DROP

DROP

DROP

THROUGH

DROP

THROUGH

DROP

THROUGH

DROP

THROUGH

THROUGH

Memorization Stage

c)Memorization Stage

1λ0λ1λ2λ3

λ0λ1λ2λ3λx

0

λx λ0λ2λ3

λ1

FSRx

λλ0 λ1 λ2 λ3

ON Resonance OFF Resonance

1

0

λ0

λ1λ2λ3

λ01

λ0λ1λ2λ3

λ00

FSRm0

λλ0 λ1 λ2 λ3

1

0

λ1

λ0λ2λ3

λ11

λ0λ1λ2λ3

λ10

FSRm1

λλ0 λ1 λ2 λ3

1

0

THROUGH

a) Router

b) λ0

λ1

Transmission Spectrum at Drop port

DROP

DROP

DROP

THROUGH

DROP

THROUGH

DROP

THROUGH

DROP

THROUGH

THROUGH

Memorization Stage

c)Memorization Stage

Fig.5 Illustration du schéma de filtrage en longueur d’onde dans une 2-4-OLUT.

n-mx2-OLUT architecture

Pour maximiser les performances de calcul, on propose une architecture légèrement modifiée,

désigné ci-après la n-m×2-OLUT, qui calcule la fonction logique, et sa logique

complémentaire simultanément. La Fig.6 présente l’architecture d’une 2-1×2-OLUT avec deux

entrées. Le résultat du calcul de l’OLUT, tel qu'effectué par une 2-LUT électrique, est donné

xx

sur la sortie Z0. La 2-1×2-OLUT possède également une seconde sortie 0Z .sur laquelle le

résultat complémentaire de l’opération est calculé. La performance de calcul d’une OLUT

utilisant la sortie complémentaire est ainsi augmentée par rapport à l’OLUT présentée dans la

section précédente, avec un minimum de hardware supplémentaire (sans filtre add-drop, mais

simplement des virages et des fusions de guides d’onde supplémentaires dans ce cas simple).

De manière similaire à la n-m-OLUT, l’OLUT avec l’interface complémentaire utilise

le format électrique pour les données d'entrée et de sortie. La partie complémentaire de la n-

m×2-OLUT est ajoutée comme suit :

Partie complémentaire: Un guide d'onde vertical est utilisé pour acheminer les

signaux optiques des guides d'onde horizontaux de la partie de mémorisation vers les sorties

complémentaires. Des filtres add-drop optiques passifs sont utilisés pour filtrer les signaux

optiques en fonction de leurs longueurs d'onde, produisant ainsi le résultat complémentaire de

la fonction Booléenne ciblée qui est stockée dans la mémoire. On note que le même codage

de données des résultats est utilisé dans la partie complémentaire et la mémoire.

yx

0/1

Routing part Memorization part

0/1

0/1

0/1

λx

λx

λx

λ0

0z

z0D

λ0

λ0

λ0

λ0

Complementary part

Input Data Output Data

Output Data D

yx

0/1

Routing part Memorization part

0/1

0/1

0/1

λx

λx

λx

λ0

0z

z0D

λ0

λ0

λ0

λ0

Complementary part

Input Data Output Data

Output Data D

Fig.6 Illustration de l’architecture d’une 2-1×2-OLUT

La n-m×2-OLUT adopte le même schéma de filtrage en longueur d'onde que la n-m-

OLUT dans la partie de routage et de la mémorisation. Cependant, le filtrage dans la partie

complémentaire est réalisé en exploitant un filtre « add-drop » passif pour sélectionner les

signaux optiques sans aucun contrôle dynamique. La Figure 7 illustre le fonctionnement du

filtre « add-drop » passif dans la partie complémentaire. Comme pour la partie de

mémorisation, son FSR est légèrement plus large que l’écart entre les longueurs d'onde

adjacentes des signaux optiques incidents, de sorte qu’une seule longueur d'onde parmi celles

contenues dans le signal optique injecté se trouve alignée avec l'une des résonances du filtre

xxi

add-drop. L’utilisation de filtres « add-drop » passifs fixe les longueurs d'onde résonantes

pendant l’étape de conception, ce qui est suffisant puisque celles-ci n’ont pas besoin d'être

changées, même lorsque l'OLUT est reconfigurée pour effectuer d'autres opérations logiques.

λ2

λ0λ1

λλ0 λ1 λ2 λ3

1

0D

λ3

λ3

FSRi3

3ZDROP

THROUGHa) b)

λ2

λ0λ1

λλ0 λ1 λ2 λ3

1

0D

λ3

λ3

FSRi3

3ZDROP

THROUGHa) b)

Fig 7. L’opération de l’add-drop filtre dans un 2-4×2-OLUT: (a) Layout (b) spectre en longueur d’onde

L’architecture et le concept de l’OLUT présentés jusqu’ici pourraient être mises en œuvre

physiquement en utilisant diverses approches. Le choix de l’implémentation a d’ailleurs

certainement un impact sur la performance de l'architecture ainsi réalisée. Dans la section

suivante, nous proposons une implémentation physique spécifique de l’OLUTs, qui n’est

peut-être pas la solution optimale, mais qui tire avantage de la technologie photonique sur

silicium aujourd’hui mature.

4. L’implémentation physique de l’architecture de l’OLUT

Le fonctionnement de l'architecture de l’OLUT qui a été présenté impose certaines

contraintes physiques sur les caractéristiques des filtres « add-drop », tels que leur géométries

et leur facteurs de qualités Q. Ici, nous étudions comment la dimension du système, c’est à

dire le nombre d'entrées et de sorties, impacte la conception des filtres « add-drop » actifs

pour la mise en œuvre de l'architecture de l’OLUT électro-optique.

La Figure 8 représente le filtre add-drop commandé par l’intermédiaire d’une jonction

PIN. Cette dernière permet de modifier, par voie électrique, les propriétés optiques du micro-

anneau silicium. Le micro-anneau est couplé à deux guides d’onde silicium croisés. La diode

PIN est polarisé aux bornes des deux électrodes P+ et N+. Lorsque le filtre add-drop est

polarisé, la concentration de porteurs libres injectés dans l’anneau peut être de plusieurs

ordres de grandeur supérieur à la densité intrinsèque initiale.

xxii

Electrical Input V

OUT2

OUT1IN1λi

λx P+

V

N+

IN1 OUT1

OUT2

Resonator λx

(x=1…m)

(a) (b)

y

x

z

x

(c)

ring waveguide: 450nm x220nmSlab height: 50nmSpacing electrode with ring: 0.6µmP+/N+ doping: 1019 cm-3

i-region doping: 1015 cm-3

Electrical Simulation parameters:

Si slab-P+

Ring Electrode +V

Si slab-N+

Ground 0V

Si-i type

Electrical Input V

OUT2

OUT1IN1λi

λx P+

V

N+

IN1 OUT1

OUT2

Resonator λx

(x=1…m)

(a) (b)

y

x

y

x

z

x

z

x

(c)

ring waveguide: 450nm x220nmSlab height: 50nmSpacing electrode with ring: 0.6µmP+/N+ doping: 1019 cm-3

i-region doping: 1015 cm-3

Electrical Simulation parameters:

Si slab-P+

Ring Electrode +V

Si slab-N+

Ground 0V

Si-i type

Fig.8 Filtre « Add-drop »: (a) representation symbolique (b) layout (top-view), (c) layout simulé(cross-section) et des paramères du composant

Le nombre de canaux pouvant être traités par un tel dispositif, c'est-à-dire le nombre

maximum, m, de bits de sortis fournis par l’OLUT, est directement lié au FSR (Free Spectral

Range) du micro-résonateur. Pour une technologie laser basé sur les semiconducteurs III-V,

on peut considérer une largeur spectrale du gain de l’ordre de 100nm à 1.5µm (puits

quantiques InP). Le FSR doit donc être inférieur à 100/m nanomètres pour la réalisation d’une

n-m-OLUT. Comme le FSR est inversement proportionnel au rayon r de micro-anneau par la

relation gx rnFSR πλ 2/2≈ (ou ng est l’indice de groupe), r doit être plus grand que ~800m (nm)

(calculé pour λx ~1.55µm et ng ~4.3). En fait, un filtre add-drop avec un plus grand FSR peut

accueillir moins de bits de sortie, puisque chacun d'eux est associé à une longueur d'onde dans

la n-m-OLUT. Par exemple, les micro-anneaux comportant au moins 5 µm de rayon doivent

être utilisés pour mettre en œuvre une 2-6-OLUT, et ce rayon peut être diminué jusqu'à 1.7μm

pour une 2-2-OLUT. La dimension n-m de l’OLUT influe donc directement sur la taille du

filtre add-drop.

Transmissions d’un filtre «Add-drop »

Le mode de fonctionnement du filtre add-drop actif est résumé dans la Fig.9 (les équations

sont données par la théorie des modes couplées temporelle, CMT). Chaque scénario est

associé à une valeur logique destiné à OUT2, aux valeurs de transmission sur le port Through

et Drop, et les spectres de transmission correspondent à OUT2. En fonction de la longueur

d'onde de résonance initiale du dispositif par rapport à la longueur d'onde du signal d'entrée,

le filtre add-drop peut être configuré selon deux modes de fonctionnement :

xxiii

Mode A : Fig.9 a) et b) illustrent comment un signal optique injecté dans le port IN1 est

acheminé à travers le filtre add-drop actif lorsque ce dernier est dans l'un des deux états

(Through et Drop), et la table de vérité indique les valeurs des transmissions qui sont ciblés

pour les deux états contrôlés par la polarisation. Comme indiqué précédemment, lorsque la

diode est polarisée en direct, la densité de porteurs injectés dans la région intrinsèque

augmente fortement, ce qui conduit à un changement de l'indice de réfraction, cependant,

accompagné d’une absorption optique supplémentaire qui tend à réduire le rapport QL to Qc

et, par conséquent, dégrada la transmission T21 sur le port Drop quand V=Vop

Mode B : Alternativement, si nous assurons que le filtre add-drop est à l'état DROP

lorsqu’aucuns porteurs n’est injecté (nécessite un pré-calibrage), les signaux optiques peuvent

se propager sur le port Drop sans obtenir la perte d'absorption supplémentaire dans le

résonateur. Alors que l'add-drop est commuté dans l'état Through, les porteurs sont remplis

dans la région intrinsèque du résonateur en anneau. Toutefois, pour ce cas, le signal d'entrée

sera transmis directement au port Through, de sorte qu'il n’est pas couplé et ne subit donc

aucune d’absorption. Il est donc énergétiquement plus favorable d’utiliser le mode B plutôt

que le mode A. Si nous supposons que la résonance du filtre add-drop est configurée pour être

initialement alignée avec la longueur d'onde du signal incident λ i (i.e. ∆λ=0) en l'absence de

polarisation externe (V=0), on obtient 211 )/21()0( cL QQVT −== and 2

21 )/2()0( cL QQVT == . Dans

ce cas-la, l’expression QL est également différent de celui de la Mode A car il exclut le Qa

supplémentaire qui est apparu pour le Mode A quand V=Vop . Les colonnes c) et d) dans la

Fig.9 montre la propagation du signal optique et la table de vérité correspondant à cette

configuration. En comparant avec les valeurs de T21 atteint pour le mode A (voir Fig.9 (b)),

nous voyons que le problème de la réduction de la transmission par absorption de porteurs

dans le ring est évitée dans cette configuration.

Considération sur la vitesse pour les filtres add-drops électro-réfractifs

Le taux maximum de données pour un tel modulateur en anneau SOI sans polarisation en

inverse est limitée à 1 ~ 2 Gbit/s, comme indiqué par le temps de montée/descente de la

réponse du système qui peut être obtenu directement en résolvant les équations transitoires

dans une jonction PIN polarisé en direct (voir la section 4.2.2). La section 4.2.2 a également

mis en évidence que le max {temps de montée, temps de descente} était essentiellement

limité par la durée de vie des porteurs libres pour un guide d'onde SOI standard et ne peut être

réduite en utilisant une polarisation directe plus grande. Dans la même section, nous avons

relaté certaines démonstrations de fonctionnement au-delà de 12.5Gbit/s. Cependant ce

xxiv

régime nécessite l’implémentation de signaux électriques complexes et de tensions élevées,

peu compatible avec un circuit de contrôle CMOS de faible consommation.

a) Mode A (V=0) b) Mode A (V=Vop) c) Mode B (V=0) d) Mode B (V=Vop)

Signal propagati

on scenario

THROUGH

IN

V=0

OUT2

OUT1

IN2

THROUGH

IN

V=0

OUT2

OUT1

IN2

DROP

IN

V≠0OUT2

OUT1

IN2

DROP

IN

V≠0OUT2

OUT1

IN2

DROP

IN

V=0OUT2

OUT1

IN2

DROP

IN

V=0OUT2

OUT1

IN2

THROUGH

IN1

V≠0

OUT2

OUT1

IN2

THROUGH

IN1

V≠0

OUT2

OUT1

IN2 Targeted

Signal logic at OUT2

‘0’ ‘1’ ‘1’ ‘0’

T11 [ ] 1/2)/21(1

1 2

2

+∆

−−−

λλL

cL

QQQ 2)

//2//

(acic

acic

QQQQQQQQ

+++ 2)

/2/(

ic

ic

QQQQ

+

[ ] 1/2)/21(1

1 2

2

+∆

−−−

λλL

cL

QQQ

T21 [ ] 1/2

)/2(2

2

+∆ λλL

cL

QQQ

2)

//22(

acic QQQQ ++

2)/2

2(ic QQ+

[ ] 1/2

)/2(2

2

+∆ λλL

cL

QQQ

Spectrum

λ

λi

T21

λres λ

λi

T21

λres λ

T21

λres

λi

λ

T21

λres

λi

λ

λiT21

λres λ

λiT21

λres λ

λi

T21

λres λ

λi

T21

λres Fig.9 Fonctionnement du filtre add-drop actif selon les 2 modes opératoires A et B.

5. Méthodologie pour l’évaluation de la performance

Fig.10 illustre la méthodologie de conception. Idéalement, pour une application de calcul

donnée (par exemple un ALU ou un additionneur complet), notre approche commence avec

les spécifications au niveau architectural (notamment en ce qui concerne le nombre de OLUTs,

les dimensions des entrées et des sorties des OLUTs, ainsi que l'option complémentaire) et

passe ensuite progressivement jusqu'au niveau composant afin de concevoir un OLUT

fonctionnel. Les paramètres au niveau du dispositif incluent la taille (rayon de l'anneau), le

facteur de qualité et le décalage de longueur d'onde des filtres add-drop. Ces paramètres

seront utilisés pour évaluer les caractéristiques clés du dispositif optique en effectuant la

simulation physique (par exemple par FDTD), la simulation électrique et la modélisation avec

la théorie des modes couplés (CMT). Les caractéristiques des autres composants (par exemple,

les lasers et les photodétecteurs, ainsi que les guides d'onde) dans la boîte à outils

fonctionnelle utilisant la technologie photonique sur silicium sont extraits de la bibliothèque.

La configuration des données d'entrée et des mémoires différentes (indiquées par l'application

cible) sont considérés pour calculer la consommation d'énergie d'un seul bloc de OLUT.

xxv

L'analyse est réalisée en s'appuyant sur un taux d'erreur par bit (« BER ») donné et le résultat

est donné en termes d'énergie. Ceci permet d'élaborer l'espace de conception possible d'un

OLUT, représenté par le facteur Q et le décalage de la longueur d'onde du filtre d’add-drop.

L'efficacité énergétique optimale d'un OLUT est obtenue par une exploration automatisée de

l'espace de conception des paramètres des dispositifs optiques (par exemple des facteurs Q et

les décalages en longueur d'onde). Les autres caractéristiques de l’OLUT, tels que la

performance, la latence ou l’encombrement, peuvent également être évaluées en fonction des

paramètres physiques dans l'espace de conception. Après cela, nous montons de nouveau au

niveau du système: nous évaluons la performance et l'efficacité énergétique de l'architecture

selon diverses options de conception au niveau système tels que le nombre et la taille des

OLUTs et la topologie d'interconnexion (par exemple le nombre de guides d'onde et le

nombre des longueurs d'onde utilisées), ainsi que les caractéristiques de l'interface. Cependant,

au niveau système, l'exploration de l'espace de conception est actuellement un processus

manuel. Il a besoin d'être automatisé entre les résultats obtenus et les spécifications au niveau

système pour explorer les architectures alternatives, susceptibles de donner de meilleurs

résultats (par exemple, une meilleure efficacité énergétique) pour une application donnée. Une

telle exploration de conception nécessite des outils benchmarks (par exemple MCNC [117])

en tenant compte de l'avantage principal de l’OLUT, c'est à dire le calcul parallèle sur un

même ensemble de données. La mise en œuvre d'un tel outil fait partie des travails futurs.

Device level specification:r, ∆λ, Qc

System level specification:Number of OLUTs, n, m, complementary, etc.

Input data, configurationInput data,

configurationApplication (e. ALU, full

adder)

Application (e. ALU, full

adder)

PD, laser, waveguide losses, etc.

PD, laser, waveguide losses, etc.

Interconnect topology, interfaces

Interconnect topology, interfaces

Energy efficiency analysis

BER<10-18

Result:A functional and energy-efficient OLUT

Result:A functional and energy-efficient reconfigurable computing architecture

using silicon photonics technoloy

library libraryTest benchTest bench

Design Space Exploration

Design Space exploration

Device level specification:r, ∆λ, Qc

System level specification:Number of OLUTs, n, m, complementary, etc.

Input data, configurationInput data,

configurationApplication (e. ALU, full

adder)

Application (e. ALU, full

adder)

PD, laser, waveguide losses, etc.

PD, laser, waveguide losses, etc.

Interconnect topology, interfaces

Interconnect topology, interfaces

Energy efficiency analysis

BER<10-18

Result:A functional and energy-efficient OLUT

Result:A functional and energy-efficient reconfigurable computing architecture

using silicon photonics technoloy

library libraryTest benchTest bench

Design Space Exploration

Design Space exploration

Fig.11 Illustration d’une méthodologie de modélisation multi-niveau pour la conception d’une architecture de calcul photonique functionnelle et efficace en consommation énergétique, basée sur des OLUTs

xxv

L'analyse est réalisée en s'appuyant sur un taux d'erreur par bit (« BER ») donné et le résultat

est donné en termes d'énergie. Ceci permet d'élaborer l'espace de conception possible d'un

OLUT, représenté par le facteur Q et le décalage de la longueur d'onde du filtre d’add-drop.

L'efficacité énergétique optimale d'un OLUT est obtenue par une exploration automatisée de

l'espace de conception des paramètres des dispositifs optiques (par exemple des facteurs Q et

les décalages en longueur d'onde). Les autres caractéristiques de l’OLUT, tels que la

performance, la latence ou l’encombrement, peuvent également être évaluées en fonction des

paramètres physiques dans l'espace de conception. Après cela, nous montons de nouveau au

niveau du système: nous évaluons la performance et l'efficacité énergétique de l'architecture

selon diverses options de conception au niveau système tels que le nombre et la taille des

OLUTs et la topologie d'interconnexion (par exemple le nombre de guides d'onde et le

nombre des longueurs d'onde utilisées), ainsi que les caractéristiques de l'interface. Cependant,

au niveau système, l'exploration de l'espace de conception est actuellement un processus

manuel. Il a besoin d'être automatisé entre les résultats obtenus et les spécifications au niveau

système pour explorer les architectures alternatives, susceptibles de donner de meilleurs

résultats (par exemple, une meilleure efficacité énergétique) pour une application donnée. Une

telle exploration de conception nécessite des outils benchmarks (par exemple MCNC [117])

en tenant compte de l'avantage principal de l’OLUT, c'est à dire le calcul parallèle sur un

même ensemble de données. La mise en œuvre d'un tel outil fait partie des travails futurs.

Device level specification:r, ∆λ, Qc

System level specification:Number of OLUTs, n, m, complementary, etc.

Input data, configurationInput data,

configurationApplication (e. ALU, full

adder)

Application (e. ALU, full

adder)

PD, laser, waveguide losses, etc.

PD, laser, waveguide losses, etc.

Interconnect topology, interfaces

Interconnect topology, interfaces

Energy efficiency analysis

BER<10-18

Result:A functional and energy-efficient OLUT

Result:A functional and energy-efficient reconfigurable computing architecture

using silicon photonics technoloy

library libraryTest benchTest bench

Design Space Exploration

Design Space exploration

Device level specification:r, ∆λ, Qc

System level specification:Number of OLUTs, n, m, complementary, etc.

Input data, configuration

Input data, configurationInput data,

configurationApplication (e. ALU, full

adder)

Application (e. ALU, full

adder)

Test benchTest benchApplication Application Application Application

(e. ALU, full Application

(e. ALU, full (e. ALU, full (e. ALU, full (e. ALU, full (e. ALU, full adder

(e. ALU, full adder)

(e. ALU, full )adderadderadderadder)adder))

Application (e. ALU, full

adder)

PD, laser, waveguide losses, etc.

PD, laser, waveguide waveguide losses, etc.losses, etc.

PD, laser, waveguide losses, etc.

Interconnect topology, interfaces

Interconnect topology, interfaces

library

Interconnect Interconnect Interconnect Interconnect topology, topology, topology, topology,

interfacestopology,

interfacesinterfacesinterfacesinterfacesinterfaces

Interconnect topology, interfaces

Energy efficiency analysis

BER<10-18

Result:A functional and energy-efficient OLUT

Result:A functional and energy-efficient reconfigurable computing architecture

using silicon photonics technoloy

library libraryTest benchTest bench

Design Space Exploration

Design Space exploration

Fig.11 Illustration d’une méthodologie de modélisation multi-niveau pour la conception d’une architecture de calcul photonique functionnelle et efficace en consommation énergétique, basée sur des OLUTs

xxvi

Modèle d’énergie

Ici, nous examinons les principes de base pour re-clarifier la relation entre les

paramètres décrivant les filtres add-drop, et la consommation d'énergie pour l’OLUT, basée

sur l'effet électro-optique. Les équations et les valeurs constantes utilisées par le modèle sont

présentées dans la Fig.12. Nous rappelons ici que la consommation globale d'énergie de

l’OLUT EOLUT (i.e. energy-per-output-bit, donnée par l’équation (a) sur la figure) est la

somme des contributions suivantes:

i) Ed (cf. Equation (4.17)) représente l'énergie dynamique dissipée par les filtres add-

drop pour effectuer la transition d'état (Drop to Through), qui doit injecter des porteurs

pour régler la longueur d'onde de résonance;

ii) Es (cf. Equation (4.18)) représente l'énergie statique consommée par les filtres add-

drop et est déterminée par la polarisation électrique et le courant obtenu selon la

simulation électrique de la jonction PIN du résonateur micro-anneau en silicium;

iii) Elaser (cf. Equation (4.19)) représente la puissance optique minimum d'entrée

délivrée par le laser pour distinguer le niveau logique « 1 » du niveau logique « 0 »

(selon la dissipation de l'énergie laser dans la OLUT) pour atteindre un taux d'erreur

par bit acceptable (BER=10-18 est choisie ici).

iv) Epd est une estimation de l'énergie dissipée par chaque photodétecteur et est

quantifiée à 10fJ/bit pour une fréquence de 1 GHz

Comme indiqué précédemment, les paramètres nécessaires pour décrire complètement

l’opération d’un filtre add-drop sont : le facteur de qualité de couplage Qc ; le décalage en

longueur d’onde ∆λ entre la longueur d'onde de résonance et la longueur d’onde du signal

d’entrée ; et le facteur de qualité intrinsèque Qi. Comme Qi est généralement fixé pour une

technologie donnée et pour un rayon d'anneau donné, les transmissions du filtre add-drop dans

le régime actif sont ainsi exprimées selon les valeurs de Qc et ∆λ. De ce fait, on peut

construire l'espace de conception possible sur la base des valeurs du facteur de qualité de

couplage Qc, ainsi que du décalage de longueur d'onde ∆λ. Pour un nombre de bits d'entrée

donné n, et un nombre de bits de sortie donné m:

• Des valeurs plus élevées de Ed et Es sont nécessaires pour le fonctionnement du n-m-

OLUT pour un décalage en longueur d'onde ∆λ plus élevé, parce qu'il y a plus de

porteurs libres à injecter. Toutefois, les valeurs de Ed et Es sont indépendantes de Qc

xxvii

• Cependant, Elaser est inversement proportionnelle à la différence minimale entre les

valeurs de transmission pire cas pour les niveaux logiques « 1 » et « 0 » (1min and 0max

dans l'équation (b) dans la Fig.12) et s’appuie donc sur les valeurs de Qc et de ∆λ.

D'une part, pour un plus grand décalage en longueur d'onde ∆λ, une valeur élevée de

transmission sera généralement obtenue au port Through du filtre add-drop dans l'état

Through, facilitant ainsi la distinction des niveaux logiques «1» et « 0 », ce qui devrait

conduire à une valeur plus faible de Elaser , à utiliser pour les OLUTs. D'autre part,

comme indiqué par les expressions de transmission dans la Fig.12, pour une valeur

plus grande de Qc (ou plus précisément du rapport Qc/Qi), il est plus difficile

d'atteindre l'état Drop lorsque le filtre add-drop est éteint (puisque T12 devient plus

faible), mais il n'aide pas à atteindre l'état Through (où T11 augmente) car une

augmentation Qc conduit à une réduction de la largeur spectrale de la résonance. Ceci

implique que l'impact de la valeur de Qc sur celle de Elaser n'est pas toujours le même

et dépend de l'état du filtre add-drop (Drop ou Through), car c'est celui-ci qui

déterminera essentiellement la valeur de transmission dans le pire cas. Par exemple, si

la transmission dans l'état Through est inférieure que dans l'état-Drop, une valeur

inférieure de Elaser est nécessaire pour augmenter Qc. Inversement, Elaser augmente

avec Qc lorsque la transmission de l'état Through est plus élevée que celle de l'état

Drop.

Pour résumer brièvement, pour une technologie donnée et un rayon d'anneau fixe (Qi

constant), l'énergie dissipée dans l'OLUT (EOLUT) repose essentiellement sur les valeurs du

facteur de qualité de couplage Qc et le décalage en longueur d'onde ∆λ. La valeur optimale de

Eolut peut être réalisée à partir d'un compromis entre la dissipation de l'énergie des lasers et les

filtres add-drop, pour différentes valeurs de Qc et ∆λ. Pour étudier les rapports entre la

dissipation d'énergie et ces paramètres physiques et ainsi obtenir la valeur minimale de Eolut,

nous présentons le calcul de l'espace de conception possible du Qc et ∆λ pour l'architecture

d’une 2-2-OLUT dans la figure 12.

xxviii

pdlasersdcOLUT EEEEmnQE +++=∆ ),,,( λ

laserdd

cLaser PB

VmnQEη

λ =∆ ),,,(

a.

b. )01/( maxmin −∆= recvLaser PP

c. Vqtot25.0Ed(∆λ,n,m)← Esw~

Es( ∆λ,n,m)← Ps~ IV

∆N ← ∆λ←←

d.

Constants:Energy-per-output-bit (fJ/bit):

Data rate (B): 1Gb/s

Bit error rate (BER): 10-18

Epd = 10fJ/bite.

(fJ/bit)

Wavelength λ: 1.55µm

Detector frequency : 1GHz

[ ]

1111

221

2

2

11

2

))/2/(2()0(

1/2)/21(1

1)(

−−−− ++=

+==

+∆

−−−==

iacLQQQQ

QQVT

QQQVVT

ic

L

cLop

λλ

Transmissions:

pdlasersdcOLUT EEEEmnQE +++=∆ ),,,( λ

laserdd

cLaser PB

VmnQEη

λ =∆ ),,,(

a.

b. )01/( maxmin −∆= recvLaser PP

c. Vqtot25.0Ed(∆λ,n,m)← Esw~

Es( ∆λ,n,m)← Ps~ IV

∆N ← ∆λ←←

d.

Constants:Energy-per-output-bit (fJ/bit):

Data rate (B): 1Gb/s

Bit error rate (BER): 10-18

Epd = 10fJ/bite.

(fJ/bit)

Wavelength λ: 1.55µm

Detector frequency : 1GHz

[ ]

1111

221

2

2

11

2

))/2/(2()0(

1/2)/21(1

1)(

−−−− ++=

+==

+∆

−−−==

iacLQQQQ

QQVT

QQQVVT

ic

L

cLop

λλ

Transmissions:

Fig.12 Les équations de base et les valeurs constants utilisé dans le model

6. Conclusions et perspectives

L'architecture OLUT est indépendante de la technologie. Nous avons proposé une

mise en œuvre physique spécifique pour l'OLUT, ce qui pourrait ne pas être optimale mais

bénéficie de la maturité de la technologie de la photonique sur silicium. Dans cette mise en

œuvre, nous nous sommes concentrés sur la réalisation des OLUTs électro-optiques, où les

données d'entrée et de sortie restent dans le domaine électrique. Nous avons développé et mis

en œuvre un filtre add-drop à contrôle électrique basé sur micro-résonateur optique en anneau

qui répond aux besoins fonctionnels pour le routage et le filtrage des signaux optique à

différentes longueurs d'onde dans l'architecture de l’OLUT. L'inconvénient essentiel de cette

proposition est associé à l'approche électro-optique, qui a besoin de conversions optique-

électriques pour la mise en cascade des OLUTs. L'autre inconvénient majeur de ce choix est

que les micro-résonateurs en anneau de silicium sont des dispositifs sensibles à la température,

car la largeur spectrale des longueurs d'onde de résonance est étroite (~ 0,1 nm pour un Q ~

15, 000) et le silicium a un grand coefficient thermo-optique. Le contrôle de la température est

donc nécessaire pour maintenir l'état des résonateurs en anneau durant le fonctionnement des

OLUTs. En effet, dans un système photonique utilisant le WDM, le réglage de la longueur

d'onde est indispensable pour compenser la non-uniformité de fabrication. Ceci n'a pas été

pris en compte dans l'estimation de la consommation d'énergie pour l’OLUT dans le chapitre

5. Une autre limitation qui se pose au choix de la mise en œuvre spécifique est la limite de

vitesse à laquelle les interrupteurs électro-optiques (introduites dans le chapitre 4) peuvent

fonctionner. En effet, ces interrupteurs, construits sur la base d'une jonction PIN, s'appuient

sur l’injection de porteurs libres. Cependant, il existe de nombreux autres moyens

xxix

d’implémenter le filtre add-drop : par exemple le coupleur directionnel, les cristaux

photoniques ou l'interféromètre Mach-Zehnder. En plus, en considérant les progrès de la

technologie, des composants plus compacts et plus économes en énergie deviennent

disponibles. Il est à noter que la frontière de la photonique sur silicium évolue extrêmement

rapidement avec de nouveaux dispositifs intégrés reportés chaque année. Cependant, notre

travail de modélisation ne repose pas sur des nouvelles contributions dans les performances

du dispositif (vitesse, puissance ou efficacité). Au lieu de cela, nous nous sommes concentrés

sur l'étude de la façon dont certains dispositifs photoniques sur silicium devraient être conçus

pour l'architecture de calcul pour atteindre les exigences de performance au niveau du

système. Dans ce contexte, nous avons également proposé une approche de modélisation

multi-niveau basée sur l'exploration de l’espace de conception et des paramètres de

composant pour estimer la performance du système. Cette méthode nous permet d'étudier la

faisabilité de l'architecture OLUT et d'explorer l'espace de conception de dispositifs

photoniques pour réaliser des calculs fiables et efficaces dans les architectures OLUTs. Cette

méthode pourrait donc être étendue à l'évaluation de la performance des OLUTs s’appuyant

sur différentes implémentations physiques, simplement en changeant le modèle physique

utilisé au niveau de composant.

L'évaluation des performances pour les architectures de l'OLUT électro-optique a été

présentée en utilisant l'approche de modélisation multi-niveau et le modèle physique.

L'impact des dimensions d'entrée d’OLUT sur les paramètres des composants, et par

conséquent sur l'efficacité énergétique du système, est étudié par le calcul de l'espace de

conception possible pour les OLUTs. Les résultats analytiques ont montré le potentiel des

architectures de OLUT d'accéder au dessous de 100 fJ/opération logique, ce qui est en effet

comparable à la dissipation totale d'énergie par l’opération logique pour les dispositifs actuels

de CMOS en silicium (au niveau du femto Joule, selon ITRS [5]). En outre, nous avons

illustré le potentiel de l'architecture n-m×2-OLUT pour améliorer l'efficacité du matériel et de

l'énergie par rapport à la n-m-OLUT en utilisant la mise en œuvre d'une unité logique

arithmétique 1-bit (ALU). Les résultats d'analyse ont mis en évidence l'avantage clé des

sorties complémentaires pour augmenter la capacité de calcul d'une OLUT jusqu'à 100%,

avec un surcoût raisonnable sur la puissance du laser optique d'entrée et de la surface du

système. Cependant, il est bien de souligner que le modèle proposé n’inclut pas certaines

sources de dissipation d'énergie, qui devraient être pris en compte dans un environnement réel.

Il s'agit par exemple de la consommation d'énergie statique pour les lasers, de l'énergie

xxx

requise par les filtres add-drop de pré-calibration en temps réel et de réglage thermique. Ces

points feront l'objet de sujets de travail futur.

Pour compléter les perspectives de ce travail de thèse, nous avons proposé une version plus

avancée de l'OLUT pour compenser les faiblesses associées à la mise en cascade des OLUTs,

grâce à l'utilisation d'un filtre add-drop tout-optique. L'interface tout-optique proposée permet

de cascader plusieurs OLUTs ensemble pour construire éventuellement une architecture

FPGA tout-optique, éliminant ainsi la latence et la consommation d'énergie associée avec des

interfaces opto-électriques. Cette approche permettrait également de bénéficier de vitesses de

calcul potentiellement plus élevées, car le filtre add-drop tout-optique a un débit bien plus

élevés que celui des dispositifs électro-optiques introduits dans le chapitre 4.

xxxi

TABLE OF CONTENTS

REMERCIEMENTS ............................................................................................ I

ABSTRACT ..................................................................................................... VII

RESUME FRANCAIS ...................................................................................... IX

CHAPTER 1 INTRODUCTION ................................................................... 1 1.1 Background ...................................................................................................... 1 1.2 Lesson from the history of optical computing ................................................. 6

1.2.1 Early days of optical computing ......................................................................... 6 1.2.2 Golden Age of optical computing ....................................................................... 7 1.2.3 Lessons and observations ................................................................................... 8

1.3 Optics in computing: what next? ................................................................... 11 1.4 Objectives and thesis outline .......................................................................... 14

CHAPTER 2 EMERGING TECHNOLOGIES FOR RECONFIGURABLE COMPUTING ............................................................ 17

2.1 Emerging technologies for reconfigurable computing architectures ............. 17 2.1.1 Introduction to computing architectures .......................................................... 17 2.1.2 FPGA Overview ............................................................................................... 19 2.1.3 FPGAs challenges and emerging technologies ................................................ 21

2.1.3.1 Non-volatile nano-memory devices ............................................................. 22 2.1.3.2 3D technology .............................................................................................. 25 2.1.3.3 Optical technologies for reconfigurable computing ..................................... 27

2.2 State-of-the-art: Silicon photonics based computing architectures ............... 29 2.2.1 Background ...................................................................................................... 29 2.2.2 Directed Logic .................................................................................................. 29 2.2.3 Reconfigurable Directed Logic ........................................................................ 31

2.3 Conclusions .................................................................................................... 35

CHAPTER 3 OLUT ARCHITECTURE DESIGN AND IMPLEMENTATION ....................................................................................... 37

3.1 Single-output OLUT Architecture ................................................................. 37 3.1.1 From electrical LUTs to optical LUTs ............................................................. 37 3.1.2 Basic principle and switching operation .......................................................... 38