Fonctions logiques séquentielles bascules compteurs registres

Systèmes de logiques séquentielles-Bascules

-

Upload

hatem-jebali -

Category

Technology

-

view

48 -

download

5

Transcript of Systèmes de logiques séquentielles-Bascules

REPUBLIQUE TUNISIENNEMINISTERE DE L'ENSEIGNEMENT SUPERIEUR, DE LARECHERCHE SCIENTIFIQUE ET DE LA TECHNOLOGIE

DIRECTION GENERALE DES ETUDES TECHNOLOGIQUES

INSTITUT SUPERIEUR DES ETUDES TECHNOLOGIQUES

DE RADESDépartement Génie Electrique

LaboratoireSystèmes Logiques

TP5 : Systèmes de logiques séquentielles

Bascules

-Elaboré par : Jebali Hatem Dhrifi Zeineb

-Encadré par : Mr Azzouni Mourad

-Année Universitaire 2015/2016-

Sommaire

Rappel de cours.....................................................................................................4Manipulation.......................................................................................................15

La bascule RS...................................................................................................15I.1- Construction d’une bascule RS asynchrone à partir de fonctions logiques.........................................................................................................15I.1.1- Table de vérité.....................................................................................15I.2- Construction d’une bascule RS synchrone à partir de fonctions logiques.......................................................................................................................16Table de vérité :.............................................................................................16

La bascule D.....................................................................................................17II.1- Construction d’une bascule D à partir d’une bascule RS.....................17II.1. Table de vérité :....................................................................................17

La bascule JK :.................................................................................................18III.1- Construction d’une bascule JK...........................................................18III.1.1- Table de vérité..................................................................................18III.2- Construction d’une bascule JK Maitre-esclave...................................19III.2.1- Table de vérité :................................................................................19III.2.2- Le chronogramme :..........................................................................19

Recherche............................................................................................................20

I. Objectif : Distinguer la différence entre les systèmes combinatoires .et celles

séquentielles Etudier les fonctionnements de différentes bascules.

II. Prérequis : Système combinatoire, Simplification des fonctions logiques, Les circuits arithmétiques

III. Equipements : Maquette de simulations : KL-31001, Les modules : KL33008

Rappel de cours

Systèmes Séquentielles1. Définition :Un système est dit « Système séquentiel », lorsque son évolution ne dépend pas uniquement des informations données par ses variables d’entrée, mais aussi de l’état antérieur de chacune de ses sorties.

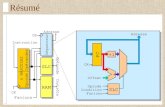

2. Modélisation :Un système séquentiel est identifié par la modélisation suivante :

Bascule « RS » Asynchrone 1. Définition :

Une bascule RS asynchrone est un système dont l’élément est une mémoire.Cette bascule est commandée par deux entrées S (Set : mise à 1) et R (Reset : remise a 0).L’action simultanée sur S et R engendre un état indéfini. N.B : La bascule « RS » est la seul bascule asynchrone existante.

2. Symbole:

S : entrée de mise à 1 ou d’enclenchement

R : entrée de remise à 0 ou de déclenchement

Remarque : l’action simultanée de R et S (R=S=1) est un état indéfini.

3. Etude d’une bascule RS : Table de vérité :

R S Qn Qn+1 Remarque0 0 0 0 µ0: Maintien a 00 0 1 1 µ1: Maintien a 10 1 0 1 ε : Enclenchement0 1 1 1 µ1: Maintien a 11 0 0 0 µ0: Maintien a 01 0 1 0 δ : Déclenchement1 1 0 0 Etat Indéfini1 1 1 0 Etat Indéfini

Tableau de Karnaugh :

RSQn 00 01 11

10

0 0 1 - 0 1 1 1 - 0

Qn=S +R.Qn

Logigramme :

Chronogramme :

Diagramme de fluence :

Le diagramme de fluence traduit la table de vérité simplifiée en un graphique composé par les deux états stables de la bascule (0) et (1) et les conditions d’évolution entre ces deux états.

Les Bascules SYNCHRONES

Dans ce mode, la variation de l’état de la sortie dans une bascule synchrone n’est possible qu’à la présence simultanée de signal de commande et du signal de synchronisation appelé HORLOGE (H), Clock (Cp, CLK) ou Timing (T).

Bascule « RS » Synchrone (RSH ou RST) :

1. Définition : Une bascule RSH est une bascule RS dont l’enclenchement et le déclenchement se sont autorisés qu’à la présence d’un signal de synchronisation. Ce dernier est dit signal d’horloge H.

L’action simultanée sur R et S à la présence de signal H, engendre un état indéfini.

2. Symbole:

3. Etude d’une bascule RSH : Table de vérité : ( même table que RS)

Logigramme :

Chronogramme :

Diagramme de fluence : (même diagramme que RS)

Bascule « JK » : Le terme bascule JK est inventé par le docteur ELDRED Nelson, un scientifique Américain.

La bascule JK est nommée en honneur de Jack Kilby ingénieur en électronique Américain.

1. Définition :La bascule JK Synchrone possède deux entrées et deux sorties complémentaires

J : entrée de mise à 1 ou enclenchement de la bascule. K : entrée de remise à 0 ou déclenchement de la bascule.

Cette bascule permet d’éliminer la condition indéterminée. Pour la condition J=K=1, la sortie Q de la bascule passe toujours à l’état complémenté à l’arrivée du front du signal d’Horloge H.

2. Symbole:

3. Etude d’une bascule JK : Table de vérité simplifiée :

J K Qn Qn+1 Remarque1 0 0 1 ε : Enclenchement0 1 1 0 δ : Déclenchement0 0 0 0 µ0: Maintien a 00 0 1 1 µ1: Maintien a 1

Tableau de Karnaugh :

JKQn 00 01 11 10 0 0 0 1 1 1 1 0 0 1

Qn+1= J.Qn + k . Qn

Logigramme :

Chronogramme :

Diagramme de fluence :

Bascule « D » :

1. Définition :La bascule D possède deux états stables, elle est commandée par une seule entrée D (Data). Cette bascule recopie le contenu de D sur Q chaque front d’horloge.

2. Symbole:

3. Etude d’une bascule D :

Table de vérité simplifiée :

D Qn Qn+ 1 Remarque 1 0 1 ε : Enclenchement 0 1 0 δ : Déclenchement 0 0 0 µ0: Maintien a 0 1 1 1 µ1: Maintien a 1

Logigramme :

Chronogramme :

Diagramme de fluence :

Bascule « T » :

1. Définition :La bascule « T » est déclenchée par le signal d’horloge « H », elle commandée par l’unique entrée « T ». La sortie « Q » change d’état à chaque impulsion du signal d’horloge et conserve son état le reste du temps.

N.B : La bascule « T » est un diviseur de fréquence quand elle est commandée par un signal d’horloge.

2. Symbole:

3. Etude d’une bascule D : Table de vérité simplifiée :

T Qn Qn+ 1 Remarque

0 0 0 µ0: Maintien a 0 1 0 1 ε : Enclenchement 0 1 1 µ1: Maintien a 1 1 1 0 δ : Déclenchement

Qn+1= T.Qn + T . Qn= T ⨁ QnChronogramme :

Diagramme de fluence :

Remarque : soit «T '» la période du signal d’horloge et « T ' '» celle de Q. On a alors T ' '=2*T '. Une multiplication par deux de la période « H » une division par deux de la fréquence de Q, donc la bascule T est un diviseur de fréquence .

Manipulation

La bascule RSI.1- Construction d’une bascule RS asynchrone à partir de fonctions logiques

I.1.1- Table de vérité

A4 A3 Qn Qn+1 Remarque 0 1 0 1 ε 1 0 1 0 δ 0 Ø 1 1 µ1

Ø 0 0 0 µ0

I.2- Construction d’une bascule RS synchrone à partir de fonctions logiques

I.2.1- Pour CLK=0, les entrées A1 et A2 n’interviennent pas (quel que soit les valeurs entrées, il n y’a pas une réponse du bascule)

I.2.2- Pour CLK=1,

Table de vérité :

CLK

SW0 SW1 L0 L1 Remarque

1 0 1 0 1 ε 1 1 0 1 0 δ 1 0 Ø 1 1 µ1

1 Ø 0 0 0 µ0

La bascule DII.1- Construction d’une bascule D à partir d’une bascule RS

II.1. Table de vérité : SW1 L0 L1 Remarque 1 1 0 ε 0 0 1 δ 0 0 1 µ0

1 1 0 µ1

Conclusion : Cette bascule (Data) recopie le contenu de SW1 (D) sur L0 (Q),

Chaque front d’horloge.

La bascule JK :III.1- Construction d’une bascule JK

III.1.1- Table de vérité

SW1 SW2 L0 L1 Remarque 1 Ø 1 0 ε : EnclenchementØ 1 0 1 δ : Déclenchement

0 Ø 0 1 µ0: Maintien a 0Ø 0 1 0 µ1: Maintien a 1

Conclusion : Quel que soit les valeurs changées par les deux interrupteurs, la bascule donne une réponse que à la présence du front de la signala d’horloge.

III.2- Construction d’une bascule JK Maitre-esclave

III.2.1- Table de vérité :

III.2.2- Le chronogramme :

La bascule JK divise le impulsions d’horloge par 2 lorsque J = K =1.

RechercheLes compteurs binaires

1- Introduction

L’élément de base du compteur est la bascule qui peut être de type D ou JK, montées en T.

Pour ce type de composants, au lieu de brancher des bascules discrètes pour constituer le compteur/décompteur recherché, les bascules qui les constituent, sont complètement encapsulées dans un même circuit intégré.

2- Exemples de références de compteurs binaires

Compteurs intégrés asynchronesTechnologie TTL 7493-74293-74393Technologie CMOS 4020-4024-4040

3- Etude du circuit TTL 7493A. Présentation

C’est un compteur binaires modulo 16 à deux étages, réalisé à partir de quatre bascules JK actives sur front descendant.

Le premier étage (DIV 2) est un compteur modulo 2, d’horloge CKA et de sortie QA. Le second (DIV 8) est un compteur modulo 8 d’horloge CKB et de sortie QB QC et QD.

77QSSSQSQS

Résumé

Un compteur est un circuit séquentiel comportant n bascules décrivant au rythme d’une horloge un cycle de comptage régulier ou quelconque d’un maximum de 2ncombinaisons.

Dans un compteur binaire chaque bascule divise par deux la fréquence d’horloge qui alimente son entrée CLK, avec ce genre de circuit, on peut diviser la fréquence initiale par n’importe quelle puissance de 2.

Le modulo d’un compteur est le nombre d’états occupés par ce dernier pendant un cycle complet. le modulo maximal d’un compteur à n bits est 2n .

Les diviseurs de fréquence sont des compteurs dont toutes les sorties ne sont pas utilisées. La division de fréquence dépendra de la sortie utilisée.

La remise à zéro peut être synchrone ou asynchrone. Dans le cas d’une RAZ asynchrone, la combinaison à appliquer à l’entrée ou aux entrées de remise à zéro est celle correspondante à la valeur immédiatement supérieure à la dernière valeur incluse dans l’intervalle de comptage.

Le 7490 est composé d’un diviseur par 2 et d’un diviseur par 8. Par mise en cascade, il permet une division par 16.

74LS93 : Fmax= 42MHz et Imax =9 mA 7493 : Fmax=40MHz et Imax=28mA