STi7105_PM

Transcript of STi7105_PM

-

8/9/2019 STi7105_PM

1/453

Preliminary Data

This is preliminary information on a new product now in development or undergoing evaluation. Details are subject tochange without notice.

August 2008 8137791 RevA 1/ 454

1

I n f o r m a t

i o n c l a s s i

f i e d C o n

f i d e n

t i a l - D o n o

t c o p y

( S e e

l a s t p a g e

f o r o

b l i g a t

i o n s

)

C

o n f i d e n t i a l

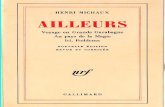

STi7105

Programming manual

IntroductionThis volume contains information to assist withprogramming of the peripherals and interfaces.This includes but is not restricted to the followingfunctional units:

– dual USB 2.0 host controller/ PHY interface– eSATA 1.0a with integrated PHY and SSC

support– gigabit ethernet controller (GMAC), with

GMII, RMII, MII, over-clocked MII (3x), andRevMII support– infrared/UHF transmitter/receiver interface

– soft modem support: MAFE or DAA– dual smartcard controllers and interfaces,

with clock generators to minimize externalcircuitry, ISO7816 compliant

– 17 GPIO ports (3.3V tolerant)– PWM4 with programmable frequency range

1 kHz to 8 kHz– four SSCs for I 2C/SPI master/slave

interfaces

– four ASCs (UARTs)– Interrupt level controller– front panel key scanning support

CP

ST40-300 core 400 MHz

UDI

32 K I cache

MMU

32 K D cacheLMI

DEI

S/PDIF

2-chPCM in

Digitalvideo in

DENC

4xSSC/I2C

4xUARTsILC

2x I/FSmCard

GPIOs PWM

MAFEinterface

IR Tx/RxUHF Rx

STBus

Main videodisplay

Audio L/R

TSmerger/router

Main/aux Displaycompositor and

Bdispblitter

6 DACsOutput

Analog videooutput

TMDS

USB

out

Clock genand

6-chPCM out

Peripheral I/Oand external interrupts

TS TS TS

systemservices

Aux videodisplay

Audio decoder

interfaces

AudioDACs

Delta Mu

2.0

16/32

DDR1

ST231

ST231core

Ethernet,MAC

MII/RMII/GMII

EMI EMPI

Digitalvideo

output 0

TMUs/INTC

CPU/FPU core

USB2.0

NSK DUALFDMA

KeyScan

out

Resets/ clocks/ modes

Serial ATAHDD, int/ext

IN1IN0 I/O

DVP

DualPTI

22

PDES

Sec

Video decoderAdvanced

TXT

(HD/SD)

PCI

DVO0 DVO1HDMI VTGs

pass through

stage

Digitalvideo

output 1

capture

FLASHNOR/NANDSFLASH

JTAG

players and

Comms

3

SWTS

iDTVversion

DualUSB 2.0

hosts

SPI

SerialFLASH

SystemsideDAA

Line sideDAA

SDRAMDDR2

TSIN2

e-SATAinterface

www.st.com

http://-/?-http://www.st.com/http://-/?-http://www.st.com/

-

8/9/2019 STi7105_PM

2/453

Contents STi7105

2/ 454 8137791 RevA

I n f o r m a t

i o n c l a s s i

f i e d C o n

f i d e n

t i a l - D o n o

t c o p y

( S e e

l a s t p a g e

f o r o

b l i g a t

i o n s

)

C

o n f i d e n t i a l

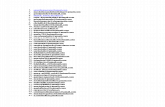

Contents

1 Preface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

1.1 References . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

1.2 Conventions used in this guide . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

2 External memory interface (EMI) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

2.1 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

2.2 EMI operating modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

2.3 EMI address map and memory space . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

2.4 EMI operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

2.4.1 Bank programming . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

2.4.2 Clock reconfiguration for synchronous interfaces . . . . . . . . . . . . . . . . . 142.5 Default/reset configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

2.5.1 Default/reset configuration for MPX boot . . . . . . . . . . . . . . . . . . . . . . . . 16

2.6 Peripheral interface (with synchronous flash memory support) . . . . . . . . 16

2.6.1 Synchronous burst flash support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

2.6.2 Operating modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

2.6.3 Burst interrupt and burst reiteration . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

2.6.4 Synchronous burst enable . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

2.6.5 Support for lower clock rates . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

2.6.6 Initialization sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

2.6.7 Use of flash memories in different banks with contiguous memory spaces22

2.6.8 Chip select allocation/bank configuration . . . . . . . . . . . . . . . . . . . . . . . 23

2.6.9 Address bus extension to low order bits . . . . . . . . . . . . . . . . . . . . . . . . 23

2.7 PCI interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

2.7.1 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

2.7.2 Master Functionality . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

2.7.3 Target Functionality . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

2.7.4 Host/Device configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

2.7.5 Boot Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

2.7.6 Master functionality operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

2.7.7 Target functionality operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

2.7.8 Configuration registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

2.7.9 Device configuration specific operation . . . . . . . . . . . . . . . . . . . . . . . . . 31

http://-/?-http://-/?-

-

8/9/2019 STi7105_PM

3/453

STi7105 Contents

I n f o r m a t

i o n c l a s s i

f i e d C o n

f i d e n

t i a l - D o n o

t c o p y

( S e e

l a s t p a g e

f o r o

b l i g a t

i o n s

)

C

o n f i d e n t i a l

8137791 RevA 3/ 454

2.8 NAND flash interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

2.9 SPIBOOT Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

2.9.1 DVB-CI /POD and ATAPI support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

2.9.2 HDD PIO mode support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

2.10 PC card interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 352.11 EMI buffer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

2.12 MPX interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

3 EMI registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

3.1 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

3.2 EMI subsystem register descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

3.3 EMI register descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

3.3.1 Configuration register formats for peripherals . . . . . . . . . . . . . . . . . . . . 48

3.4 EMI buffer register descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

4 EMI NAND flash support registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

4.1 EMI NAND flash addressing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

4.2 EMI NAND flash register summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

4.3 EMIBank register descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

5 PCI registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 82

5.1 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 825.2 PCI registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 84

5.3 PCI Host Function registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 98

5.4 PCI Configuration registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 101

6 USB 2.0 host (USBH) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 107

6.1 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 107

6.1.1 References . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 107

6.2 Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1076.2.1 STBus interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 109

6.2.2 Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 109

6.2.3 System Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 110

7 USB 2.0 host (USBH) registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 111

http://-/?-http://-/?-

-

8/9/2019 STi7105_PM

4/453

Contents STi7105

4/ 454 8137791 RevA

I n f o r m a t

i o n c l a s s i

f i e d C o n

f i d e n

t i a l - D o n o

t c o p y

( S e e

l a s t p a g e

f o r o

b l i g a t

i o n s

)

C

o n f i d e n t i a l

7.1 Base Addresses and Offsets . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 111

7.2 AHB Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 114

7.3 AHBPC Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 121

8 Serial ATA (SATA) subsystem . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 124

8.1 Introduction to the SATA subsystem . . . . . . . . . . . . . . . . . . . . . . . . . . . . 124

8.2 References . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 124

8.3 Key Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 125

8.3.1 PHY feature list . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 125

8.3.2 SATA Controller feature list . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 125

8.4 System overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 125

8.4.1 SATA host controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 125

8.4.2 DMA data transfers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 126

8.4.3 SATA PHY . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 126

8.5 Functional description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 126

8.5.1 Low power management . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 126

8.5.2 Interrupt management . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 127

8.5.3 Reset management . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 127

8.6 Clocking . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 127

9 Serial ATA (SATA) host . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 128

9.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1289.1.1 References . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 128

9.2 Host overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 129

9.2.1 Internal communication paths . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 129

9.3 Host functional description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 130

9.3.1 STBus Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 130

9.3.2 Transport layer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 131

9.3.3 Link layer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 131

9.3.4 Physical layer overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 133

10 Serial ATA (SATA) DMA . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 134

10.1 SATA DMA transfer types . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 134

10.1.1 Multi-block transfers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 134

10.1.2 Auto-reloading of channel registers . . . . . . . . . . . . . . . . . . . . . . . . . . . 139

10.1.3 Contiguous address between blocks . . . . . . . . . . . . . . . . . . . . . . . . . . 139

http://-/?-http://-/?-

-

8/9/2019 STi7105_PM

5/453

STi7105 Contents

I n f o r m a t

i o n c l a s s i

f i e d C o n

f i d e n

t i a l - D o n o

t c o p y

( S e e

l a s t p a g e

f o r o

b l i g a t

i o n s

)

C

o n f i d e n t i a l

8137791 RevA 5/ 454

10.1.4 Suspension of transfers between blocks . . . . . . . . . . . . . . . . . . . . . . . 140

10.1.5 Ending multi-block transfers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 140

10.2 Programming a channel . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 141

10.2.1 Programming examples . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 142

10.3 Disabling a channel prior to transfer completion . . . . . . . . . . . . . . . . . . 162

10.3.1 Abnormal transfer termination . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 163

11 Serial ATA (SATA) host registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 164

11.1 DMA controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 167

11.1.1 Channel . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 167

11.1.2 Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 179

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 182

11.1.3 Miscellaneous . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 191

11.2 SATA host controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19411.2.1 Shadow ATA/ATAPI . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 194

11.2.2 SATA . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 201

11.2.3 SATA host . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 207

11.3 AHB to STBus protocol converter registers . . . . . . . . . . . . . . . . . . . . . . 214

12 Ethernet subsystem . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 218

12.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 218

12.1.1 PHY connections . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 218

12.1.2 Interface support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 218

12.2 Ethernet subsystem features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 219

12.2.1 System Configuration Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 219

12.3 Ethernet I/O Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 220

12.3.1 MII Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 221

12.3.2 RMII (Reduced MII) Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 222

12.3.3 RevMII Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 224

12.3.4 GMII Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 225

12.4 Ethernet Subsystem Architecture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22712.4.1 STBus bridge . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 228

12.4.2 DMA block . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 228

12.4.3 MTL block . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 228

12.4.4 GMAC block . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 228

12.4.5 XMII block . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 228

http://-/?-http://-/?-

-

8/9/2019 STi7105_PM

6/453

Contents STi7105

6/ 454 8137791 RevA

I n f o r m a t

i o n c l a s s i

f i e d C o n

f i d e n

t i a l - D o n o

t c o p y

( S e e

l a s t p a g e

f o r o

b l i g a t

i o n s

)

C

o n f i d e n t i a l

12.5 DMA block . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 228

12.5.1 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 228

12.5.2 Initialization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 230

12.5.3 Transmission . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 230

12.5.4 Reception . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 234

12.5.5 Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 236

12.6 Descriptors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 236

12.6.1 Format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 236

12.6.2 Receive descriptors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 236

12.6.3 Transmit descriptors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 241

12.6.4 Alternate (Enhanced) Descriptor Structure . . . . . . . . . . . . . . . . . . . . . 245

12.7 MAC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 250

12.7.1 General Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 250

12.7.2 Transmission . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25012.7.3 Reception . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 252

12.7.4 RMII Block . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 256

12.7.5 MAC management counters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 256

12.7.6 Power Management block . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 257

12.7.7 Station Management Agent . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 260

13 Ethernet registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 262

13.1 Register addresses . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 262

13.2 GMAC control and status registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . 268

13.3 GMAC management counters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 284

13.4 DMA control and status registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 312

14 Programmable I/O port . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 328

14.1 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 328

14.1.1 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 328

14.1.2 Alternate functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 329

15 Programmable I/O port registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 330

16 Synchronous serial controller (SSC) . . . . . . . . . . . . . . . . . . . . . . . . . . 337

16.1 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 337

16.2 Basic operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 338

http://-/?-http://-/?-

-

8/9/2019 STi7105_PM

7/453

STi7105 Contents

I n f o r m a t

i o n c l a s s i

f i e d C o n

f i d e n

t i a l - D o n o

t c o p y

( S e e

l a s t p a g e

f o r o

b l i g a t

i o n s

)

C

o n f i d e n t i a l

8137791 RevA 7/ 454

16.2.1 Pin connection and control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 340

16.2.2 Clock generation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 341

16.2.3 Baudrate generation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 342

16.2.4 Shift register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 343

16.2.5 Receive data sampling . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 343

16.2.6 Antiglitch filter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 344

16.2.7 Transmit and receive buffers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 344

16.2.8 Loopback mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 345

16.2.9 Enabling operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 345

16.2.10 Master/slave operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 345

16.2.11 Error detection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 345

16.2.12 Interrupt mechanism . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 346

16.3 I²C operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 347

16.3.1 I²C control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34816.3.2 Clock synchronization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 350

16.3.3 START/STOP condition detection . . . . . . . . . . . . . . . . . . . . . . . . . . . . 351

16.3.4 Slave address comparison . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 352

16.3.5 Clock stretching . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 352

16.3.6 START/STOP condition generation . . . . . . . . . . . . . . . . . . . . . . . . . . . 353

16.3.7 Acknowledge bit generation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 354

16.3.8 Arbitration checking . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 354

17 Synchronous serial controller (SSC) registers . . . . . . . . . . . . . . . . . . 355

18 Asynchronous serial controller (ASC) . . . . . . . . . . . . . . . . . . . . . . . . 366

18.1 Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 366

18.1.1 Resetting the FIFOs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 366

18.1.2 Transmission and reception . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 366

18.2 Data frames . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 367

18.2.1 8-bit data frames . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 367

18.2.2 9-bit data frames . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 368

18.3 Transmission . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 369

18.3.1 Transmission with FIFOs enabled . . . . . . . . . . . . . . . . . . . . . . . . . . . . 369

18.3.2 Double buffered transmission . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 369

18.3.3 ASC_n_DIR . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 370

18.4 Reception . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 370

18.4.1 Hardware error detection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 371

http://-/?-http://-/?-

-

8/9/2019 STi7105_PM

8/453

Contents STi7105

8/ 454 8137791 RevA

I n f o r m a t

i o n c l a s s i

f i e d C o n

f i d e n

t i a l - D o n o

t c o p y

( S e e

l a s t p a g e

f o r o

b l i g a t

i o n s

)

C

o n f i d e n t i a l

18.4.2 Input buffering modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 371

18.4.3 Time out mechanism . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 372

18.5 Baudrate generation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 372

18.5.1 Baudrates . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 373

18.6 Interrupt control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 374

18.6.1 Using the ASC interrupts when FIFOs are disabled (double bufferedoperation) 375

18.6.2 Using the ASC interrupts when FIFOs are enabled . . . . . . . . . . . . . . . 377

18.7 Smart card operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 377

18.7.1 Control registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 378

18.7.2 Transmission . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 378

18.7.3 Reception . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 379

18.7.4 Divergence from ISO smart card specification . . . . . . . . . . . . . . . . . . 380

19 Asynchronous serial controller (ASC) registers . . . . . . . . . . . . . . . . 381

20 PWM and counter module . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 391

20.1 Programmable PWM function . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 392

20.2 Periodic interrupt generation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 393

20.3 Capture and compare . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 394

20.3.1 Capture function . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 394

20.3.2 Compare function . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 394

21 PWM and counter module registers . . . . . . . . . . . . . . . . . . . . . . . . . . 395

22 Modem analog front end (MAFE) interfaces . . . . . . . . . . . . . . . . . . . . 402

22.1 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 402

22.2 Using the MAFE to connect to a modem . . . . . . . . . . . . . . . . . . . . . . . . 402

22.3 Software . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 403

22.3.1 Data exchange . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 403

22.3.2 Control/status exchange . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 403

23 Modem analog front end (MAFE) interface registers . . . . . . . . . . . . . 404

24 Direct access arrangement (DAA) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 409

25 Integrated modem codec . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 410

http://-/?-http://-/?-

-

8/9/2019 STi7105_PM

9/453

STi7105 Contents

I n f o r m a t

i o n c l a s s i

f i e d C o n

f i d e n

t i a l - D o n o

t c o p y

( S e e

l a s t p a g e

f o r o

b l i g a t

i o n s

)

C

o n f i d e n t i a l

8137791 RevA 9/ 454

26 Remote controller interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 411

26.1 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 411

26.2 Functional description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 411

26.2.1 RC transmit code processor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 412

26.2.2 RC receive code processor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41326.2.3 Noise suppression filter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 414

26.3 Start code detector . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 414

26.3.1 Generation of subcarrier . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 415

26.3.2 Signalling rates and pulse duration specification for IrDA . . . . . . . . . . 415

26.3.3 Start code detection example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 415

27 Remote controller interface registers . . . . . . . . . . . . . . . . . . . . . . . . . 418

27.1 RC transmitter registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 420

27.2 RC receiver registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 425

27.3 Noise suppression . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 432

27.4 I/O control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 432

27.5 Reverse polarity . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 433

27.6 Receive status and clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 434

27.7 IrDA Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 436

27.8 SCD . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 439

28 Key scanner . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44528.1 Debounce . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 445

28.2 Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 445

28.3 Key scanner pads . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 446

29 Key scanner registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 447

List of registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 449

Revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 453

http://-/?-http://-/?-

-

8/9/2019 STi7105_PM

10/453

Preface STi7105

10/45 4 8137791 RevA

I n f o r m a t

i o n c l a s s i

f i e d C o n

f i d e n

t i a l - D o n o

t c o p y

( S e e

l a s t p a g e

f o r o

b l i g a t

i o n s

)

C

o n f i d e n t i a l

1 Preface

Comments on this or other manuals in the STi7105 documentation suite should be made bycontacting your local sales office.

1.1 References

ST231 Core and Instruction set architecture manual

This manual describes the architecture and instruction set for the ST231 cores.

ST40 Core architecture manual

This manual describes the architecture and instruction set for the ST40 core.

STi7105 datasheet

This document describes the pins, package, electrical characteristics and timing information

for the STi7105 device. It is intended for hardware engineers.

1.2 Conventions used in this guide

General notation

The notation in this document uses the following conventions:● sample code , keyboard input and file names● variables , code variables and code comments● screens , windows , dialog boxes and tool names● instructions

Hardware notation

The following conventions are used for hardware notation:● REGISTER NAMES and FIELD NAMES (NOT_SIGNALNAME for inverted signal).● PIN NAMES and SIGNAL NAMES.

The following abbreviations are used to represent register behavior:● W: write only,● R: read only,● RW: read/write,● Res: reserved,● R/LLU: read/linked list update.

http://-/?-http://-/?-

-

8/9/2019 STi7105_PM

11/453

STi7105 Preface

I n f o r m a t

i o n c l a s s i

f i e d C o n

f i d e n

t i a l - D o n o

t c o p y

( S e e

l a s t p a g e

f o r o

b l i g a t

i o n s

)

C

o n f i d e n t i a l

8137791 RevA 11/ 454

Software notation

Syntax definitions are presented in a modified Backus-Naur Form (BNF).● Terminal strings of the language, that is those not built up by rules of the language, are

printed in teletype font. For example, void .● Nonterminal strings of the language, that is those built up by rules of the language, are

printed in italic teletype font. For example,name

.● If a nonterminal string of the language starts with a nonitalicized part, it is equivalent to

the same nonterminal string without that nonitalicized part. For example, vspace-name .

● Each phrase definition is built up using a double colon and an equals sign to separatethe two sides (‘ ::= ’).

● Alternatives are separated by vertical bars (‘ | ’).● Optional sequences are enclosed in square brackets (‘ [ ’ and ‘ ] ’).● Items which may be repeated appear in braces (‘ { ’ and ‘ } ’).

http://-/?-http://-/?-

-

8/9/2019 STi7105_PM

12/453

External memory interface (EMI) STi7105

12/45 4 8137791 RevA

I n f o r m a t

i o n c l a s s i

f i e d C o n

f i d e n

t i a l - D o n o

t c o p y

( S e e

l a s t p a g e

f o r o

b l i g a t

i o n s

)

C

o n f i d e n t i a l

2 External memory interface (EMI)

The EMI is a general purpose external memory interface that allows the system to support anumber of memory types, external process interfaces and devices. This includes gluelesssupport for up to five independent memories or devices.

2.1 FeaturesThe main features include:● MPX mode support● 16-bit or 8-bit interface for FLASH, Burst-FLASH and peripherals. 32-bit MPX target

and initiator port● NAND FLASH interface● Serial FLASH interface● PCI interface

● support for up to five separately configurable external memory banks● EMI as either bus master or slave● retiming stage always enabled● five chip-selects (CSA, CSB, CSC, CSD, CDE)● port size (8 or 16 bits) for the boot defined by static mode pins sampled at the end of

the reset phase. Port size automatically set to 32 bits in case of boot from MPX.● no SDRAM support● address shifting in the padlogic present in previous products not supported● supports an HDD interface in PIO mode4 and a DVB-CI/POD interface via dedicated

signals.

The EMI memory map is divided into five regions (EMI banks). Address range 0x0000 0000to 0x07FF FFFF.

Bank boundaries are programmable between 4 MBytes and 64 MBytes. On RESET, theallocated memory space is divided into five regions of 16 MBytes each.

Each bank can only accommodate one type of device, but different device types can beplaced in different banks to provide glueless support for mixed memory systems.

The EMI is little endian. Bit positions are numbered left to r ight from the most significant tothe least significant. Thus in a 32-bit word, the leftmost bit, bit 31, is the most significant bitand the rightmost bit, bit 0, is the least significant.

The external data bus can be configured to be 8 or 16 bits wide on a per-bank basis, and isautomatically 32-bits wide for a bank configured in MPX mode.

,

http://-/?-http://-/?-

-

8/9/2019 STi7105_PM

13/453

STi7105 External memory interface (EMI)

I n f o r m a t

i o n c l a s s i

f i e d C o n

f i d e n

t i a l - D o n o

t c o p y

( S e e

l a s t p a g e

f o r o

b l i g a t

i o n s

)

C

o n f i d e n t i a l

8137791 RevA 13/ 454

2.2 EMI operating modesThe EMI can support the following device types, each one associated to different pinmappings:● Peripheral/SRAM● Asynchronous NOR-FLASH (ST, AMD, Intel types)● Synchronous NOR-FLASH● NAND-FLASH (large and small page boot, flex and advanced flex modes)● Serial FLASH (ST and Atmel types)● DVB-CI● ATAPI-PIO● PCI (host or device; configured on boot)

Refer to the STi7105 datasheet ‘Basic chip operating modes and multiplexing scenarios’ fordetailed information.

2.3 EMI address map and memory spaceThe EMI is allocated a 128 Mbyte memory region mapped onto five user configurablememory banks, plus a configuration space used to control the behavior of the EMI.

Following reset, the EMI is configured with 5 banks of 16 Mbytes.

The configuration address space is organized as shown in the EMI register summary.

Each EMI_BANK n (n = 0 to 4) contains a set of four 32-bit registers that are used toconfigure each bank depending on the type of device that is connected.

The type and organization of each set of bank registers depends on the value inDEVICETYPE ( EMI_CFG_DATA0 ) which defines the type of memory or device attached tothat bank.

The EMI supports nonmultiplexed address and data bus.

Each memory type and the associated control registers are described later in this chapter.

Table 1. Memory space

Address range Size (bytes) Function

Start End

0x0000 0000 0x00FF FFFF 16 Mbytes EMI Bank0(CS[0])

0x0100 0000 0x01FF FFFF 16 Mbytes EMI Bank1(CS[1])

0x0200 0000 0x02FF FFFF 16 Mbytes EMI Bank2(CS[2])

0x0300 0000 0x03FF FFFF 16 Mbytes EMI Bank3(CS[3])

0x0400 0000 0x04FF FFFF 16 Mbytes EMI Bank4(CS[4])

http://-/?-http://-/?-

-

8/9/2019 STi7105_PM

14/453

External memory interface (EMI) STi7105

14/ 454 8137791 RevA

I n f o r m a t

i o n c l a s s i

f i e d C o n

f i d e n

t i a l - D o n o

t c o p y

( S e e

l a s t p a g e

f o r o

b l i g a t

i o n s

)

C

o n f i d e n t i a l

2.4 EMI operationThe EMI is a highly flexible memory device which is able to support a large range of memorycomponents gluelessly. It accepts memory operations from the system and, depending onthe address of the operation, either accesses its internal configuration space or one of thepossible five external memory banks.

The position, size, clock frequency and memory type supported, is dependent on how theassociated control registers, EMI_BANKS[0:4], are programmed.

Following reset, all banks start with the same configuration which allows the system to bootfrom a large range of nonvolatile memory devices.

As part of the boot process, the user should program the EMI configuration registers tomatch the memory supported in that system, defining the memory size, the location in theaddress and the device type connected.

2.4.1 Bank programming

Refer to Section 2.6.8: Chip select allocation/bank configuration on page 23 for full bankprogramming details.

2.4.2 Clock reconfiguration for synchronous interfacesFollowing reset, the clocks for synchronous interfaces are disabled. This is due to the defaultreset assuming a memory which may be accessed asynchronously.

To access the synchronous memory, the user sets up the configuration state associated withthat bank. The user then programs the required clock ratio in the registerEMI_FLASH_CLK_SEL associated with that memory type.

The external clocks and associated clock dividers are then enabled by a write of 1 to registerEMI_MPX_CLK_SEL or EMI_FLASH_CLK_SEL , depending upon the device connected onthe board. Once enabled, any attempt to reprogram the clock ratios may have undefinedeffects.

2.5 Default/reset configurationFollowing reset, a default configuration setting is loaded into all five banks. This allows theEMI to access data from a slow ROM or FLASH memory. The default settings are detailed inTable 3 .

Table 2. Configuration registers

Address rangeFunction

Start End

0xFE70 0000 0xFE70 07FF EMI configuration

0xFE70 0800 0xFE70 0FFF EMI buffer0xFE70 1000 0xFE70 1FFF Nand configuration

http://-/?-http://-/?-

-

8/9/2019 STi7105_PM

15/453

STi7105 External memory interface (EMI)

I n f o r m a t

i o n c l a s s i

f i e d C o n

f i d e n

t i a l - D o n o

t c o p y

( S e e

l a s t p a g e

f o r o

b l i g a t

i o n s

)

C

o n f i d e n t i a l

8137791 RevA 15/ 454

The remaining configuration parameters are not relevant for an asynchronous boot; that isthe aim of the default configuration.

Figure 1. Default asynchronous configuration

Table 3. Default configuration for asynchronous boot

Parameter Default value

DATADRIVEDELAY 10 phases

BUSRELEASETIME 4 cycles

CSACTIVE Active during read only

OEACTIVE Active during read only

BEACTIVE Inactive

PORTSIZE Value of the signal EMI_PRTSZ_INIT

DEVICETYPE Peripheral

ACCESSTIMEREAD (18 + 2 = 20 cycles)

CSE1TIMEREAD 0 phases

CSE2TIMEREAD 0 phases

OEE1TIMEREAD 0 phases

OEE2TIMEREAD 0 phasesLATCHPOINT End of access cycle

WAITPOLARITY Active high

CYCLEnotPHASE Phase

BE1TIMEREAD 3 phases

BE2TIMEREAD 3 phases

EMIDATA(write)

EMIADDR

NOTEMICS

NOTEMIOE

EMIDATA(read) 10 phases

4 cycles

Read datalatch point

http://-/?-http://-/?-

-

8/9/2019 STi7105_PM

16/453

External memory interface (EMI) STi7105

16/ 454 8137791 RevA

I n f o r m a t

i o n c l a s s i

f i e d C o n

f i d e n

t i a l - D o n o

t c o p y

( S e e

l a s t p a g e

f o r o

b l i g a t

i o n s

)

C

o n f i d e n t i a l

2.5.1 Default/reset configuration for MPX boot

The default configuration is loaded into all six banks on reset.

2.6 Peripheral interface (with synchronous flash memorysupport)A generic peripheral (for example SRAM, EPROM, SFlash) access is provided which issuitable for direct interfacing to a wide variety of SRAM, ROM, flash, SFlash and otherperipheral devices.

Note: Refer to Section 2.6.8 on page 23 for specific STi7105 settings.

Figure 2 shows a generic access cycle and the allowable values for each timing field.

Table 4. Default configuration for MPX boot

Parameter Default value

BUSRELEASETIME 3 cycles

DEVICETYPE MPX

WAITSTATESREAD 3 cycles

WAITSTATESWRITE 3 cycles

WAITSTATESFRAME 1 cycle

EXTENDEDMPX ‘0’ (Hitachi compatible transfer size set)

WAITPOLARITY ‘0’ (Active high)

STROBESONFALLING 0 (strobes changing on rising edge)

MPXCLOCKRATIO “00” (full clock speed)

http://-/?-http://-/?-

-

8/9/2019 STi7105_PM

17/453

STi7105 External memory interface (EMI)

I n f o r m a t

i o n c l a s s i

f i e d C o n

f i d e n

t i a l - D o n o

t c o p y

( S e e

l a s t p a g e

f o r o

b l i g a t

i o n s

)

C

o n f i d e n t i a l

8137791 RevA 17/ 454

Figure 2. Generic access cycle

Separate configuration parameters are available for reads and writes. In addition, eachstrobe can be configured to be active on read, writes, neither or both.

Table 5. Strobe timing parameters for peripheral

Name Programmable value

ACCESSTIME 2 cycles + 0 to125 cycles

BUSRELEASETIME 0 to15 cycles

DATADRIVEDELAY 0 to 31 phases after start of access cycle

CSE1TIME Falling edge of CS. 0 to15 phases or cycles after start of access cycle

CSE2TIME Rising edge of CS. 0 to15 phases or cycles before end of access cycle

OEE1TIME Falling edge of OE. 0 to15 phases or cycles after start of access cycle

OEE2TIME Rising edge of OE. 0 to15 phases or cycles before end of access cycle.

BEE1TIME Falling edge of BE. 0 to15 phases or cycles after start of access cycle

BEE2TIME Rising edge of BE. 0 to15 phases or cycles before end of access cycle

LATCHPOINT0: End of access cycle.1 to 16: 1 to 16 cycles before end of access cycle.

Table 6. Active code settings

CS/OE/BE active code Strobe activity

00 Inactive

01 Active during read only

Read datalatch point

BUSRELEASETIME

Data drive delay

CSE1 time CSE2 time

OEE1 time

BEE1 time BE E2 time

ACCESSCYCLETIME

EMIADDR

NOTEMICS

NOTEMIOE

NOTEMIBE

EMIDATA(write)

EMIDATA(read)

OEE2Time

EMIRDNOTWRWrite

Constant high for reads

Constant high for reads

http://-/?-http://-/?-

-

8/9/2019 STi7105_PM

18/453

External memory interface (EMI) STi7105

18/ 454 8137791 RevA

I n f o r m a t

i o n c l a s s i

f i e d C o n

f i d e n

t i a l - D o n o

t c o p y

( S e e

l a s t p a g e

f o r o

b l i g a t

i o n s

)

C

o n f i d e n t i a l

2.6.1 Synchronous burst flash support

Burst mode flash accesses consist of multiple read accesses which must be made in asequential order. The EMI maps system memory operations onto one or more burst flashaccesses depending on the burst size configuration, operation size and the starting addressof the memory access.

The EMI supports the following memory devices:● AMD AM29BL162C,● ST M58LW064A/B,● Intel 28F800F3/ 28F160F3,● and any new part in these families with identical access protocol.

Table 7 provides a brief description and comparison of EMI-supported flash memories.

Note: Not all memory features are supported. Non-supported features are highlighted.

The EMI implements a superset of operational modes so that it is compatible with most ofthe main functions listed for the three flash families. The following sections contain a briefdescription of the EMI flash interface functionality.

10 Active during write only

11 Active during read and write

Table 6. Active code settings (continued)

CS/OE/BE active code Strobe activity

Table 7. ST/AMD/Intel flash features comparison

AM29BL162C STM58LW064A/B Intel28F800F3/28F160F3

Size 16 Mbits 64 Mbits 8/16 Mbits

Max (1) operatingfrequency

40 MHz 60 MHz 60 MHz

Data bus 16 bits fixed 16/32 bits 16 bits fixed

Mainoperations

Async single accesswriteSync burst readAsync single accessread

Async single access writeSync burst readAsync single access read

Async page readNot supported by EMI

Async single access writeSync burst readAsync single access readAsync page readNot supported by EMISync single access readNot supported by EMI

Burst size32 word partiallysupported by EMI:burst is interrupted

1-2-4-8 words (2) orcontinuous.Set by burst configurationregister. Continuous is not supported by EMI

4 to 8 words or continuousSet by read configurationregisterContinuous is not supported by EMI

http://-/?-http://-/?-

-

8/9/2019 STi7105_PM

19/453

STi7105 External memory interface (EMI)

I n f o r m a t

i o n c l a s s i

f i e d C o n

f i d e n

t i a l - D o n o

t c o p y

( S e e

l a s t p a g e

f o r o

b l i g a t

i o n s

)

C

o n f i d e n t i a l

8137791 RevA 19/ 454

Burst style (3) Linear burst -32 wordsSequential burstInterleaved burst (Notsupported)

Linear burstIntel burst (Not supported)

X-latency (4) 70-90-120 ns 7-8-9-10-12 (5) cycles 2-3-4-5-6 cycles

Y-latency (6) 1 cycle 1-2 cycles 1 cycle

Burst suspend/resume (7)

Yes via burst addressadvance(NOTEMIBAA) input

Yes via burst address advance(NOTEMIBAA) input No automatic advance

Ready/busypin (8) Yes (RD/BY) Yes (RD/BY) No

Ready forburst (9) No Yes (R) Yes (W)

1. The flash operating frequency, clock divide ratios and system frequency should be consistent with themaximum operating frequency.

2. A burst length of eight words is not available in the x 32 data bus configuration.

3. Modulo burst is equivalent to linear burst and sequential burst. Interleaved burst is equivalent to Intel burst.On AMD the burst is enabled by four async write operations. On ST and Intel the burst is enabledsynchronously via the burst configuration register.

4. X latency is the time elapsed from the beginning of the accesses (address put on the bus) to the first validdata that is output during a burst. For ST, it is the time elapsed from the sample valid of starting address tothe data being output from memory for Intel and AMD.

5. 10 to 12 only for F = 50 MHz.

6. Y-latency is the time elapsed from the current valid data that is output to the next data valid in output duringa burst.

7. In AMD and ST devices, BAA (or B) can be tied active. This means that the address advance during aburst is noninterruptable (Intel likewise). EMI assumes these pins are tied active and does not generate aBAA signal.

8. When the pin is low, the device is busy with a program/erase operation. When high, the device is ready forany read, write operation.

9. These signals are used to introduce wait states. For example, in the continuous burst mode the memorymay incur an output delay when the starting address is not aligned to a four word boundary. In this case await is asserted to cope with the delay.

Table 7. ST/AMD/Intel flash features comparison (continued)

AM29BL162C STM58LW064A/B Intel28F800F3/28F160F3

http://-/?-http://-/?-

-

8/9/2019 STi7105_PM

20/453

External memory interface (EMI) STi7105

20/ 454 8137791 RevA

I n f o r m a t

i o n c l a s s i

f i e d C o n

f i d e n

t i a l - D o n o

t c o p y

( S e e

l a s t p a g e

f o r o

b l i g a t

i o n s

)

C

o n f i d e n t i a l

2.6.2 Operating modes

Two different programmable read modes are supported:● asynchronous single read● synchronous burst mode (default four words length: configurable to 1, 2, 4 and 8 words)

using a specific lower frequency clock selected using register EMI_FLASH_CLK_SEL .

Note: 1 Continuous burst is not supported by the EMI.2 32-word burst size is partially supported by the EMI; the burst is interrupted when the

required data has been read.

3 Asynchronous page mode read is not supported by the EMI.

4 Interleaved burst mode is not supported by the EMI due to the implementation of multiplereads only using synchronous burst mode (feature provided by all three families of flashchips adopted).

The EMI supports an asynchronous single write.

The asynchronous single read/write uses the same protocol as that of the normal peripheralinterface.

Figure 3 shows a typical burst access with burst length of four words.

Figure 3. Synchronous burst mode flash read (burst length = 4)

The ACCESSTIMEREAD parameter is used to specify the time taken by the device toprocess the burst request. The rate at which subsequent accesses can be made is thenspecified by the DATAHOLDDELAY parameter, e1 and e2 delays can also be specified.

2.6.3 Burst interrupt and burst reiterationThe EMI interrupts the burst after the required amount of data has been read, thus makingthe chip select of the burst device inactive. This operation is allowed by all three families offlash devices (burst read interrupt for an ST device, standby for Intel, terminate current burstread for AMD). Due to this operation, the flash device puts its outputs in tri-state. If a newburst operation is then required, a new chip select and load burst address is provided(NOTEMILBA) to the memory chip.

NOTEMILBA

EMIDATA

EMIADDRA A

NOTEMIOE

NOTEMICS

EMIFLASHCLK

ACCESSTIMEREAD DATAHOLDDELAY

D + 1 D + 2 D + 3D D

NOTEMIBAA

http://-/?-http://-/?-

-

8/9/2019 STi7105_PM

21/453

STi7105 External memory interface (EMI)

I n f o r m a t

i o n c l a s s i

f i e d C o n

f i d e n

t i a l - D o n o

t c o p y

( S e e

l a s t p a g e

f o r o

b l i g a t

i o n s

)

C

o n f i d e n t i a l

8137791 RevA 21/ 454

If the flash interface is configured to a burst sequence of n bytes, and a burst read request ofm bytes is presented to the EMI on the STBus interface, there are three possible outcomes.1. n = m

The EMI performs one burst access during which it gets the exact number of words asrequested (see example A on Figure 4 with n = m = 8). Depending on the starting address,there is possibly a wrap that is automatically completed by the flash device. The wrap occurswhen the starting address is not aligned on an n-byte word boundary.

Figure 4. Burst on a flash with a single access

2. n > m

If the starting address is aligned on an m-byte word boundary, the EMI gets m bytes from asingle burst sequence as explained in the previous paragraph. Then the transfer on flash isinterrupted making the chip select inactive. This terminates the burst transfer and puts thememory device in standby mode, waiting for a new request and starting address for a newburst.

If the starting address is not aligned on an m-byte word boundary, a first burst on the flashexecutes until the m-byte word boundary is crossed. The burst on the flash is interruptedand there follows another burst with a starting address that wraps to an m-byte boundary(directly given by STBus interface) to read the remaining data. After all the required byteshave been read, the burst access on flash can be interrupted.3. n < m

The EMI needs to perform more burst accesses until it gets the required m words.

If the starting address is aligned on an n-byte word boundary, there are a series of flashburst accesses until the exact number of bytes is met.

If the starting address is not aligned on an n-byte word boundary, there is a first access onflash to read data until the n-byte word boundary is met. This access is then interrupted andnew series of accesses are star ted on a new address provided by STBus (that eventuallywraps at the m-bytes boundary). This is repeated until the exact number of bytes is reached.This happens in the middle of the last flash burst that is interrupted in the usual manner.

2.6.4 Synchronous burst enable

This operation is controlled by software and must only be performed when all otherconfiguration registers in the EMI have been programmed.

0 1 2 3 4 5 6 7

First burst

B)

A)0 1 2 3 4 5 6 7

Single burst

Start address = 0x0010B

Start address = 0x0000B

n = m = 8 words

Wrap to read last two bytes is automatically done by flash device

http://-/?-http://-/?-

-

8/9/2019 STi7105_PM

22/453

External memory interface (EMI) STi7105

22/ 454 8137791 RevA

I n f o r m a t

i o n c l a s s i

f i e d C o n

f i d e n

t i a l - D o n o

t c o p y

( S e e

l a s t p a g e

f o r o

b l i g a t

i o n s

)

C

o n f i d e n t i a l

Table 7 shows that for ST and Intel devices to operate in synchronous burst mode, theconfiguration parameters must be set in a special configuration register inside the memorydevice. The configuration software routine starts two asynchronous write operations foreach bank of burst memory, where address and data, respect precise configuration rules.However, for AMD the burst enable is performed by a sequence of four normalasynchronous writes.

2.6.5 Support for lower clock rates

Many SFlash devices operate in the 30 to 50 MHz clock range ( Table 7 ) whereas the EMIoperates up to a clock frequency of 100 MHz. To deal with this difference, the EMI can run ina lower speed mode. The hardware in the EMI needed for this mode forces accesses toalways start on the rising edge of the slower clock. It is up to the user to configure the otherEMI timings, to setup and latch, on the appropriate edge of this slower clock.

Figure 5. Half speed EMI SFlash clock

2.6.6 Initialization sequence

Peripheral interfaces are used immediately after reset to boot the device. Therefore, thedefault state must be correct for either synchronous or normal ROM. An SFlash device canbe interfaced to normal ROM strobes with the addition of only the address valid signal andthe clock. When the CPU has run the initial bootstrap, it can configure both the SFlashdevice and the EMI to make use of the burst features.

Note: The flash devices are in asynchronous read mode after reset.

Caution: The process of changing from default configuration to synchronous mode is not interruptible.Therefore the CPU must not be reading from the device at the same time as changing theconfiguration as there is a small window where the EMI configuration is inconsistent with thememory device configuration.

2.6.7 Use of flash memories in different banks with contiguous memoryspaces

As shown in Table 7 on page 18 , the maximum size of memory chip for SFlash is 64 Mbits.This may not be enough for some of the variants that use the EMI.

NOTEMILBA

EMIDATA

EMIADDR A

NOTEMIOE

NOTEMICS

CLK_EMI

EMIFLASHCLK

ACCESSTIMEREAD

A

D D+1 D+2 D+3

DATAHOLDDELAY

NOTEMIBAA

http://-/?-http://-/?-

-

8/9/2019 STi7105_PM

23/453

STi7105 External memory interface (EMI)

I n f o r m a t

i o n c l a s s i

f i e d C o n

f i d e n

t i a l - D o n o

t c o p y

( S e e

l a s t p a g e

f o r o

b l i g a t

i o n s

)

C

o n f i d e n t i a l

8137791 RevA 23/ 454

It is however possible to place two flash devices in different banks and have their memoryspace located contiguously in the overall address space. With this arrangement, the twoflash devices are seen the same way as a single, larger memory device from the softwarepoint of view.

This is done through the use of the bank reconfiguration capability, controlled through theEMI Buffer Registers.

2.6.8 Chip select allocation/bank configuration

Each of the five EMI banks can be configured separately to support different types ofdevices. There are restrictions on certain banks. The STi7105 provides five chip selects atits outputs, one per bank (NOTEMICSA, NOTEMICSB, NOTEMICSC, NOTEMICSD,NOTEMICSE).

2.6.9 Address bus extension to low order bits

The STi7105 EMI is able to use either 8- or 16-bit wide memory devices. Selection is donethrough field PORTSIZE of register EMI_CFG_DATA0 . The width of the boot bank isselected in hardware by the logic level to which mode pins MODE[8] are tied.

When using a 16-bit device, the low order address bit is on pin EMIADDR[1]. PinsNOTEMIBE[1:0] are byte selectors: bit [0] enables the low order byte and bit [1] enables thehigh order byte.

When using an 8-bit device, the low order address bit is on pin NOTEMIBE[1] (that is,NOTEMIBE[1] is a vir tual EMIADDR[0]). Pins NOTEMIBE[0] acts as byte enable.

2.7 PCI interfaceThe STBus-PCI bridge enables the EMI to support a PCI interface.

2.7.1 OverviewThe STBus-PCI bridge can be configured to be Host or Multi-Function Device by registeraccess and suppor ts both the Master and Target functionalities.

The PCI clock direction is controllable through register access.

http://-/?-http://-/?-

-

8/9/2019 STi7105_PM

24/453

External memory interface (EMI) STi7105

24/ 454 8137791 RevA

I n f o r m a t

i o n c l a s s i

f i e d C o n

f i d e n

t i a l - D o n o

t c o p y

( S e e

l a s t p a g e

f o r o

b l i g a t

i o n s

)

C

o n f i d e n t i a l

Host configuration

A PCI system with the STi7105 configured as a Host has the following connections:

Figure 6. Example of PCI system with STi7105 as a Host

Note: When the STBus-PCI bridge is operating as a Host, four PCI interrupts are available forexternal PCI agents.

Device configuration

A PCI system with the STi7105 configured as a Device has the following connections:

Figure 7. Example of PCI system with STi7105 as a Device

Note: When the STBus-PCI bridge is operating as a Device, it can generate one interrupt to theHost.

PCI bus

PCIbridge

STbus

reqgntint

Host

PCI

Device

Up to 4 lines,1 per Device

STi7105

PCI busSTi7105

PCIbridge

reqgntint

Host

PCI

Device

reset

http://-/?-http://-/?-

-

8/9/2019 STi7105_PM

25/453

STi7105 External memory interface (EMI)

I n f o r m a t

i o n c l a s s i

f i e d C o n

f i d e n

t i a l - D o n o

t c o p y

( S e e

l a s t p a g e

f o r o

b l i g a t

i o n s

)

C

o n f i d e n t i a l

8137791 RevA 25/ 454

2.7.2 Master Functionality

In the Master functionality, a part of the STBus address space is mapped on to the PCImemory space.

The STBus-PCI bridge generates the PCI frames on the PCI bus. When it is configured asDevice, the req/gnt protocol is used to get access to the PCI bus from the external Host.

Only memory frames can be generated by accessing to this address range. A specificmechanism handles IO and Configuration frames.

The base address with which the PCI frames are generated is software configurable. Thewindow size of the STBus address that is exposed onto the PCI address domain is alsosoftware configurable. A minimum of 1KBytes and a maximum of 1 GByte of contiguousmemory space can be mapped on to the PCI address.

Figure 8. shows the STBus address window mapped onto the PCI memory address andonto the configuration registers housed inside the STBus-PCI bridge.

Figure 8. Master Functionality: STBus address window on PCI memory space

The PCI Master functionality has the following limitations:● All the configuration and IO accesses are of one data cycle.● Fast back-to-back frames on PCI are not supported.

2.7.3 Target Functionality

The PCI Target functionality is implemented as a multi-function device. It supports up to8 functions, each function having its own configuration space.

The base addresses are defined in each configuration spaces to support a memory block,an I/O and a dual address cycle access so that the PCI interface can respond to 24 PCIaddresses (3 addresses per function).

Each PCI Target memory function occupy up to 256 MB of PCI memory map whose baseaddress are defined by the Host, as shown in the Figure 9. :

STBus Address, 4GB

STBus-PCI config,

Min 1KByte,

STBus Address window on PCImapped on STBus Window size

Max 1GByte

PCI Address, 4GB

and Base address

SW configurable

base address:EMISS_PCI_BRIDGE_REG

base address:PCI_MASTER

http://-/?-http://-/?-

-

8/9/2019 STi7105_PM

26/453

External memory interface (EMI) STi7105

26/ 454 8137791 RevA

I n f o r m a t

i o n c l a s s i

f i e d C o n

f i d e n

t i a l - D o n o

t c o p y

( S e e

l a s t p a g e

f o r o

b l i g a t

i o n s

)

C

o n f i d e n t i a l

Figure 9. Target Functionality: PCI address window on STBus memory space

A PCI frame access for any of the Target functions accesses a buffer defined within theSTi7105 memory space. The association of the buffer with the target function is softwareconfigurable. The process of accessing the destination buffers is called “buffer function” inthis document. A maximum of 8 buffer functions can be supported by the STBus-PCI bridge.Each buffer can be configured as a circular buffer and associated to an interrupt generatedwhen the buffer limit is reached.

The PCI Target function has following limitations.● Any of given buffer functions can be associated with either memory or IO, not both.● The PCI slave interface supports 8 functions, each function has one memory, one IO

and one dual address cycle addresses. This makes total of 24 functions in the PCItarget.

In the case of read function, the read latencies have to be met.

2.7.4 Host/Device configuration

The STi7105 is set by default to the Host configuration. The Device configuration can beselected by setting EMISS_CONFIG.PCI_HOST_NOT_DEVICE to ‘0’.

2.7.5 Boot Configuration

At power on reset, the STBus-PCI bridge is held at reset. The software is expected toprogram the boot configuration memory which defines the configuration space of the PCIinterface. The sequence for boot configuration memory initialization is as follows:● the boot configuration memory pointer is reset to zero by writing 0x00 into the register

PCI_BOOTCFG_ADD.● Then data is written into the register PCI_BOOTCFG_DATA.● the boot configuration memory pointer is incremented after each write access. This

facilitates updating the next location in the boot configuration memory without updatingthe pointer.

PCI Address, 4GB

up to 256 MB

PCI Address window on SystemMemory configured by the

mapped to

System Memory

depth of the buffer

SW configurable

(Memory or IO space)

each function

Space, 4GB

8 functions max

http://-/?-http://-/?-

-

8/9/2019 STi7105_PM

27/453

STi7105 External memory interface (EMI)

I n f o r m a t

i o n c l a s s i

f i e d C o n

f i d e n

t i a l - D o n o

t c o p y

( S e e

l a s t p a g e

f o r o

b l i g a t

i o n s

)

C

o n f i d e n t i a l

8137791 RevA 27/ 454

After updating the boot configuration memory, the reset is de-asserted by settingPCI_BRIDGE_CONFIG.PCI_RESET to ‘1’.

2.7.6 Master functionality operation

Address space

On reset a default 1KB of STBus address range, whose base address is defined asPCI_MASTER_base_address, is mapped on to the PCI address space. This can beincreased to a maximum of 1 GB through the register PCI_FRAME_ADD_MASK. Thefollowing rule must be ensured by software: If a bit ‘m’ is set to ‘1’, all the least significant bitstill ‘m’ have to be set to ‘1’. Not following this rule would result in the generation of PCIframes at the wrong addresses.

Memory accesses

The base address on the PCI memory map for which memory read or write frames have tobe generated, has to be written into the register PCI_FRAME_ADD. The unmasking bitshave to be set appropriately by writing the appropriate value into the registerPCI_FRAME_ADD_MASK.

The address of the generated PCI frame can be calculated by the following equation:pci_address = [STBus_address & PCI_FRAME_ADD_MASK] | [PCI_FRAME_ADD &~(PCI_FRAME_ADD_MASK)]

where:– the lowest 10 bits are inferred from the STBus address bits,– the bits 31 and 30 are inferred from the PCI_FRAME_ADD bits,– the other bits depend on the PCI_FRAME_ADD_MASK bit value: if the bit

PCI_FRAME_ADD_MASK.MASK_DISABLE[m] is set to ‘1’, the bit [m] is inferredfrom the STBus address bit [m] else if the bitPCI_FRAME_ADD_MASK.MASK_DISABLE[m] is set to ‘0’, the bit [m] is inferredfrom the PCI_FRAME_ADD bit [m]

as detailed in Figure 10. :

http://-/?-http://-/?-

-

8/9/2019 STi7105_PM

28/453

External memory interface (EMI) STi7105

28/ 454 8137791 RevA

I n f o r m a t

i o n c l a s s i

f i e d C o n

f i d e n

t i a l - D o n o

t c o p y

( S e e

l a s t p a g e

f o r o

b l i g a t

i o n s

)

C

o n f i d e n t i a l

Figure 10. Master Functionality: address translation

If all PCI_FRAME_ADD_MASK.MASK_DISABLE bits are set to ‘1’, then 1GB of the systemspace are mapped to the PCI space. It is the responsibility of the software to program thesebits depending on the system configuration.

IO and Configuration accesses

The PCI IO and config frames generated by the STBus-PCI bridge are of one data beat. Togenerate the IO or config frames, the address of the PCI IO or config frames has to bewritten into the register PCI_CSR_ADDRESS. The byte enables and command for theframe generated have to be written into the register PCI_CSR_BE_CMD. A read frame isgenerated by reading the register PCI_CSR_RD_DATA and a write frame generated bywriting into the register PCI_CSR_WR_DATA.

2.7.7 Target functionality operation

Memory and IO accesses

Each received IO or memory frames on the PCI interface generate transactions on theSTBus and are managed through a maximum of 8 buffers. Each of the supported bufferscan be uniquely associated to an IO or memory access on the PCI function space and hasone physical buffer on which storing or reading operations can wrap.

The buffer-function association is done by the sw during the configuration phase. There isno hw mechanism for managing any address range conflict functions.

The wrapping mode uses the buffer in a circular way. When the address exceeds the depthof the programmed buffer, it is re-initialized with the start address. Circular buffers areenvisaged in scenarios where the read throughput on the PCI target interface has to be met.

Buffer Initialization

The procedure for association of the buffer to the target function is described as follows:● Each of the buffer function has on physical buffers (usually defined in the external

memory) on which storing or reading operations can wrap. The address of these

select0 1

STBus addressPCI_FRAME_ADDRESS

PCI_FRAME_ADD_MASK

31 10 030 929

PCI address

reserved reserved

31 10 030 929reserved

0931 1030 29

31 10 030 929

http://-/?-http://-/?-

-

8/9/2019 STi7105_PM

29/453

STi7105 External memory interface (EMI)

I n f o r m a t

i o n c l a s s i

f i e d C o n

f i d e n

t i a l - D o n o

t c o p y

( S e e

l a s t p a g e

f o r o

b l i g a t

i o n s

)

C

o n f i d e n t i a l

8137791 RevA 29/ 454

buffers is written into the register PCI_BUFFADD0_FUNCn (‘m’ is the buffer numberand ‘n’ is function number).

● All the write frames received are posted, that is TRDY is asserted when the data isreceived by the PCI interface.

● For the read frames TRDY is asserted when the data is read from the physical buffer.● The buffer wrapping for the function ‘n’ is enabled by setting

PCI_BRIDGE_CONFIG.WRAP_ENABLE[n] = ‘1’.● The depth of the buffer (both the buffers have same depth) is written into the register

PCI_FUNCn_BUFF_DEPTH. The buffer depth has to be 2 k, that is, if a bit in the bufferdepth is set to ‘1’, all the LSB bits would be ‘0’.

● The PCI frame type associated to the buffer is defined in the registerPCI_FUNCn_BUFF_CONFIG.BAR_HIT field.

● The function-buffer association is defined in the registerPCI_FUNCn_BUFF_CONFIG.FUNC_ID field and the activation of the association inPCI_FUNCn_BUFF_CONFIG.FUNC_ENABLE bit.

Processing frames

If correctly initialized, the reception of the first PCI frame is using the buffer 0 information totransfer the content on the STBus: the address is translated using the content of thePCI_BUFFADD0_FUNC0. If there is no function-buffer association, a frame receptiondoesn’t generate any STBus transaction but an interrupt, if the interrupt is enabled.

The address of the generated STBus frame depends on the bit field, as shown in Figure 11. ,● the upper bits are inferred from the upper PCI_BUFFADD0_FUNCn register bits,● the lower bits are inferred from the lower PCI address bits,

the boundary between ‘lower’ and ‘upper‘ bits being defined by the position of the unique ‘1’allowed in the PCI_FUNCn_BUFF_DEPTH register bits.

The bottom bits of the STbus address can also vary as they are auto-incremented based on

the length of the burst generated by the PCI access.

http://-/?-http://-/?-

-

8/9/2019 STi7105_PM

30/453

External memory interface (EMI) STi7105

30/ 454 8137791 RevA

I n f o r m a t

i o n c l a s s i

f i e d C o n

f i d e n

t i a l - D o n o

t c o p y

( S e e

l a s t p a g e

f o r o

b l i g a t

i o n s

)

C

o n f i d e n t i a l

Figure 11. Target Functionality: address translation

The current buffer’s address pointer for the buffer function ‘n’ is available for read access inPCI_CURRADDPTR_FUNCn.CURR_ADDRESS field.

Interrupts

The interrupts are handled by 3 registers:● PCI_BRIDGE_INT_DMA_ENABLE for settings,● PCI_BRIDGE_INT_DMA_STATUS for status read operations,● PCI_BRIDGE_INT_DMA_CLEAR for de-assertion.

The standard interrupt corresponding to the function ‘n’ is enabled when the correspondingbit PCI_BRIDGE_INT_DMA_ENABLE.INT_FUNC_ENAB[n] is set to ‘1’. ReadingPCI_BRIDGE_INT_DMA_STATUS.INT_FUNC_STS[n] accesses to the interrupt flag andsetting PCI_BRIDGE_INT_DMA_CLEAR.INT_FUNC_CLR[n] to ‘1’ clears thecorresponding interrupts.

Two specific error cases are covered by dedicated interrupt enables:

If the bit PCI_BRIDGE_INT_DMA_ENABLE.INT_BRIDGE_UNDEF_FUNC_ENB is set to‘1’, an interrupt is asserted if a PCI frame is received attached to a function for which there isno associated buffer. The corresponding status bit is located inPCI_BRIDGE_INT_DMA_STATUS.INT_BRIDGE_UNDEF_FUNC_STS and the clear bit inPCI_BRIDGE_INT_DMA_CLEAR.INT_BRIDGE_UNDEF_FUNC_CLR.

All interrupts can be disabled by thePCI_BRIDGE_INT_DMA_ENABLE.INTERRUPT_ENABLE bit.

Received frame information

The register PCI_TARGID_BARHIT contains the target function ID (function spaceaddressed by the PCI frame) and the information if the PCI frame received was IO, memoryor dual address cycle.When an interrupt is asserted due to un-associated function, readingthis register helps in inferring the addressed function space and the type of the received PCIframe .

STBus address

PCI_BUFFADD0_FUNCn

PCI_FUNC0_BUFF_DEPTH

PCI address31 k 0k+1

auto-increment

31 k 0k+1

31 k-1 0k+1

31 k 0k+1

k000 10

depending onPCI burst length

http://-/?-http://-/?-

-

8/9/2019 STi7105_PM

31/453

STi7105 External memory interface (EMI)

I n f o r m a t

i o n c l a s s i

f i e d C o n

f i d e n

t i a l - D o n o

t c o p y

( S e e

l a s t p a g e

f o r o

b l i g a t

i o n s

)

C

o n f i d e n t i a l

8137791 RevA 31/ 454

2.7.8 Configuration registers

The standard Configuration registers are listed in Table 18.: PCI Configuration registerssummary

In Host mode, they are defined during the Boot Configuration phase (refer to Section 2.7.5:Boot Configuration ). They can be accessed anytime by: