Instructions Types dinstructions Séquencement Contrôle BUS SYSTÈME Registres Unité de Traitement...

-

Upload

fleurette-le-bras -

Category

Documents

-

view

110 -

download

0

Transcript of Instructions Types dinstructions Séquencement Contrôle BUS SYSTÈME Registres Unité de Traitement...

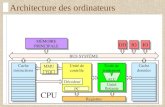

Instructions Types d’instructions Séquencement Contrôle

BUS SYSTÈME

RegistresRegistres

Unité deTraitement

Unité deTraitement

UnitéFlottante

Unité deContrôle

Unité deContrôle

Décodeur

PC

ALU

CPU

MÉMOIREPRINCIPALE

MÉMOIREPRINCIPALE IOIO IOIO IOIO

CacheDonnées

CacheInstructions

Contrôle de l’unité de traitement

UNITÉDE

CONTRÔLE

OENSELAL[2:0]SH[2:0]RA[2:0]RB[2:0]WENWA[2:0]3

3333

Z≠0

OENOEN SELSEL AL[2:0]AL[2:0] SH[2:0]SH[2:0] RA[2:0]RA[2:0] RB[2:0]RB[2:0]WENWEN WA[2:0]WA[2:0]

OPÉRATION OPÉRANDES

RA

WA

RBWEN

I0 I1

Z

SHIFTER

R0 R1 R2 R3 R4 R5 R6 R7

SH2SH1SH0

AL2AL1AL0

OENSEL

Z≠0

1 0

INPORTOUTPORT

33

3

Contrôle par instructions - Décodage

0:R1 4:R1,R3,R41:R0,R2 5:R2,R4,R22:R0,R3 6:R1,R13: 7:R2

0:AIN 4: CA&B1:BA 5: CA+B2:BA+1 6: BA>>13:NOP 7: OUTA

0:0|1 4:51:2 5:62:3 6:7|43:4 7:00:data inport

1:ocount 02:mask 13:while data ≠ 04:tempdata AND mask5:ocountocount+temp6:data data >> 1 end while7:outport ocount

SLCSLC

CKn BASCULES

Opcode Opérandes

n BASCULES

Opcode Opérandes

Fanions

RAMRAM

Contrôle

SLCSLCOpérandes

Instruction

Adresse

Chaque instruction doit permettre de générer les bits de contrôle pour l’unité de traitement ainsi que l’adresse de l’instruction suivante.

Format des instructions: exemple

Le codage des instructions est, en général, arbitraire:

OPCODE OPER1 OPER2 OPER3LOAD ADR, R1 0 0 0 Adresse[5:0] 0 0 1MOVE R0, R2 0 0 1 0 0 0 0 1 0 ø ø øINC R0, R3 0 1 0 0 0 0 0 1 1 ø ø øBRA ADR, COND 0 1 1 Adresse[5:0] data=0AND R1, R3, R4 1 0 0 0 0 1 0 1 1 1 0 0ADD R2, R4, R2 1 0 1 0 1 0 1 0 0 0 1 0SHR R1, R1 1 1 0 0 0 1 0 0 1 ø ø øBRA ADR, COND 0 1 1 Adresse[5:0] vraiSTORE ADR, R2 1 1 1 Adresse[5:0] 0 1 0

Compilationprogram toto;varA, B, C : array [1...1000] of integer;i : integer

begin...for i:=1 to 1000 do

C[i] := A[i] + B[i];...

end

program toto;varA, B, C : array [1...1000] of integer;i : integer

begin...for i:=1 to 1000 do

C[i] := A[i] + B[i];...

end

Algorithme

Langage de haut-niveau

Langage machine= jeu d’instructions

Algorithme

Langage de haut-niveau

Langage machine= jeu d’instructions

COMPILATEURCOMPILATEUR

...MOVE.L #2001,A0MOVE.L #3001,A1MOVE.L #4001,A2

START: ABCD -(A0),-(A1)MOVE.B (A1),(A2)

TEST: CMPA #1001, A0BNE START...

...MOVE.L #2001,A0MOVE.L #3001,A1MOVE.L #4001,A2

START: ABCD -(A0),-(A1)MOVE.B (A1),(A2)

TEST: CMPA #1001, A0BNE START...

Opération du processeur - Opcodes

Un processeur non-spécialisé (general-purpose) doit avoir un jeu d’instructions qui soit: Complet: il doit pouvoir exécuter toute fonction calculable; Efficace: il doit exécuter rapidement les fonctions les plus utilisées; Régulier: il doit contenir les fonctions attendues (p.ex., s’il y a un

décalage à gauche, il doit y avoir un décalage à droite); Compatible?: si nécessaire, il doit être compatible avec le jeu d’une

machine existante.

Tout algorithme est réalisé par une séquence (série) d’instructions.

Boucle de traitementDébutDébut

Instructionsen attente?

Instructionsen attente?

ChargementChargement

DécodageDécodage

Interruptionsen attente?

Interruptionsen attente?

TraitementTraitement

OUI

NON

NON

OUI

Les instructions sont stockées en mémoire, comme n’importe quelle donnée. À chaque instruction correspond donc un adresse.

Chaque instruction est chargée dans le processeur, décodée pour déterminer sa fonction et les bits de contrôle pour l’unité de traitement sont générés en conséquence.

L’unité de traitement effectue l’opération désirée sur les données.

Si une interruption est en attente, elle a normalement précédence sur les instructions, et elle est donc traitée immédiatement.

Types d’instructions - Opcode Transfert de données

Transferts d’informations entre positions mémoire (interne ou externe au processeur)

Arithmétique Opérations sur données numériques

Logique Opérations booléennes et autres

Entrées/sorties (I/O) Transferts d’informations entre le processeur ou la RAM et les

unités externes

Contrôle Instructions qui modifient le flot d’instructions

Format des instructions: exemple

data inport = LOAD ADR, R1 [T]ocount 0 = MOVE R0, R2 [T]mask 1 = INC R0, R3 [A]while data ≠ 0 = BRA COND, ADR [C]temp data AND mask = AND R1, R3, R4 [L]ocount ocount + temp = ADD R2, R4, R2 [A]data data >> 1 = SHR R1, R1 [L]end while = BRA 1, ADR [C]outport ocount = STORE ADR, R2 [T]

Format des instructions

Beaucoup d’information! P.ex., une architecture avec 256 instructions, 16 fanions, 64 registres et un bus (adresse) de 32 bits aurait besoin, même si tous les opérandes sont des registres (ce qui n’est pas le cas), de

8 + 4 + 6x3 + 32x2 = 94 bits!

Une solution est de coder les instructions sur plusieurs mots mémoire.Ce fut une technique très utilisée dans le passé (processeurs 8 et 16 bits) et le reste aujourd’hui pour certains types d’instructions. Elle introduit cependant beaucoup de délai (plusieurs coups d’horloge par instruction, décodage complexe).

Des simplifications sont nécessaires!

OpcodeOpcode ConditionsConditions Opérandes (3)Opérandes (3) Prochaine(s) instruction(s)Prochaine(s) instruction(s)

Format des instructions - Simplifications

Première simplification: chaque type d’instruction nécessite des informations différentes.

Transferts de données: 78 bits (un opérande peut être une adresse)

Opérations arithmétiques et logiques: 58 bits (que des registres)

Opérations d’entrée/sortie: 78 bits (un opérande peut être une adresse)

Instructions de contrôle: 76 bits

OpcodeOpcode Opérandes (2)Opérandes (2) Prochaine instructionProchaine instruction

OpcodeOpcode Opérandes (3)Opérandes (3) Prochaine instructionProchaine instruction

OpcodeOpcode Opérandes (2)Opérandes (2) Prochaine instructionProchaine instruction

OpcodeOpcode ConditionsConditions Prochaine(s) instruction(s)Prochaine(s) instruction(s)

SLSL

CK

n BASCULES

Opcode Opérandes

n BASCULES

Opcode Opérandes

Fanions

RAMRAM

Contrôle

SLCSLC

Opérandes

Instruction

Adresse

Format des instructions - SimplificationsDeuxième simplification: par défaut, on peut définir la prochaine instruction comme étant l’instruction suivante en mémoire.

0:+1|0 4:+11:+1 5:+12:+1 6:+1|43:+1 7:0

0:data inport1:ocount 02:mask 13:while data ≠ 04:tempdata AND mask5:ocountocount+temp6:data data >> 1 end while7:outport ocount

Séquenceur

Séquenceur

CK

n BASCULES

Opcode Opérandes

n BASCULES

Opcode Opérandes

Fanions

RAMRAM

Contrôle

SLCSLC

Opérande

s

Instruction

AdresseCK

Séquenceur

CK

Opérande

SLCOpcode

ConditionFanions

+1

Adresse

PC

Format des instructions - Simplifications

Transferts de données: 46 bits (un opérande peut être une adresse)

Opérations arithmétiques et logiques: 26 bits (que des registres)

Opérations d’entrée/sortie: 46 bits (un opérande peut être une adresse)

Instructions de contrôle: 44 bits

Toujours trop grandes! Il faut trouver d’autres simplifications.

OpcodeOpcode Opérandes (2)Opérandes (2)

OpcodeOpcode Opérandes (3)Opérandes (3)

OpcodeOpcode Opérandes (2)Opérandes (2)

OpcodeOpcode ConditionCondition Prochaine instructionProchaine instruction

Les opérations arithmétiques et logiques peuvent, en théorie, être effectuées directement sur des données en mémoire (CISC):

add adr1,adr2,adr3 (8+32x3=104 bits!)

En pratique, pour simplifier le contrôle du processeur, ce type d’opérations est toujours fait avec des données préalablement placées dans les registres du processeur (RISC):

add rx,ry,rz (8+6x3=26 bits)

Grâce à cette approche, 32 bits sont normalement suffisants pour stocker une instruction complète. Pour des processeurs plus petits (16 bits), on peut toujours réduire le nombre d’opérandes à deux:

move rx,rzadd ry,rz

Opérations arithmétiques et logiques

Transferts de données et I/OPour les transferts de données et pour le traitement des entrées/sorties, on ne peut pas se passer de références à la mémoire principale.L’instruction doit coder soit les données elles-mêmes, soit des indications sur comment l’unité de traitement peux les retrouver.Encore une fois, les transferts de données peuvent, en théorie, être effectués directement sur des adresses mémoire:

move adr1,adr2 (8+32x2=72 bits)

En pratique, pour simplifier le contrôle du processeur, un des opérandes (la source ou la destination, indifféremment) dans ce type d’opérations est toujours un des registres du processeur:

move adr,rx (8+ 32+6=46 bits)

Cette approche réduit le nombre de bits nécessaires pour codes ces instructions, mais pas suffisamment. Le problème est résolu (plus ou moins) par l’utilisations de modes d’adressage.

Modes d'adressagePour les transferts de données et pour le traitement des entrées/sorties, on suppose donc que l’un des opérandes est un registre. L’autre opérande doit coder soit les données elles-mêmes, soit leur emplacement dans la mémoire principale (adresse).

Petit exemple: MAX = 100;CNTR = MAX/2;ARR = MALLOC(MAX*sizeof(INT));START_VAL = *(ARR);END_VAL = *(ARR + 100);CNTR_VAL = *(ARR + CNTR);START = ARR;END = ARR + MAX;FOR (I=0; I<CNTR; I++) {

BOTTOM_HALF += *(START); START += sizeof(INT);TOP_HALF += *(END-sizeof(INT)); }

...

Adressage immédiatSi les données sont stockées directement dans l'instruction elle-même, on parle d’adressage immédiat ou littéral:

move data,rx

Il faut remarquer que les données de ce type d’instruction ont forcément une taille limitée par largeur de l’instruction (dans notre exemple, 32 - 8 - 6 = 18 bits).

Dans notre exemple:MAX = 100;

OpcodeOpcode DataData Destination (Rx)Destination (Rx)

Adressage par registreLes données peuvent être préalablement stockées dans un des registres du processeur. On parle dans ce cas d’adressage par registre:

move ry,rx

Les données dans ce type d’instructions ont une taille égale à la largeur des registres.

Dans notre exemple:CNTR = MAX/2;

OpcodeOpcode Source (Ry)Source (Ry)

Banc desregistres

Banc desregistres

Opérande

Destination (Rx)Destination (Rx)

Adressage directSi le deuxième opérande doit indiquer l’emplacement des données en mémoire principale, on peut coder directement l’adresse dans l’instruction. On parle dans ce cas d’adressage direct ou absolu:

move adr,rx

La taille des adresses est ici limitée par la largeur de l’instruction. Les bits restants sont implicites (ajoutés par la MMU).

Ce mode d'adressage est très rarement utilisé dans les programmes écrits par l'utilisateur. Par contre, il est très commun dans les OS:

ARR = MALLOC(MAX*sizeof(INT));

OpcodeOpcode Source (adresse)Source (adresse)

MMUMMU

MémoireMémoire

Opérande

Destination (Rx)Destination (Rx)

Adressage indirect par registreL’emplacement (adresse) des données en mémoire principale peut aussi être préalablement stocké dans un des registres du processeur.On parle dans ce cas d’adressage indirect par registre:

move (ry),rx

Les adresses dans ce type d’instructions ont une taille égale à la largeur des registres.

Dans notre exemple:START_VAL = *(ARR);

OpcodeOpcode Source (Ry)Source (Ry)

Banc desregistres

Banc desregistres

Adresse

MémoireMémoire

Opérande

Destination (Rx)Destination (Rx)

Adressage indirect via mémoireL’emplacement (adresse) des données en mémoire principale peut être lui-même stocké en mémoire principale. On parle dans ce cas d’adressage indirect via mémoire:

move (adr),rx

OpcodeOpcode Source (adresse)Source (adresse)

MémoireMémoire

Adresse

Opérande

MMUMMU

Destination (Rx)Destination (Rx)

La taille des adresses est ici limitée par la largeur de l’instruction. Les bits restants sont implicites (ajoutés par la MMU).

Comme l'adressage direct, ce mode d'adressage est très rarement utilisé dans les programmes écrits par l'utilisateur mais il est très commun dans les OS.

Adressage avec déplacementL’emplacement (adresse) des données en mémoire principale peut être défini comme un déplacement (offset) par rapport à une adresse de base stockée dans un des registres. Si le déplacement est stocké dans l'instruction, on parle d’adressage avec déplacement ou basé:

move dpl(ry),rx

OpcodeOpcode

Banc desregistres

Banc desregistres

Adresse

MémoireMémoire

Opérande

OffsetOffset

++

Base (Ry)Base (Ry) Destination (Rx)Destination (Rx)

La taille des adresses est égale à la largeur des registres. Par contre, la taille du déplacement est limitée par la taille de l'instruction.

Dans notre exemple:END_VAL = *(ARR + 100);

Adressage indexéL’emplacement (adresse) des données en mémoire principale peut être défini par la somme d’une adresse de base stockée dans un registre et d’un déplacement (index) stocké dans un autre registre. On parle dans ce cas d’adressage indexé:

move (ry+rz),rx

OpcodeOpcode

Banc desregistres

Banc desregistres

Adresse

MémoireMémoire

Opérande

Base (Ry)Base (Ry)

++Offset

Index (Rz)Index (Rz) Destination (Rx)Destination (Rx)

Les adresses et le déplacements dans ce type d’instructions ont une taille égale à la largeur des registres.Dans notre exemple:

CNTR_VAL = *(ARR + CNTR);

Adressage auto-incrémentéPour parcourir une série de positions mémoire successives (p.ex. lors de l’accès à une table), il est utile d’incrémenter une adresse avant ou après chaque accès. Il s'agit de l’adressage auto-incrémenté.

Post-incrément: move (ry)+,rx

OpcodeOpcode Source (Ry)Source (Ry)

Banc desregistres

Banc desregistres

Adresse

MémoireMémoire

Opérande

++Taille de la donnée

Destination (Rx)Destination (Rx)

Les adresses dans ce type d’instructions ont une taille égale à la largeur des registres.

Dans notre exemple:BOTTOM_HALF += *(START); START += sizeof(INT);

Adressage auto-décrémentéPour parcourir une série de positions mémoire successives à partir de la fin, il est utile de décrémenter une adresse avant ou après chaque accès. On parle dans ce cas d’adressage auto-décrémenté.

Pre-décrément: move -(ry),rx

OpcodeOpcode Source (Ry)Source (Ry)

Banc desregistres

Banc desregistres

Adresse

MémoireMémoire

Opérande

Taille de la donnée

--

Destination (Rx)Destination (Rx)

Les adresses dans ce type d’instructions ont une taille égale à la largeur des registres.

Dans notre exemple:TOP_HALF += *(END-sizeof(INT));

Petit exemple bien compliquéprogram toto;var

A, B, C : array [1...1000] of integer;i : integer

beginfor i:=1 to 1000 do

C[i] := A[i] + B[i];end

...MOVE.L #2001,A0 Charger l’adresse 2001 dans le registre A0

(pointeur sur le vecteur A)MOVE.L #3001,A1 Charger l’adresse 2001 dans le registre A1

(pointeur sur le vecteur B)MOVE.L #4001,A2 Charger l’adresse 2001 dans le registre A2

(pointeur sur le vecteur C)START: ABCD -(A0),-(A1) Décrémenter le contenu de A0 et A1 (adresses),

puis additionner les données (1 byte BCD)MOVE.B (A1),-(A2) Décrémenter A2 et stocker le résultat (1 octet)

dans le vecteur C TEST: CMPA #1001, A0 Comparer le contenu de A0 (adresse) avec 1001;

Z=1 si les deux valeurs sont égales, Z=0 sinon BNE START Sauter à START si Z n’est pas égal à 1 ...

Les instructions de contrôle (essentiellement des branchements) doivent nécessairement indiquer une adresse (la cible du branchement):

if (cond) then [continue] else [branche]

En théorie, cette cible pourrait être n’importe quelle position mémoire. En pratique, dans la grande majorité des cas, il s’agit d’un saut à une instruction dont la position mémoire est relativement proche de l’instruction qui est en train de s’exécuter.Par conséquent, le mode d’adressage couramment utilisé pour les instructions de contrôle est l’adressage par déplacement, où la base est définie implicitement comme étant le PC.

Instructions de contrôle

OpcodeOpcode ConditionCondition Adresse cibleAdresse cible

OpcodeOpcode ConditionCondition OffsetOffset

Séquenceur

Séquenceur

CK

n BASCULES

Opcode Opérandes

n BASCULES

Opcode Opérandes

Fanions

RAMRAM

Contrôle

SLCSLC

Opérande

s

Instruction

AdresseCK

Branchement par déplacement

0:+1|+0 4:+11:+1 5:+12:+1 6:+1|-23:+1 7:-70:data inport

1:ocount 02:mask 13:while data ≠ 04:tempdata AND mask5:ocountocount+temp6:data data >> 1 end while7:outport ocount

Séquenceur

Séquenceur

CK

n BASCULES

Opcode Opérandes

n BASCULES

Opcode Opérandes

Fanions

RAMRAM

Contrôle

SLCSLC

Opérande

s

Instruction

AdresseCK

Séquenceur

CK

Offset

SLCOpcode

ConditionFanions

+1

Adresse

+

PC

![Unité 1 unité 2 révisions 1 unité 3 unité 4 révisions 2[2] · 2017. 7. 14. · CORRIGÉ des exercices unité par unité Unité 1 p. 28 Ex 3 1. shù 2. táng 3. hē 4. mà 5.](https://static.fdocuments.fr/doc/165x107/5fecefa4b60207651f7e6888/unit-1-unit-2-rvisions-1-unit-3-unit-4-rvisions-22-2017-7-14.jpg)