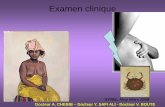

Examen de synthèse

Transcript of Examen de synthèse

INF3500 – examen final – automne 2014

Polytechnique Montréal page 1/13 Département de génie informatique et génie logiciel

INF3500 : Conception et réalisation de systèmes numériques

Examen final

Automne 2014

Durée: 2h30

Pondération: 50%

Documentation: Une feuille recto verso 8.5”×11” ou A4 permise.

Calculatrice: Programmable permise.

Directives particulières:

Ordinateurs, tablettes, téléphones, caméras et autres appareils mobiles interdits.

Répondre à toutes les questions, la valeur de chaque question est indiquée.

Répondre sur le questionnaire et le remettre.

Ne posez pas de questions. En cas de doute sur le sens d’une question, énoncez clairement toute

supposition que vous faites.

INF3500 – examen final – automne 2014

Polytechnique Montréal page 2/13 Département de génie informatique et génie logiciel

Question 1. (6 points)

L’unité de contrôle d’une version simplifiée du processeur PolyRISC comporte une unité de branchement.

Elle contribue à réaliser les instructions du type suivant : si (RA condition RB) goto (CP + valeur).

Elle a trois entrées et une sortie. Sa sortie doit être vraie quand il faut effectuer un branchement.

L’unité arithmétique et logique du processeur calcule la différence RA – RB et fournit les signaux Z et N à

l’unité de branchement. L’entrée Z indique si la différence est 0 et l’entrée N indique si la différence est

négative. L’entrée condition, exprimée avec 3 bits (un entier de 0 à 7) spécifie quand il faut brancher :

0: si RA = RB, 1: si RA != RB, 2: si RA < RB, 3: si RA > RB, 4: si RA <= RB, 5: si RA >= RB

6: brancher, indépendamment de Z et N, 7: ne pas brancher, indépendamment de Z et N

Donnez une architecture, en VHDL synthétisable, d’un module combinatoire qui correspond à ces spéci-

fications et à la définition d’entité suivante.

library ieee; use ieee.std_logic_1164.all;

entity uniteBranchement is

port(

Z, N : in std_logic;

condition: in integer range 0 to 7;

brancher: out std_logic

);

end uniteBranchement;

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

brancher

condition

Z

N

/

3

INF3500 – examen final – automne 2014

Polytechnique Montréal page 3/13 Département de génie informatique et génie logiciel

Question 2. (6 points)

Considérez le code VHDL et le modèle de FPGA suivants. Montrez, sur le modèle du FPGA, un résultat

possible de la synthèse et de l’implémentation de ce code. Indiquez directement sur le dessin où chaque

signal et port de sortie se situe ainsi que les interconnexions entre les blocs. Les interconnexions peuvent

contourner les blocs. Indiquez aussi la fonction logique réalisée par chaque LUT que vous utilisez. Res-

pectez l’assignation donnée pour les ports d’entrée.

library ieee;

use ieee.std_logic_1164.all;

entity module10 is

port (

clk, A, B, C, D, E: in std_logic;

X, Y, Z: out std_logic

);

end module10;

architecture arch of module10 is

signal F, G, H : std_logic;

begin

X <= not(A and B and E);

Y <= G xor H;

process(clk) is

begin

if rising_edge(CLK) then

F <= A and B and C and D;

G <= F xor E;

H <= B or C or D;

end if;

end process;

process(A, B, C)

begin

if A = '1' then

Z <= B or C;

else

Z <= B and C;

end if;

end process;

end arch;

Table de

conversion

(LUT)

D

CLK

QBloc entrée/

sortie

(IOB)

D

CLK

Q

Table de

conversion

(LUT)

D

CLK

Q

Table de

conversion

(LUT)

D

CLK

Q

Table de

conversion

(LUT)

D

CLK

Q

Table de

conversion

(LUT)

D

CLK

Q

Table de

conversion

(LUT)

D

CLK

Q

Table de

conversion

(LUT)

D

CLK

Q

Table de

conversion

(LUT)

D

CLK

Q

Table de

conversion

(LUT)

D

CLK

Q

Table de

conversion

(LUT)

D

CLK

Q

A

Bloc entrée/

sortie

(IOB)

D

CLK

Q

B

Bloc entrée/

sortie

(IOB)

D

CLK

Q

C

Bloc entrée/

sortie

(IOB)

D

CLK

Q

D

Bloc entrée/

sortie

(IOB)

D

CLK

Q

E

Bloc entrée/

sortie

(IOB)

D

CLK

Q

Bloc entrée/

sortie

(IOB)

D

CLK

Q

Bloc entrée/

sortie

(IOB)

D

CLK

Q

Bloc entrée/

sortie

(IOB)

D

CLK

Q

Bloc entrée/

sortie

(IOB)

D

CLK

Q

INF3500 – examen final – automne 2014

Polytechnique Montréal page 4/13 Département de génie informatique et génie logiciel

Question 3. (8 points)

Aidez le père Noël à calculer la valeur de Q = N / D, où N est le nombre de cadeaux fabriqués et D est le

nombre d’enfants sages, par la méthode de la division par la réciproque. On peut calculer la réciproque de

D au besoin puis effectuer le calcul Q = N × (1 / D).

La méthode de Newton-Raphson permet de calculer la réciproque d’un nombre D par un processus itéra-

tif. À chaque itération, on calcule Xk+1 = Xk + Xk × (1 – D × Xk). Si D est dans l’intervalle [0.5, 1] (suite à

une normalisation préalable) et avec X0 = 1, la valeur de Xk converge vers D-1 avec une précision accep-

table en 4 itérations. On peut décrire l’algorithme avec les micro-opérations suivantes où Din, N et init

sont des ports d’entrée du circuit, et que fini et Qout sont des ports de sortie du circuit. On suppose que

la valeur Din est dans l’intervalle [0.5, 1]. Quand fini prend la valeur 1, la sortie Qout indique le nombre

de cadeaux par enfant sage. (On suppose qu’on peut avoir des fractions de cadeaux par enfant.)

init : k ← 0; init’ ET k != 4: k ← k + 1;

init : X ← 1; init’ ET k != 4: X ← X + X * (1 – D * X);

init : fini ← 0; init’ ET k = 4 : fini ← 1

init : D ← Din;

Qout ← N * X

Donnez le diagramme d’un chemin des données correspondant à ces micro-opérations.

INF3500 – examen final – automne 2014

Polytechnique Montréal page 5/13 Département de génie informatique et génie logiciel

Question 4. (7 points)

Considérez le code VHDL suivant pour un arbitre de bus. L’arbitre permet à trois processeurs de partager

un bus unique. Quand un processeur veut avoir accès au bus, il active un des trois signaux de contrôle r

(pour « requête »). Pour informer un des processeurs qu’il peut se servir du bus, l’arbitre utilise l’un des

trois signaux de contrôle g (pour « go »). Quand le processeur correspondant a terminé du bus, il en in-

forme l’arbitre de bus en désactivant son signal de requête r.

-- tiré de S. Brown & Z. Vranesic,

-- Fund. of Digital Logic, McGraw-Hill, 2005.

LIBRARY ieee;

USE ieee.std_logic_1164.all;

ENTITY arbiter IS

PORT (

Clock, Resetn : IN STD_LOGIC ;

r : IN STD_LOGIC_VECTOR(1 TO 3);

g : OUT STD_LOGIC_VECTOR(1 TO 3)

) ;

END arbiter ;

ARCHITECTURE Behavior OF arbiter IS

TYPE State_type IS (Idle, gnt1, gnt2, gnt3);

SIGNAL y : State_type ;

BEGIN

g(1) <= '1' WHEN y = gnt1 ELSE '0';

g(2) <= '1' WHEN y = gnt2 ELSE '0';

g(3) <= '1' WHEN y = gnt3 ELSE '0';

PROCESS ( Resetn, Clock )

BEGIN

IF Resetn = '0' THEN y <= Idle;

ELSIF (Clock'EVENT AND Clock = '1') THEN

CASE y IS

WHEN Idle =>

IF r(1) = '1' THEN y <= gnt1;

ELSIF r(2) = '1' THEN y <= gnt2;

ELSIF r(3) = '1' THEN y <= gnt3;

ELSE y <= Idle ;

END IF ;

WHEN gnt1 =>

IF r(1) = '1' THEN y <= gnt1;

ELSE y <= Idle ;

END IF ;

WHEN gnt2 =>

IF r(2) = '1' THEN y <= gnt2;

ELSE y <= Idle ;

END IF ;

WHEN gnt3 =>

IF r(3) = '1' THEN y <= gnt3;

ELSE y <= Idle ;

END IF ;

END CASE ;

END IF ;

END PROCESS ;

END Behavior ;

a. (5 points) Donnez un diagramme d’états illustrant le fonctionnement de ce module. Identifiez claire-

ment chaque état, les transitions entre les états, et les conditions de transition entre les états.

b. (2 points) Combien de vecteurs de test seraient nécessaires pour effectuer un test exhaustif ? Justifiez

complètement votre réponse et montrez tous vos calculs.

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

INF3500 – examen final – automne 2014

Polytechnique Montréal page 6/13 Département de génie informatique et génie logiciel

Question 5. (8 points)

Considérez le code VHDL suivant pour un module combinatoire et son banc de test associé.

library IEEE;

use IEEE.std_logic_1164.all;

entity module3 is

port (

A, B, C : in std_logic;

F, G : out std_logic

);

end module3;

architecture arch2 of module3 is

signal S1, S2, S3 : std_logic := '0';

begin

S3 <= S1 or B;

G <= S3 or not(A);

process (A, B, C)

variable V : std_logic := '0';

begin

S1 <= A and C;

V := (not A) and (not B);

S2 <= V or C;

F <= B or C;

end process;

end arch2;

library ieee;

use ieee.std_logic_1164.all;

entity module3_TB is

end module3_TB;

architecture arch of module3_TB is

signal A, B, C, F, G : std_logic;

begin

UUT : entity module3(arch2)

port map (A, B, C, F, G);

A <= '1' after 0 ns;

B <= '0' after 0 ns;

C <= '0' after 0 ns, '1' after 10 ns;

end arch;

Donnez la valeur de tous les ports et signaux internes du module combinatoire en fonction du temps, en

tenant compte des délais deltas.

temps delta A B C S1 S2 S3 F G

0 ns 0

0 ns

0 ns

0 ns

0 ns

0 ns

0 ns

10 ns 0

10 ns

10 ns

10 ns

10 ns

10 ns

10 ns

INF3500 – examen final – automne 2014

Polytechnique Montréal page 7/13 Département de génie informatique et génie logiciel

Question 6. (7 points)

Considérez le chemin des données suivant du processeur PolyRISC.

UAL

B

A

F

Z

N

op_UAL

B

ch

oix

Ch

arg

e

Bloc des registres

ch

arg

eB

R

ch

oix

B

ch

oix

A

AdonnéeBR

Mémoire des données

donnee_MD

adresse

charge_MD

M[adresse]

ch

oix

B_

UA

L

ch

oix

Do

nn

ee

_B

R

`

va

leu

r

Op_UAL:

0: F <= A

1: F <= B

2: F <= A + B

3: F <= A – B

4: F <= A ET B

5: F <= A OU B

6: F <= NON A

7: F <= A OUX B

Sélection des muxes:

0: signal du haut

1: signal du bas

a. Indiquez si chaque opération ou groupe d’opérations simultanées suivants est possible. Si oui, donnez

la valeur des signaux de contrôle correspondants.

Opération ou groupe d’opérations simultanées

Po

ssib

le ?

ch

arg

eB

R

ch

oix

Ch

arg

e

ch

oix

A

ch

oix

B

vale

ur

Ch

oix

B_U

AL

Op

_U

AL

Ch

arg

e_

MD

ch

oix

Do

n-

nee_B

R

R4 := M[R0 + R2] ;

R7 := R1 + R2 ;

M[R1 + R2] := R1;

R0 := 534 ;

R4 := M[R0 + 534];

R3 := R4 + R5;

R4 := M[R4 + R5] ;

R2 := R1 ET 85;

M[R1 + 85] := R3;

b. Si des opérations ou groupes d’opérations sont impossibles, indiquez pourquoi dans chaque cas et pro-

posez une modification au chemin des données pour la/les rendre possible(s).

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

INF3500 – examen final – automne 2014

Polytechnique Montréal page 8/13 Département de génie informatique et génie logiciel

Question 7. (8 points)

Le diagramme de la page suivante montre un circuit implémenté sur un FPGA simplifié. Les entrées du

circuit sont C, D, E et F et les sorties sont Q, R et S. Le FPGA est composé de tranches ayant chacune une

table de conversion (LUT) et une bascule pouvant être utilisée ou non, et de blocs d’entrée/sortie (IOB)

dans lesquels les bascules sont toujours utilisées. Les LUTs ont un délai de 2.25 ns. Les bascules ont un

délai de 0.75 ns, un temps de préparation tsu de 0.25 ns, et un temps de maintien th de 0.1 ns. Les intercon-

nexions ajoutent un délai de 0.2 ns pour chaque rangée et chaque colonne de distance. Par exemple, le

signal qui part de la tranche C0R4 (colonne 0, rangée 4) pour aller à la LUT de la tranche C2R3 a un délai

de (2 (colonnes) + 1 (rangée)) × 0.2 ns = 0.6 ns.

a. (3 points) Identifiez le chemin critique du circuit sur le diagramme et donnez la fréquence maximale

d’horloge, en supposant aucun déphasage d’horloge.

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

b. (2 points) Le FPGA souffre d’un sérieux problème de conception pour la distribution du signal

d’horloge. Les bascules de chaque colonne reçoivent un signal d’horloge qui est en avance de 0.2 ns par

rapport aux bascules de la colonne précédente. Par exemple, les bascules de la colonne 0 reçoivent des

fronts d’horloge qui sont en retard de 0.4 ns par rapport à ceux reçus par les bascules de la colonne 2.

Dans ces conditions, quelle est la fréquence maximale d’horloge du circuit implémenté?

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

c. (3 points) Une nouvelle version du FPGA a été produite sans problème de déphasage d’horloge. Le

circuit est à nouveau implémenté. On veut le pipeliner pour atteindre un débit de 250 × 106 résultats par

seconde, où un résultat est un triplet Q/R/S. Indiquez clairement sur le dessin où et comment ajouter des

registres de pipeline. Identifiez le nouveau chemin critique et donnez la fréquence maximale d’horloge.

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

_____________________________________________________________________________________

INF3500 – examen final – automne 2014

Polytechnique Montréal page 9/13 Département de génie informatique et génie logiciel

a. Annotez le circuit pour indiquer le chemin critique.

c. Annotez le circuit pour montrer comment le pipeliner.

Bloc entrée/

sortie

(IOB)

D

CLK

Q

Bloc entrée/

sortie

(IOB)

D

CLK

Q

Bloc entrée/

sortie

(IOB)

D

CLK

Q

Bloc entrée/

sortie

(IOB)

D

CLK

Q

Bloc entrée/

sortie

(IOB)

D

CLK

Q

Table de

conversion

(LUT)

D

CLK

Q

Table de

conversion

(LUT)

D

CLK

Q

Table de

conversion

(LUT)

D

CLK

Q

Table de

conversion

(LUT)

D

CLK

Q

Table de

conversion

(LUT)

D

CLK

Q

Table de

conversion

(LUT)

D

CLK

Q

Table de

conversion

(LUT)

D

CLK

Q

Table de

conversion

(LUT)

D

CLK

Q

Table de

conversion

(LUT)

D

CLK

Q

Table de

conversion

(LUT)

D

CLK

Q

Table de

conversion

(LUT)

D

CLK

Q

Table de

conversion

(LUT)

D

CLK

Q

Table de

conversion

(LUT)

D

CLK

Q

Table de

conversion

(LUT)

D

CLK

Q

Table de

conversion

(LUT)

D

CLK

Q

Bloc entrée/

sortie

(IOB)

D

CLK

Q

Bloc entrée/

sortie

(IOB)

D

CLK

Q

Bloc entrée/

sortie

(IOB)

D

CLK

Q

Bloc entrée/

sortie

(IOB)

D

CLK

Q

Bloc entrée/

sortie

(IOB)

D

CLK

Q

D

C

E

F

Q

Colonne 1 Colonne 2Colonne 0

R

Rangée 0

Rangée 1

Rangée 2

Rangée 3

Rangée 4

S

Bloc entrée/

sortie

(IOB)

D

CLK

Q

Bloc entrée/

sortie

(IOB)

D

CLK

Q

Bloc entrée/

sortie

(IOB)

D

CLK

Q

Bloc entrée/

sortie

(IOB)

D

CLK

Q

Bloc entrée/

sortie

(IOB)

D

CLK

Q

Table de

conversion

(LUT)

D

CLK

Q

Table de

conversion

(LUT)

D

CLK

Q

Table de

conversion

(LUT)

D

CLK

Q

Table de

conversion

(LUT)

D

CLK

Q

Table de

conversion

(LUT)

D

CLK

Q

Table de

conversion

(LUT)

D

CLK

Q

Table de

conversion

(LUT)

D

CLK

Q

Table de

conversion

(LUT)

D

CLK

Q

Table de

conversion

(LUT)

D

CLK

Q

Table de

conversion

(LUT)

D

CLK

Q

Table de

conversion

(LUT)

D

CLK

Q

Table de

conversion

(LUT)

D

CLK

Q

Table de

conversion

(LUT)

D

CLK

Q

Table de

conversion

(LUT)

D

CLK

Q

Table de

conversion

(LUT)

D

CLK

Q

Bloc entrée/

sortie

(IOB)

D

CLK

Q

Bloc entrée/

sortie

(IOB)

D

CLK

Q

Bloc entrée/

sortie

(IOB)

D

CLK

Q

Bloc entrée/

sortie

(IOB)

D

CLK

Q

Bloc entrée/

sortie

(IOB)

D

CLK

Q

D

C

E

F

Q

Colonne 1 Colonne 2Colonne 0

R

Rangée 0

Rangée 1

Rangée 2

Rangée 3

Rangée 4

S

INF3500 – examen final – automne 2014

Polytechnique Montréal page 10/13 Département de génie informatique et génie logiciel

Solutions

1. Réponse

architecture arch of uniteBranchement is

begin

-- unité de branchement

process(Z, N, condition)

begin

case condition is

when 0 => brancher <= Z; -- =

when 1 => brancher <= not(Z); -- !=

when 2 => brancher <= N; -- <

when 3 => brancher <= not(N) and not(Z); -- >

when 4 => brancher <= N or Z; -- <=

when 5 => brancher <= not(N) or Z; -- >=

when 6 => brancher <= '1'; -- toujours

when 7 => brancher <= '0'; -- jamais

end case;

end process;

end;

2. Réponse

INF3500 – examen final – automne 2014

Polytechnique Montréal page 11/13 Département de génie informatique et génie logiciel

3. Réponse

4. a. Solution :

sur les transitions, l’ordre

des signaux est r1r2r3, et

un ‘x’ indique un signal

sans importance

(figure tirée de S. Brown & Z. Vranesic, Funda-

mentals of Digital Logic, McGraw-Hill, 2005.)

b. 4 états, 3 entrées : un test exhaustif requiert au minimum 4 × 23 = 32 vecteurs de test

INF3500 – examen final – automne 2014

Polytechnique Montréal page 12/13 Département de génie informatique et génie logiciel

5. Réponse

6. Réponse

Opération ou groupe d’opérations simultanées

Po

ssib

le ?

ch

arg

eB

R

ch

oix

Ch

arg

e

ch

oix

A

ch

oix

B

vale

ur

Ch

oix

B_U

AL

Op

_U

AL

Ch

arg

e_

MD

ch

oix

Do

n-

nee_B

R

R4 := M[R0 + R2] ; oui 1 4 0 2 - 0 2 0 1

R7 := R1 + R2 ;

M[R1 + R2] := R1; oui 1 7 2 1 - 0 2 1 0

R0 := 534 ;

R4 := M[R0 + 534]; non L’architecture ne permet pas de charger deux registres simultanément.

R3 := R4 + R5;

R4 := M[R4 + R5] ; non L’architecture ne permet pas de charger deux registres simultanément.

R2 := R1 ET 85;

M[R1 + 85] := R3; non

L’UAL n’a qu’une sortie et ne peut donc pas faire l’addition et l’opération

logique ET en même temps.

Pour les opérations #3, il faudrait un bloc de registres à deux entrées, deux chemins de rétroaction vers

l’entrée du bloc de registres, et deux signaux distincts choixCharge1 et choixCharge2. Il faudrait de plus

pouvoir aiguiller la valeur provenant de l’unité de contrôle (ici 534) vers le bloc des registres.

Pour les opérations #4, il faudrait un bloc de registres à deux entrées, deux chemins de rétroaction vers

l’entrée du bloc de registres (un de la mémoire et un de la sortie de l’UAL), et deux signaux distincts

choixCharge1 et choixCharge2.

Pour les opérations #5, il faudrait avoir deux sorties à l’UAL, par exemple une pour les fonctions logiques

et une pour les fonctions arithmétiques. Les additions devraient pouvoir être envoyées à l’adresse de la

mémoire. Toutes les opérations devraient pouvoir être retournées vers le bloc des registres en rétroaction.

[En pratique, on utilise un 2e additionneur pour calculer les adresses de la mémoire.]

INF3500 – examen final – automne 2014

Polytechnique Montréal page 13/13 Département de génie informatique et génie logiciel

7. Réponse

a. Le chemin critique a un délai de 0.75 + 0.6 + 2.25 + 0.6 + 2.25 + 0.25 = 6.7 ns, pour une fréquence

maximale d’horloge de 149 MHz.

b. Sur le chemin critique, on doit ajouter 0.4 ns à la période minimale d’horloge, donc Tmin = 7.1 ns,

fmax = 141 MHz.

Sur les chemins courts, p.ex. de IOB C à C0R1, on a un délai de 0.75 + 0.2 + 2.25 + 0.25 = 3.2 ns > th ok.

Donc fmax = 141 MHz.

c. On insère des registres de pipeline dans la colonne 1. Attention, il faut utiliser une tranche supplémen-

taire pour le chemin de C0R4 à C2R3. Le chemin critique a maintenant un délai de 0.75 + 0.6 + 2.25 +

0.25 = 3.85 ns, donc fmax = 259 MHz ok pour 250 × 106 résultats par seconde.