Commande dactionneurs à laide dun microprocesseur 1 Prise en main du DSP Christian Koechli.

-

Upload

astrid-gubbins -

Category

Documents

-

view

224 -

download

7

Transcript of Commande dactionneurs à laide dun microprocesseur 1 Prise en main du DSP Christian Koechli.

Commande d’actionneurs à l’aide d’un microprocesseur

1 Prise en main du DSP

Christian Koechli

Composants de l’électronique de commande

CPU: DSP ou

contrôleur

Driver

Mesure Capteurs

Alim puissance

Signaux logiques

Signaux de commande

Signaux de mesure

Alim. de la « logique »

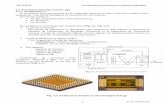

Texas Instruments TMS320F28069

• Processeur 32 bits• Architecture Harvard• F=90MHz (80 protos)• FPU / CLA• 256 kB flash• 100 kB RAM• 1 AD (16 canaux 12 bits 3MSps)• SPI/I2C/CAN/USB• 2 RS232• 54 GPIO• 3 CAPTURE +4 HRCap+ 2eQep• 8 ePWM

F28069Block Diagram

Memory Map

Gestion de la mémoire

Watchdog Timer

General Purpose IO

GPIOMultiplexing

Exemple de programmation

extern volatile struct GPIO_CTRL_REGS GpioCtrlRegs;extern volatile struct GPIO_DATA_REGS GpioDataRegs;struct GPIO_CTRL_REGS { union GPACTRL_REG GPACTRL; // GPIO A Control Register (GPIO0 to 31) union GPA1_REG GPAQSEL1; // GPIO A Qualifier Select 1 Register (GPIO0 to 15) union GPA2_REG GPAQSEL2; // GPIO A Qualifier Select 2 Register (GPIO16 to 31) union GPA1_REG GPAMUX1; // GPIO A Mux 1 Register (GPIO0 to 15) union GPA2_REG GPAMUX2; // GPIO A Mux 2 Register (GPIO16 to 31) union GPADAT_REG GPADIR; // GPIO A Direction Register (GPIO0 to 31) union GPADAT_REG GPAPUD; // GPIO A Pull Up Disable Register (GPIO0 to 31) Uint32 rsvd1; // reserved union GPBCTRL_REG GPBCTRL; // GPIO B Control Register (GPIO32 to 63) union GPB1_REG GPBQSEL1; // GPIO B Qualifier Select 1 Register (GPIO32 to 47) union GPB2_REG GPBQSEL2; // GPIO B Qualifier Select 2 Register (GPIO48 to 63) union GPB1_REG GPBMUX1; // GPIO B Mux 1 Register (GPIO32 to 47) union GPB2_REG GPBMUX2; // GPIO B Mux 2 Register (GPIO48 to 63) union GPBDAT_REG GPBDIR; // GPIO B Direction Register (GPIO32 to 63) union GPBPUD_REG GPBPUD; // GPIO B Pull Up Disable Register (GPIO32 to 63) Uint16 rsvd2[24];// reserved union AIO_REG AIOMUX1; // Analog IO Mux 1 Register (AIO0 to 15) Uint32 rsvd3; // reserved union AIODAT_REG AIODIR; // Analog IO Direction Register (AIO0 to 15) Uint16 rsvd4[5]; // reserved};

Exemple de programmationstruct GPIO_DATA_REGS { union GPADAT_REG GPADAT; // GPIO Data Register (GPIO0 to 31) union GPADAT_REG GPASET; // GPIO Data Set Register (GPIO0 to 31) union GPADAT_REG GPACLEAR; // GPIO Data Clear Register (GPIO0 to 31) union GPADAT_REG GPATOGGLE; // GPIO Data Toggle Register (GPIO0 to 31) union GPBPUD_REG GPBDAT; // GPIO Data Register (GPIO32 to 63) union GPBDAT_REG GPBSET; // GPIO Data Set Register (GPIO32 to 63) union GPBDAT_REG GPBCLEAR; // GPIO Data Clear Register (GPIO32 to 63) union GPBDAT_REG GPBTOGGLE; // GPIO Data Toggle Register (GPIO32to 63) Uint16 rsvd1[8]; // reserved union AIODAT_REG AIODAT; // Analog IO Data Register (AIO0-15) Uint16 rsvd2; union AIODAT_REG AIOSET; // Analog IO Data Set Register (AIO0-15) Uint16 rsvd3; union AIODAT_REG AIOCLEAR; // Analog IO Data Clear Register (AIO0-15) Uint16 rsvd4; union AIODAT_REG AIOTOGGLE; // Analog IO Data Toggle Register (AIO0-15) Uint16 rsvd5;};

Au reset toutes les pates sont configurées comme IO/input.Pour configurer la patte EPWM1A comme périphérique EPWM :EALLOW;GpioCtrlRegs.GPAMUX1.bit.GPIO0=1 ;EDIS;

Interrupts

A valid signal on a specific interrupt line causes the latch A valid signal on a specific interrupt line causes the latch to display a “1” in the appropriate bitto display a “1” in the appropriate bit

Maskable Interrupt Processing Conceptual Core Overview

11

00

11

((IFRIFR))““Latch”Latch”

INT1INT1

INT2INT2

INT14INT14

CoreCoreInterruptInterrupt

C28xC28xCoreCore

((INTMINTM))““Global Switch”Global Switch”

((IERIER))““Switch”Switch”

If the individual and global switches are turned “on” the If the individual and global switches are turned “on” the interrupt reaches the coreinterrupt reaches the core

Interrupt Flag Register (IFR)

RTOSINTRTOSINT DLOGINTDLOGINT INT14INT14 INT13INT13 INT12INT12 INT11INT11 INT10INT10 INT9INT9

8899101011111212131314141515

INT8INT8 INT7INT7 INT6INT6 INT5INT5 INT4INT4 INT3INT3 INT2INT2 INT1INT10011223344556677

Pending :Pending : IFR IFR BitBit = 1 = 1

Absent :Absent : IFRIFR Bit Bit = 0 = 0

Compiler generates atomic instructions (non-interruptible) for setting/clearing IFRCompiler generates atomic instructions (non-interruptible) for setting/clearing IFR If interrupt occurs when writing IFR, interrupt has priorityIf interrupt occurs when writing IFR, interrupt has priority IFR(bit) cleared when interrupt is acknowledged by CPUIFR(bit) cleared when interrupt is acknowledged by CPU Register cleared on reset Register cleared on reset

/*** Manual setting/clearing IFR ***//*** Manual setting/clearing IFR ***/

extern cregister volatile unsigned int IFR;extern cregister volatile unsigned int IFR;

IFR |= 0x0008;IFR |= 0x0008; //set INT4 in IFR//set INT4 in IFR

IFR &= 0xFFF7;IFR &= 0xFFF7; //clear INT4 in IFR//clear INT4 in IFR

Interrupt Enable Register (IER)

RTOSINTRTOSINT DLOGINTDLOGINT INT14INT14 INT13INT13 INT12INT12 INT11INT11 INT10INT10 INT9INT9

8899101011111212131314141515

INT8INT8 INT7INT7 INT6INT6 INT5INT5 INT4INT4 INT3INT3 INT2INT2 INT1INT10011223344556677

Enable: Set IER Enable: Set IER BitBit = 1 = 1

Disable: Clear IERDisable: Clear IER Bit Bit = 0 = 0

Compiler generates atomic instructions (non-interruptible) Compiler generates atomic instructions (non-interruptible) for setting/clearing IERfor setting/clearing IER

Register cleared on resetRegister cleared on reset

/*** Interrupt Enable Register ***//*** Interrupt Enable Register ***/

extern cregister volatile unsigned int IER;extern cregister volatile unsigned int IER;

IER |= 0x0008;IER |= 0x0008; //enable INT4 in IER//enable INT4 in IER

IER &= 0xFFF7;IER &= 0xFFF7; //disable INT4 in IER//disable INT4 in IER

Interrupt Global Mask Bit

• INTM used to globally enable/disable interrupts:– Enable: INTM = 0– Disable: INTM = 1 (reset value)

• INTM modified from assembly code only:

INTMINTMST1ST1 Bit 0Bit 0

/*** Global Interrupts ***//*** Global Interrupts ***/

asm(“ CLRC INTM”); //enable global interruptsasm(“ CLRC INTM”); //enable global interrupts

asm(“ SETC INTM”); //disable global interruptsasm(“ SETC INTM”); //disable global interrupts

F28069 PIE Interrupt Assignment Table

Déroulement d’un appel d’interruption