CIRCUITS Logiques programmables : PLD … · Entrées / sorties d’un P.A.L. combinatoire. ... Un...

Transcript of CIRCUITS Logiques programmables : PLD … · Entrées / sorties d’un P.A.L. combinatoire. ... Un...

Circuits logiques programmables

SILANUS & HORTOLLAND Circuits logiques programmables CPLD 2011-2012.DOC 1/8

Préambule :

Le document qui suit aborde dans une première partie le fonctionnement des circuits logiques

programmables simples, classés dans la catégorie SPLD (Simple PLD) dans certains catalogues. Puis des

circuits à plus haut niveau d’intégration que sont les CPLD.

Les autres circuits tels que les EPLD, FPGA, … ne sont pas abordés.

1. INTRODUCTION.

1.1. Concept.

Les PLD (composants logiques programmables) sont des circuits logiques constitués de matrices de

portes ET, OU, et NON

Les PLD se programment grâce à un équipement qui s'intègre dans un outil de développement

électronique.

1.2. Avantages.

Grâce aux PLD, un constructeur de circuits logiques peut implanter certaines fonctions logiques

complexes sur un seul circuit intégré. Cette façon de procéder rend plus efficace la conception, en

réduisant :

le nombre de circuits intégrés,

l’interconnexion entre les boîtiers,

la surface du circuit imprimé.

Le nombre réduit de circuits intégrés et d'interconnexions limite les risques de pannes, ce qui

entraîne une meilleure fiabilité.

Les circuits logiques programmables offrent une certaine confidentialité dans la mesure où il est

possible d’empêcher la lecture de leur programmation.

2. Après plusieurs année d’évolution et de concurrence entre

plusieurs fabricants, le terme PLD ne concerne quasiment plus

qu’une seule famille de composants les GAL (Generic Array

Logic) conçus par la société LATTICE. Ce sont des circuits

programmables et effaçables électriquement plusieurs fois.

3. Organisation élémentaire : PAL (Programmable Array Logic)

PLD GAL

PLD (Programmable Logic Devices) CPLD (Complex Programmable Logic Devices)

CIRCUITS Logiques programmables :

PLD et CPLD

Circuits logiques programmables

SILANUS & HORTOLLAND Circuits logiques programmables CPLD 2011-2012.DOC 2/8

Pour simplifier le schéma, on utilise une représentation unifilaire des entrées des fonctions ET.

Exemple : donner l’équation de S

3.1. Entrées / sorties d’un P.A.L. combinatoire.

Circuits logiques programmables

SILANUS & HORTOLLAND Circuits logiques programmables CPLD 2011-2012.DOC 3/8

3.2. Entrées / sorties d’un P.A.L. à registres.

3.3. Entrées / sorties d’un P.A.L. à OU-EXCLUSIF.

4. Exemple de décodage

des références.

Indiquer les caractéristiques du circuit : GAL16V8ZD-15QP

Un circuit disposant de bascules en sortie peut réaliser quel(s) composant(s) logique(s) classique(s) ?

Circuits logiques programmables

SILANUS & HORTOLLAND Circuits logiques programmables CPLD 2011-2012.DOC 4/8

5. La programmation de circuits logiques

Plusieurs solutions sont possibles pour programmer les PLD. Elles dépendent essentiellement de l’outil de

développement utilisé.

Logigramme (Schéma logique)

Langage ABEL.

Langage VHDL.

Langage Verilog.

La programmation des PLDs nécessite un logiciel adapté pour le développement du programme et un

programmateur permettant de « griller » le circuit. En outre il est conseillé de suivre la démarche décrite par

l’organigramme suivant :

Cahier des charges

Mise en « équation » du problème

Résolution du problème sous forme d’équations

logiques, de table de vérité, de logigramme ou

d’algorithme

Saisie des équations logiques, de la table de vérité,

du logigramme ou de l’algorithme avec le logiciel

Simplification logique

Génération d’un fichier au format JEDEC

Simulation

Programmation du PLD à l’aide du fichier JEDEC

et du programmateur

PLD programmé

Choix du PLD en fonction

du nombre d’entrées et de sorties

étapes logicielles

Analyse « papier »

Circuits logiques programmables

SILANUS & HORTOLLAND Circuits logiques programmables CPLD 2011-2012.DOC 5/8

5.1. Description du langage ABEL.

Ce langage permet de décrire le comportement d’un composant logique

programmable de différentes manières :

Description par les équations logiques. Description arithmétique.

Description par diagramme d’état. Description par une table de vérité.

On appelle le fichier écrit dans ce langage et destiné à la programmation d’un

composant programmable le fichier source. Il se compose de trois parties

principales.

Exemples de fichiers ABEL pour traiter un même problème de façons différentes :

5.2. Elaboration du fichier JEDEC.

C’est le format de fichier généralement utilisé par les programmateurs de circuits

logiques programmables. Il est constitué de la liste des interconnexions entre les

lignes et les colonnes de la matrice du composant à programmer.

Ce fichier est obtenu par compilation du fichier source écrit en langage ABEL.

MODULE dist_boi;

title 'Distributeur de boissons'

dist_boi Device 'p16v8';

Declarations

"Inputs

CN, CNS, CL, CLS pin 6, 7, 8, 9;

"Outputs

G,E,C,L,S pin 12, 13, 14, 15 istype 'com';

Equations

G = CN&CNS&(CL$CLS)#CL&CLS&(CN$CNS);

E = CN&CNS&(CL$CLS)#CL&CLS&(CN$CNS);

C = CN&CNS&(CL$CLS)#CL&CLS&(CN$CNS);

L = CN&CNS&(CL$CLS);

S = CN&CL&(CNS$CLS);

End dist_boi

MODULE dist_boi;

title 'Distributeur de boissons'

dist_boi Device 'p16v8';

Declarations

"Inputs

CN, CNS, CL, CLS pin 6, 7, 8, 9;

"Outputs

G,E,C,L,S pin 12, 13, 14, 15 istype 'com';

Equations

Truth_table ([CN, CNS, CL, CLS]->[G,E,C,L,S]);

[0, 0, 0, 0]->[0, 0, 0, 0, 0];

[0, 0, 0, 1]->[

[0, 0, 1, 0]->[

[0, 0, 1, 1]->[

[0, 1, 0, 0]->[

[0, 1, 0, 1]->[

[0, 1, 1, 0]->[

[0, 1, 1, 1]->[

[1, 0, 0, 0]->[

[1, 0, 0, 1]->[

[1, 0, 1, 0]->[

[1, 0, 1, 1]->[

[1, 1, 0, 0]->[

[1, 1, 0, 1]->[

[1, 1, 1, 0]->[

[1, 1, 1, 1]->[

end dist_boi;

Fichier ABEL utilisant les équations : Fichier ABEL utilisant la table de vérité :

! : inversion

& : ET

# : OU

$ : OU Exclusif

Compléter ci-contre la version utilisant une table de

vérité, sachant que les entrées sont actives à l’état

bas.

Circuits logiques programmables

SILANUS & HORTOLLAND Circuits logiques programmables CPLD 2011-2012.DOC 6/8

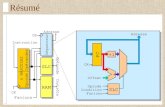

Les CPLD

(Complex Programmable Logic Devices)

Il existe 4 fabricants de CPLD : ALTERA, ATMEL, LATTICE et XILINX

La présentation qui suit n’aborde que les circuits de la famille ispMACH 4A de la société

Lattice

Description fonctionnelle :

L’architecture fonctionnelle des circuits ispMACH 4A est constituée de plusieurs blocs de

type PAL (PAL block) interconnectés entre eux par une matrice centrale de commutation

(central switch matrix)

Exemple de macrocellule

Circuits logiques programmables

SILANUS & HORTOLLAND Circuits logiques programmables CPLD 2011-2012.DOC 7/8