Chapitre iii processeur intel 80x86

-

Upload

sana-aroussi -

Category

Documents

-

view

1.217 -

download

88

Transcript of Chapitre iii processeur intel 80x86

CHAPITRE III

PROCESSEUR INTEL 80X86

Université Saad Dahleb de Blida

Faculté des Sciences

Département d’Informatique

Licence Génie des Systèmes Informatique (GSI)

Semestre 3 (2ème année)

AROUSSI

2013 - 2014

Disponible sur https://sites.google.com/a/esi.dz/s-aroussi/

2

Présenter le Processeur 8086 de Intel

Étudier son jeux d'instruction.

Apprendre à le programmer en assembleur pour

comprendre son fonctionnement.

Coder les instructions en langage machine (binaire).

OBJECTIFS DU CHAPITRE

PLAN DU CHAPITRE III

Introduction

Architecture Générale

Jeu d’instructions

Programmation en Assembleur

Code Machine des Instructions

3

4

INTRODUCTION ÉVOLUTION DES PROCESSEURS INTEL

1971

1972 – 1992

1993-2005

2006 jusqu’à aujourd’hui

Premier processeur

4004

Processeurs 80x : 8080,

8086, 8080, 80286, 80386,

80486, ......

Pentium: I, II, III,

IV, V, ...

Processeurs multi-cœurs:

Core 2, i5, i7, .....

La majorité des microprocesseurs

Intel sont compatibles avec le 8086

5

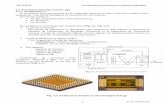

INTRODUCTION PROCESSEUR INTEL 8086

Disponible depuis 1978, le processeur 8086 fut le premier

processeur 16 bits fabriqué par Intel.

Il se présente sous forme d'un boîtier de 40 broches

alimenté par une alimentation unique de 5V.

PARTIE 1:

ARCHITECTURE GÉNÉRALE DU

PROCESSEUR 8086 6

7

Bus de données Interne 16 bits Bus de données Interne 16 bits

UAL

Codage

Contrôle

Séquencement File d’attente 6

octets de codes

instructions

AH AL

BH BL

CH CL

DH DL

BP

SP

SI

DI

AX

BX

CX

DX

CS

DS

SS

ES

Calcul

d’adresse

IP

RT RT

Flags

Interface

avec Bus

externes

Bus d’adresse Bus d’adresse

Bus de données Bus de données

Bus de contrôle

20 bits

16 bits

16 bits

Bus d’adresse Interne 20 bits

Architecture Générale du processeur 8086

8

ARCHITECTURE GÉNÉRALE DU PROCESSEUR 8086 SEGMENTATION DE LA MEMOIRE

La taille du bus d’adresse égale à 20 bits La mémoire totale

adressable égale 220 octets = 1 Mo

La taille des registres est 16 bits on peut adresser seulement 216

octets = 64 ko.

La mémoire est donc fractionnée en pages de 64 ko appelés

segments.

On utilise alors deux registres pour adresser une case mémoire

donnée:

Un registre pour adresser le segment, appelé registre segment:

CS, DS, SS, ES

Un registre pour adresser à l'intérieur du segment, appelé

registre offset: IP, SP, BP, SI, DI.

Une adresse se présente sous la forme segment:offset

9

ARCHITECTURE GÉNÉRALE DU PROCESSEUR 8086 REGISTRES

Tous les registres du 8086 sont structurés en 16 bits.

10

ARCHITECTURE GÉNÉRALE DU PROCESSEUR 8086 REGISTRES GÉNÉRAUX

Registres Usage

AX:

Accumulateur

Usage général,

Obligatoire pour la multiplication et la division,

Ne peut pas servir pour l'adressage

BX : Base Usage général,

Adressage

CX :

Comptage et

calcul

Usage général,

Compteur de répétition.

Ne peut pas servir pour l'adressage

DX : Data

Usage général,

Extension au registre AX pour contenir un nombre

32 bits Dans la multiplication et la division 16 bits

Ne peut pas servir pour l'adressage

11

ARCHITECTURE GÉNÉRALE DU PROCESSEUR 8086 REGISTRES GÉNÉRAUX

Registres Usage

SP : Pointeur

de Pile

Utilisé pour l'accès à la pile. Pointe sur la tête de

la pile

BP : Pointeur

de Base

Usage général

Adressage comme registre de base

SI : Registre

d'index (source)

Usage général

Adressage comme registre d’index de l'opérande

source.

DI : Registre

d'index

(destination)

Usage général

Adressage comme registre d’index de l'opérande

destination

12

ARCHITECTURE GÉNÉRALE DU PROCESSEUR 8086 REGISTRES DE SEGMENT

Ces registres sont combinés avec les registres offset (par exemple IP) pour

former les adresses. Une case mémoire est repérée par une adresse de la

forme [Rseg :Roff]

Le registre segment localise le début d’une zone mémoire de 64Ko

Le registre offset précise l’adresse relative par rapport au début de

segment.

13

ARCHITECTURE GÉNÉRALE DU PROCESSEUR 8086 REGISTRES DE SEGMENT

Registres Usage

CS : Code

Segment Définit le début de la mémoire programme dans laquelle sont

stockées les instructions du programme.

Les adresses des différentes instructions du programme sont

relatives à CS

DS : Data

Segment Définit le début de la mémoire de données dans laquelle sont

stockées toutes les données traitées par le programme.

SS : Stack

Segment Définit le début de la pile.

SP permet de gérer l’empilement et le dépilement.

ES : Extra

Segment Définit le début d'un segment auxiliaire pour données

14

ARCHITECTURE GÉNÉRALE DU PROCESSEUR 8086 COMPTEUR D’INSTRUCTION

Le compteur d’instruction (IP), appelé aussi Compteur

Ordinal (C.O.) permet de pointer TOUJOURS le premier

octet de l’instruction suivante.

15

ARCHITECTURE GÉNÉRALE DU PROCESSEUR 8086 REGISTRE D'ÉTAT (FLAGS)

C (Carry) : indique qu’il y a une retenue du résultat à

8 bits ou 16 bits.

P (Parité) : indique que le nombre de 1 est un nombre

pair.

Z (Zéro) : indique que le résultat est nul.

S (Signe) : indique le signe du résultat

O (Overflow): indique un dépassement de capacité

O D I T S Z A P C

0 15

16

ARCHITECTURE GÉNÉRALE DU PROCESSEUR 8086 FORMAT D’INSTRUCTION

La structure la plus générale d’une instruction est la suivante :

L’opération est réalisée entre les 2 opérandes et le résultat

est toujours récupéré dans l’opérande de gauche.

Il y a aussi des instructions qui agissent sur un seul opérande

INST Opérande

Les opérandes peuvent être des registres, des constantes ou le

contenu de cases mémoire.

17

ARCHITECTURE GÉNÉRALE DU PROCESSEUR 8086 MODE D’ADRESSAGE

1. Adressage registre

L'opération se fait sur un ou 2 registres

INST R , R

INST R

Exemples :

INC AX : incrémenter le registre AX (AX++)

MOV AX, BX : Copier le contenu de BX dans AX

(AXBX)

18

ARCHITECTURE GÉNÉRALE DU PROCESSEUR 8086 MODE D’ADRESSAGE

2. Adressage Immédiat

L’opérande est une constante (valeur) qui fait partie de

l’instruction :

INST R , IM

INST IM

Exemples :

MOV AX, 243 : charger le registre AX par le nombre

décimal 243 (AX243)

JMP 008 : saut à l’instruction du numéro 008

19

ARCHITECTURE GÉNÉRALE DU PROCESSEUR 8086 MODE D’ADRESSAGE

2. Adressage Immédiat

L’opérande est une constante (valeur) qui fait partie de

l’instruction : INST R , IM; INST IM

Exemples :

MOV AL, ‘A‘ : Charger le registre AL par le code ASCII du

caractère ‘A' (65)

MOV AX, ‘A‘ : Charger le registre AH par 00 et le registre

AL par le code ASCII du caractère ‘A'

MOV AX,‘AB' : Charger AH par le code ASCII du caractère

‘A' et AL par le code ASCII du caractère ‘B‘ (66)

20

ARCHITECTURE GÉNÉRALE DU PROCESSEUR 8086 MODE D’ADRESSAGE

3. Adressage direct

Un des deux opérandes se trouve en mémoire. L’adresse

de la case mémoire est précisé directement dans

l’instruction.

INST R , [adr]

INST [adr] , R

INST taille [adr] , im

L’adresse doit être placée entre [Rseg:Roff]. Si le segment

(Rseg) n’est pas précisé, DS est pris par défaut.

21

ARCHITECTURE GÉNÉRALE DU PROCESSEUR 8086 MODE D’ADRESSAGE

3. Adressage direct

INST R , [adr]

INST [adr] , R

INST taille [adr] , im

Exemples :

MOV AX,[243] : Copier le contenu de la mémoire d'adresse

DS:243 dans AX

MOV [123],AX : Copier le contenu de AX dans la mémoire

d'adresse DS:123

MOV AX, [SS:243] : Copier le contenu de la mémoire SS:243

dans AX

22

ARCHITECTURE GÉNÉRALE DU PROCESSEUR 8086 MODE D’ADRESSAGE

4. Adressage Indirect

Un des deux opérandes se trouve en mémoire. L’adresse se

trouve dans l’un de ces 4 registres BX, BP, SI ou DI.

INST R , [Rseg : Roff]

INST [Rseg : Roff] , R

INST taille [Rseg : Roff] , im

Si Rseg n'est pas spécifié, le segment par défaut sera

utilisé.

Registre BX BP SI DI

Segment par défaut DS SS DS DS

23

ARCHITECTURE GÉNÉRALE DU PROCESSEUR 8086 MODE D’ADRESSAGE

4. Adressage Indirect

Exemples :

MOV AX, [BX]; Charger AX par le contenu de la mémoire d'adresse

DS:BX

MOV AX, [BP]; Charger AX par le contenu de la mémoire d'adresse

SS:BP

MOV AX, [SI]; Charger AX par le contenu de la mémoire d'adresse

DS:SI

MOV AX, [DI] ; Charger AX par le contenu de la mémoire d'adresse

DS:DI

MOV AX, [ES:BP]; Charger AX par le contenu de la mémoire

d'adresse ES:BP

24

ARCHITECTURE GÉNÉRALE DU PROCESSEUR 8086 MODE D’ADRESSAGE

4. Adressage Indirect

L’adressage indirect est divisé en 3 catégories selon le

registre d’offset utilisé: l’adressage Basé, l’adressage

indexé et l’adressage basé indexé.

Mode Adressage Basé Indexé Basé Indexé

Registres utilisés BX

BP

DI

SI

BX, DI

BX, SI

BP, DI

BP, SI

25

ARCHITECTURE GÉNÉRALE DU PROCESSEUR 8086 MODE D’ADRESSAGE

4. Adressage Indirect

A. Adressage Basé

L’offset se trouve dans l’un des deux registres de base BX

ou BP. On peut préciser un déplacement qui sera ajouté

au contenu de Roff pour déterminer l’offset,

INST R , [Rseg : Rb+dep]

INST [Rseg : Rb+dep] , R

INST taille [Rseg : Rb+dep] , im

26

ARCHITECTURE GÉNÉRALE DU PROCESSEUR 8086 MODE D’ADRESSAGE

4. Adressage Indirect

A. Adressage Basé

Exemples :

MOV AX, [BX] : Charger AX par le contenu de la mémoire d'adresse

DS:BX

MOV AX, [BX+5] : Charger AX par le contenu de la mémoire d'adresse

DS:BX+5

MOV AX, [BP-200] : Charger AX par le contenu de la mémoire d'adresse

SS:BX-200

MOV AX, [ES:BP] : Charger AX par le contenu de la mémoire d'adresse

ES:BP

27

ARCHITECTURE GÉNÉRALE DU PROCESSEUR 8086 MODE D’ADRESSAGE

4. Adressage Indirect

B. Adressage Indexé

L’offset se trouve dans l’un des deux registres d’index SI

ou DI. On peut préciser un déplacement qui sera ajouté au

contenu de Ri pour déterminer l’offset.

INST R , [Rseg : Ri+dep]

INST [Rseg : Ri+dep] , R

INST taille [Rseg : Ri+dep] , im

28

ARCHITECTURE GÉNÉRALE DU PROCESSEUR 8086 MODE D’ADRESSAGE

4. Adressage Indirect

B. Adressage Indexé

Exemples :

MOV AX, [SI]; Charger AX par le contenu de la mémoire

d'adresse DS:SI

MOV AX, [SI+500]; Charger AX par la mémoire d'adresse

DS:SI+500

MOV AX, [DI-8]; Charger AX par la mémoire d'adresse DS:DI-8

MOV AX, [ES:SI+4]; Charger AX par la mémoire d'adresse

ES:SI+4

29

ARCHITECTURE GÉNÉRALE DU PROCESSEUR 8086 MODE D’ADRESSAGE

4. Adressage Indirect

C. Adressage Basé Indexé

L'offset de l’adresse de l'opérande est la somme d'un

registre de base, d'un registre d'index et d'un déplacement

optionnel. Si Rseg n'est pas spécifié, le segment par défaut

du registre de base est utilisé :

INST R , [Rseg : Rb+Ri+dep]

INST [Rseg : Rb+Ri+dep] , R

INST taille [Rseg : Rb+Ri+dep] , im

30

ARCHITECTURE GÉNÉRALE DU PROCESSEUR 8086 MODE D’ADRESSAGE

4. Adressage Indirect

C. Adressage Basé Indexé

Exemples :

MOV AX,[BX+SI]; AX est chargé par la mémoire d'adresse

DS:BX+SI

MOV AX,[BX+DI+5]; AX est chargé par la mémoire d'adresse

DS:BX+DI+5

MOV AX,[BP+SI-8]; AX est chargé par la mémoire d'adresse

SS:BP+SI-8

MOV AX,[BP+DI]; AX est chargé par la mémoire d'adresse

SS:BP+DI

31

ARCHITECTURE GÉNÉRALE DU PROCESSEUR 8086 TAILLE DES ECHANGES AVEC LA MEMOIRE

La mémoire est organisée en octets.

1. Quand on fait une instruction entre un registre et une

donnée qui se trouve en mémoire, c’est le registre qui

détermine la taille de l’opération:

Si le registre est un registre simple (8 bits), l’opération

se fera avec une seule case mémoire.

32

ARCHITECTURE GÉNÉRALE DU PROCESSEUR 8086 TAILLE DES ECHANGES AVEC LA MEMOIRE

1. Quand on fait une instruction entre un registre et une

donnée qui se trouve en mémoire, c’est le registre qui

détermine la taille de l’opération:

Si le registre est un registre double (2 octets),

l’opération se fera avec deux cases mémoires

MOV [adresse], AX donne

33

ARCHITECTURE GÉNÉRALE DU PROCESSEUR 8086 TAILLE DES ECHANGES AVEC LA MEMOIRE

2. Quand on fait une opération entre une constante et une

case mémoire, il faut utiliser les préfixes BYTE (1 octet) et

WORD (2 octets) pour préciser le nombre d’octets à écrire :

PARTIE 2:

JEUX D’INSTRUCTIONS

DU PROCESSEUR 8086 34

35

JEUX D’INSTRUCTIONS

Plusieurs types d’instructions, notamment:

Instructions de Transfert (MOV, XCHG, ....)

Instructions Arithmétiques (ADD, SUB, MUL, DIV, ...)

Instructions Logiques (NOT, AND, OR, XOR, ...)

Instructions de Décalage (SHR, SHL, ROL, ROR, ...)

Instruction de Branchement (JMP, Jxx, LOOP....)

......

36

INSTRUCTIONS DE TRANSFERT

MOV

MOV Od,Os: Copie l'opérande Source (Os) dans

l'opérande Destination (Od) [OdOS]

MOV R1 , R2 R1R2

MOV R , [adr] R[adr]

MOV [adr] , R [adr]R

MOV R , im Rim

MOV taille [adr] , im copier une constante dans une case mémoire

taille = BYTE ou WORD

MOV [adr], [adr]

MOV Rseg, Rseg

37

INSTRUCTIONS DE TRANSFERT

XCHG

XCHG Od,Os: Échange l'opérande Source (Os) avec

l'opérande Destination (Od) [OsOd].

XCHG R1 , R2 R1R2

XCHG [adr] , R

XCHG R , [adr]

[adr]R

XCHG [adr], [adr]

38

INSTRUCTIONS ARITHMÉTIQUES

Le 8086 permet d'effectuer les quatre opérations

arithmétiques de base: l'addition, la soustraction, la

multiplication et la division.

Les opérations peuvent s'effectuer sur des nombres de 8

bits ou de 16 bits signés ou non signés.

Les nombres signés sont représentés en complément à 2.

39

INSTRUCTIONS ARITHMÉTIQUES

ADDITION

ADD Od,Os: additionne l'opérande source et l'opérande

destination et met le résultat dans l'opérande destination

[OdOd+Os].

ADD R1 , R2 R1 R1 + R2

ADD R , [adr] R1 R + [adr]

ADD [adr] , R [adr] [adr] + R

ADD R , im R R + im

ADD taille [adr] , im [adr] [adr] + im

ADD [adr], [adr]

40

INSTRUCTIONS ARITHMÉTIQUES

ADDITION

INC Op: incrémente l'opérande Op [Op Op+1].

Exemple: En partant de la situation mémoire illustrée, quelle est

la situation mémoire après l’exécution séquentielle des instructions

suivantes

INC BYTE [400h]

INC WORD [400h]

INC R R R+1

INC taille [adr] Incrémenter le contenu d’une case mémoire

taille = BYTE ou WORD

FE

33

DS: 400

41

INSTRUCTIONS ARITHMÉTIQUES

ADDITION

Exemple:

FE

33

DS: 400

INC WORD [400h]

INC BYTE [400h]

FF

33

DS: 400

00

34

DS: 400 Bits de poids faible

Bits de poids fort

42

INSTRUCTIONS ARITHMÉTIQUES

SOUSTRACTION

SUB Od,Os: soustrait l'opérande source et l'opérande

destination et met le résultat dans l'opérande destination

[OdOd-Os].

SUB R1 , R2 R1 R1 - R2

SUB R , [adr] R1 R - [adr]

SUB [adr] , R [adr] [adr] – R

SUB R , im R R - im

SUB taille [adr] , im [adr] [adr] - im

SUB [adr], [adr]

43

INSTRUCTIONS ARITHMÉTIQUES

SOUSTRACTION

DEC Op: décrémente l'opérande Op [Op Op-1].

NEG Op: Remplace Op par son négatif

[Op0-Op = CA2 (Op)]

DEC R R R-1

DEC taille [adr] [adr] [adr] - 1

NEG R R CA2(R)

NEG taille [adr] [adr] CA2 ([adr])

44

INSTRUCTIONS ARITHMÉTIQUES

SOUSTRACTION

Exemple:

MOV AX, 26h

SUB CX 59h

MOV AX, 35

NEG AX

0 0 2 6 AX

F F C D CX

Z = 0 ; C = 1 ; S = 1

0 0 2 3 AX

F F D D AX

45

INSTRUCTIONS ARITHMÉTIQUES

SOUSTRACTION

CMP Od,Os: compare (soustrait) les opérandes Od et Os

et positionne les flags (registre d’état) en fonction du

résultat. L’opérande Od n’est pas modifié.

Opérandes non Signés Opérandes Signé

O S Z C O S Z C

Od > Os - 0 0 0 0/1 0 0 -

Od = Os - 0 1 0 0 0 1 -

Od < Os - 1 0 1 0/1 1 0 -

46

INSTRUCTIONS ARITHMÉTIQUES

SOUSTRACTION

Exemple:

MOV AL, 23

CMP AL, 34

? ? 1 7 AX

C = 1 ; Z = 0; S = 1

Opérandes non Signés Opérandes Signé

O S Z C O S Z C

Od > Os - 0 0 0 0/1 0 0 -

Od = Os - 0 1 0 0 0 1 -

Od < Os - 1 0 1 0/1 1 0 -

AL AH

47

INSTRUCTIONS ARITHMÉTIQUES

MULTIPLICATION

MUL Os: effectue une multiplication non signée entre

l'accumulateur (AL ou AX) et l'opérande Os. Le résultat

de taille double est stocké dans l'accumulateur et son

extension (AH ou DX).

IMUL Os : identique à MUL excepté qu'une

multiplication signée est effectuée.

48

INSTRUCTIONS ARITHMÉTIQUES

MULTIPLICATION

(I) MUL Reg8 AX AL * Reg8

(I) MUL BYTE [adr] AX AL * [adr]

(I) MUL Reg16 DX:AX AX * Reg16

(I) MUL WORD [adr] DX:AX AX * [adr]

(I) MUL im

49

INSTRUCTIONS ARITHMÉTIQUES

MULTIPLICATION

Exemple:

MOV AL, 4

MOV AH, 25

MUL AH

MOV BX, 435

MOV AX, 2372

MUL BX

? ? 0 4 AX

AL AH

0 0 6 4

1 9 0 4

0 1 B 3

0 0 0 F

0 9 4 4

B E 8 C

BX

AX

AX DX

50

INSTRUCTIONS ARITHMÉTIQUES

MULTIPLICATION

Exemple:

MOV BX, 435

MOV AX, 2372

MUL BX

MOV BX, -435

MOV AX, 2372

IMUL BX

F E 4 D

F F F 0

0 9 4 4

4 1 7 4

BX

AX

AX DX

0 1 B 3

0 0 0 F

0 9 4 4

B E 8 C

BX

AX

AX DX

51

INSTRUCTIONS ARITHMÉTIQUES

DIVISION

DIV Os: effectue une division non signée de

l'accumulateur (AL ou AX) par l'opérande Os. Le quotient

est récupéré dans le registre AL ou AX et le reste dans le

registre AH ou DX.

IDIV Os : identique à DIV excepté qu'une division signée

est effectuée.

52

INSTRUCTIONS ARITHMÉTIQUES

DIVISION

(I) DIV Reg8

(I) DIV BYTE [adr]

AL Quotient

AH Reste

(I) DIV Reg16

(I) DIV WORD [adr]

AX Quotient

DX Reste

(I) DIV im

53

INSTRUCTIONS ARITHMÉTIQUES

DIVISION

Exemple:

MOV BX, 435

MOV AX, 2372

DIV BX

MOV BX, -435

MOV AX, 2372

DIV BX

0 1 B 3

0 0 C 5

0 9 4 4

0 0 0 5

BX

AX

AX (Quotient) DX (Reste)

F E 4 D

0 0 C 5

0 9 4 4

F F F B

BX

AX

AX (Quotient) DX (Reste)

54

INSTRUCTIONS ARITHMÉTIQUES

DIVISION

CBW (Convert Byte to Word) effectue une extension de

AL dans AH en respectant le signe:

Si AL contient un nombre positif, on complète par des 0 pour

obtenir la représentation sur 16 bits.

Si AL contient un nombre négatif, on complète par des 1 pour

obtenir la représentation sur 16 bits.

Exemple:

MOV AL, 96

CBW

AX

AL AH

0 0 6 0

? ? 6 0

55

INSTRUCTIONS ARITHMÉTIQUES

DIVISION

CWD (Convert Word to Double Word) effectue une

extension de AX dans DX en respectant le signe.

Exemple:

MOV AX, 96

CWD

MOV AX, -96

CWD

AX

0 0 0 0

? ? ? ?

0 0 6 0

0 0 6 0

DX

AX

F F F F

? ? ? ?

F F A 0

F F A 0

DX

56

INSTRUCTIONS LOGIQUES

NÉGATION

NOT OP transforme la valeur de l’opérande (registre ou

mot mémoire) en son complément à 1 [OPCA1(OP)].

Exemple:

MOV AX, 96

NOT AX

AX

0 0 6 0

F F 9 F

57

INSTRUCTIONS LOGIQUES

ET LOGIQUE

AND Od, Os effectue un ET logique entre Od et Os.

[Od Od Os]

AND R1 , R2 R1 R1 R2

AND R , [adr] R1 R [adr]

AND [adr] , R [adr] [adr] R

AND R , im R R im

AND taille [adr] , im [adr] [adr] im

AND [adr], [adr]

58

INSTRUCTIONS LOGIQUES

ET LOGIQUE

Exemple:

MOV AX , 503h

AND AX , 0201h

0 0 0 0 0 1 0 1 0 0 0 0 0 0 1 1

0 0 0 0 0 0 1 0 0 0 0 0 0 0 0 1

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1

AX

0201h

AX

59

INSTRUCTIONS LOGIQUES

ET LOGIQUE

TEST Od, Os: similaire à AND mais ne retourne pas

de résultat dans Od, seuls les indicateurs sont

positionnés.

Exemple:

MOV AX , 503h

TEST AX , 0201h

0 0 0 0 0 1 0 1 0 0 0 0 0 0 1 1

0 0 0 0 0 0 1 0 0 0 0 0 0 0 0 1

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1

AX

0201h

RT

S = 0, Z = 0

60

INSTRUCTIONS LOGIQUES

OU LOGIQUE

OR Od, Os effectue un OU logique entre Od et Os.

[Od Od Os]

OR R1 , R2 R1 R1 R2

OR R , [adr] R1 R [adr]

OR [adr] , R [adr] [adr] R

OR R , im R R im

OR taille [adr] , im [adr] [adr] im

OR [adr], [adr]

61

INSTRUCTIONS LOGIQUES

OU LOGIQUE

Exemple:

MOV AX , 503h

OR AX , 0201h

0 0 0 0 0 1 0 1 0 0 0 0 0 0 1 1

0 0 0 0 0 0 1 0 0 0 0 0 0 0 0 1

0 0 0 0 0 1 1 1 0 0 0 0 0 0 1 1

AX

0201h

AX

62

INSTRUCTIONS LOGIQUES

OU EXCLUSIF

XOR Od, Os effectue un OU exclusif (XOR) entre Od et

Os [Od Od Os].

XOR R1 , R2 R1 R1 R2

XOR R , [adr] R1 R [adr]

XOR [adr] , R [adr] [adr] R

XOR R , im R R im

XOR taille [adr] , im [adr] [adr] im

XOR [adr], [adr]

63

INSTRUCTIONS LOGIQUES

OU EXCLUSIF

Exemple:

MOV AX , 503h

OR AX , 0201h

Exercice 1 (Premier programme): Écrire un programme

qui fait AX BX sans utiliser l’instruction XOR

0 0 0 0 0 1 0 1 0 0 0 0 0 0 1 1

0 0 0 0 0 0 1 0 0 0 0 0 0 0 0 1

0 0 0 0 0 1 1 1 0 0 0 0 0 0 1 0

AX

0201h

AX

64

INSTRUCTIONS DE DÉCALAGE

SHL Od, n Décalage Logique Gauche (Shift Logical Left)

SAL Od, n Décalage Arithmétique Gauche (Shift Arithmetic Left)

SHR Od, n Décalage Logique Droit (Shift Logical Right)

SAR Od, n Décalage Arithmétique Droit (Shift Arithmetic Right)

ROL Od, n Décalage Circulaire Gauche (Rotate Left)

ROR Od, n Décalage Circulaire Droit (Rotate Right)

RCL Od, n Décalage Circulaire Gauche à travers la retenue

(Rotate Left through Carry)

RCR Od, n Décalage Circulaire Droit à travers la retenue (Rotate

Right through Carry)

Od = registre ou adresse mémoire

™ n = 1 ou CL

65

INSTRUCTIONS DE DÉCALAGE DÉCALAGE LINÉAIRE GAUCHE/DROIT

SHL Od, n et SAL Od, n ont le même comportement.

SHR Od, n

. . . . . . MSB LSB

. . . . . .

C C

0 0 0 0

n zéros n zéros

. . . . . . MSB LSB

. . . . . .

C C 0 0 0 0

n zéros n zéros

66

INSTRUCTIONS DE DÉCALAGE DÉCALAGE LINÉAIRE DROIT

SHR Od, n

SHR ne tient pas compte du bit de signe SHR

travaille avec les nombres non signés.

SAR Od, n

SAR préserve le bit de signe SAR est réservée aux

nombres signés.

. . . . . . MSB LSB

. . . . . .

C C 0 0 0 0

n zéros n zéros

. . . . . . LSB

C C n fois n fois

67

INSTRUCTIONS DE DÉCALAGE DÉCALAGE CIRCULAIRE GAUCHE/DROIT

ROL Od, n

ROR Od, n

. . . . . .

C C

. . . . . .

C C

68

INSTRUCTIONS DE DÉCALAGE DÉCALAGE CIRCULAIRE À TRAVERS LA RETENUE

RCL Od, n

RCR Od, n

. . . . . . C C

. . . . . . C C

69

INSTRUCTIONS DE DÉCALAGE DÉCALAGE CIRCULAIRE À TRAVERS LA RETENUE

Exemple:

MOV AL, 11001011B

SHR AL, 1

MOV AL, 11001011B

ROR AL, 1

MOV AL, 11001011B

RCR AL, 1

1 1 0 0 1 0 1 1

0 1 1 0 0 1 0 1 1

x

C AL

1 1 0 0 1 0 1 1

1 1 1 0 0 1 0 1 1

x

C AL

1 1 0 0 1 0 1 1

x 1 1 0 0 1 0 1 1

x

C AL

70

INSTRUCTIONS DE BRANCHEMENT

Les instructions de branchement (ou saut) permettent de

modifier l’ordre d’exécution des instructions du

programme en fonction de certaines conditions.

L’instruction de branchement est une instruction à un

opérande « INST Label ». Un label (ou une étiquette) est

une représentation symbolique d’une instruction en

mémoire.

Le mode d’adressage des instructions de branchement est

immédiat.

71

INSTRUCTIONS DE BRANCHEMENT

On distingue 3 types d’instructions:

Branchement inconditionnel: JMP

Contrôle de Boucle : LOOPX

Branchement conditionnel: Jcondition

72

INSTRUCTIONS DE BRANCHEMENT INCONDITIONNEL

JMP label: effectue un saut (jump) vers le label spécifié.

.

.

.

Etiq: .

.

.

.

JMP Etiq

.

.

.

.

.

JMP suite

.

.

.

Suite: .....................

.

.

73

INSTRUCTIONS DE BRANCHEMENT DE CONTRÔLE DE BOUCLE

LOOP Label: fonctionne automatiquement avec le

registre CX (compteur). Quant le processeur rencontre

une instruction LOOP, il décrémente le registre CX. Si le

résultat n'est pas encore nul, il reboucle à la ligne portant

l'étiquette label, sinon il continue le programme à la ligne

suivante MOV CX, 10

ici: .....

.....

.....

LOOP ici

......

S’exécute 10 fois

74

INSTRUCTIONS DE BRANCHEMENT DE CONTRÔLE DE BOUCLE

Exemple: Que fait ce programme?

MOV DX, 0

MOV CX, 5

ETIQ: MOV BX, CX

MOV DL, [BX+1100]

LOOP ETIQ

Addition les 5 valeurs se trouvant à l’adresse 1101-1105 Addition les 5 valeurs se trouvant à l’adresse 1101-1105

75

INSTRUCTIONS DE BRANCHEMENT DE CONTRÔLE DE BOUCLE

Instruction Actions

1. Mise à jours de CX 2. Branchement si:

LOOP CXCX-1 CX 0

LOOPZ, LOOPE CXCX-1

(CX 0 ) et (Z=1)

LOOPNZ, LOOPNE CXCX-1

(CX 0 ) et (Z=0)

JCXZ Pas d’action CX = 0

76

INSTRUCTIONS DE BRANCHEMENT CONDITIONNEL

Un saut conditionnel n’est exécuté que si une certaine

condition est satisfaite, sinon l’exécution se poursuit

séquentiellement à l’instruction suivante.

La condition du saut porte sur l’état de l’un (ou plusieurs)

des indicateurs d’état (flags) du microprocesseur qui sont

positionnés en fonction du résultat de la dernière

opération.

77

Instruction Nom Condition

JZ Jump if Zero Saut si Z = 1

JNZ Jump if Not Zero Saut si Z = 0

JC Jump if Carry Saut si C = 1

JNC Jump if Not Carry Saut si C = 0

JS Jump if Sign Saut si S = 1

JNS Jump if Not Sign Saut si S = 0

JO Jump if Overflow Saut si O = 1

JNO Jump if Not Overflow Saut si O = 0

JP Jump if Parity Saut si P = 1

JNP Jump if Not Parity Saut si P = 0

78

INSTRUCTIONS DE BRANCHEMENT CONDITIONNEL

Branchements (sauts) arithmétiques: suivent en

général l’instruction de comparaison : CMP A,B

Condition Nombres signés Nombres non signés

A = B JE

A B JNE

A > B JG JA

A B JGE JAE

A < B JL JB

A B JLE JBE

PARTIE 3:

PROGRAMMATION EN ASSEMBLEUR

8086 79

80

PROGRAMMATION EN ASSEMBLEUR ÉTAPES DE LA RÉALISATION D’UN PROGRAMME

1. Définir le problème à résoudre : que faut-il faire

exactement ?

2. Déterminer des algorithmes: comment faire ? Par

quoi commencer, puis poursuivre ?

3. Rédiger le programme (code source) en utilisant le

jeu d’instructions (mnémoniques) ;

4. Tester le programme en réel ;

5. Corriger les erreurs (bugs) éventuelles : déboguer le

programme puis refaire des tests jusqu’à obtention d’un

programme fonctionnant de manière satisfaisante.

81

PROGRAMMATION EN ASSEMBLEUR DÉFINITION D’UN ASSEMBLEUR

Assembleur : logiciel de traduction du code source écrit

en mnémoniques (jeu d’instructions) au langage machine

(codes binaires correspondant aux instructions).

82

1. Saisir le code source avec

un éditeur de texte.

2. Compiler le code source

pour obtenir le code objet.

3. Éditer les liens pour avoir

un programme exécutable;

PROGRAMMATION EN ASSEMBLEUR ÉTAPES DE LA RÉALISATION PRATIQUE

83

Plusieurs logiciels

permettent le passage entre

ces trois phases présentée

comme:

MASM (Microsoft Assembl

er : avec LINK comme

éditeur de lien),

TASM (Turbo assembler :

avec TLINK comme éditeur

de lien) et

NASM, etc ...

PROGRAMMATION EN ASSEMBLEUR ÉTAPES DE LA RÉALISATION PRATIQUE

84

PROGRAMMATION EN ASSEMBLEUR POURQUOI?

Quelques fois, le code écrit en assembleur peut être plus rapide et

plus compact que le code généré par un compilateur.

L'assembleur permet l'accès à des fonctionnalités matérielles du

système directement qu'il pourrait être difficile ou impossible à

utiliser depuis un langage de plus haut niveau (C, C++, C #, Java,).

Acquérir une compréhension plus profonde de la façon dont

fonctionne un ordinateur (par exemple, comment les compilateurs et

les langage de haut niveau fonctionnent)

85

PROGRAMMATION EN ASSEMBLEUR FICHIER SOURCE

Comme tout programme, un programme écrit en assembleur

(programme source) comprend des définitions de données et des

instructions, qui s'écrivent chacune sur une ligne de texte.

86

PROGRAMMATION EN ASSEMBLEUR FICHIER SOURCE

PROGRAM Exemple

Data SEGMENT

; On met les directives de données pour réserver de la mémoire pour les

variables qui seront utilisées dans le programme.

Data ENDS

Code SEGMENT

ASSUME CS : Code, DS: Data

PROG

; mettre les instructions du programme

Code ENDS

END PROG

87

PROGRAMMATION EN ASSEMBLEUR FICHIER SOURCE

Les données sont déclarées par des directives, mots clefs

spéciaux que comprend l'assembleur (donc ils sont destinés à

l'assembleur.

Les directives qui déclarent des données sont regroupées dans les

segments de données, qui sont délimités par les directives

SEGMENT et ENDS.

Déclaration d’une constante: Nom EQU Expression

VAL EQU 50 ; assigner la valeur 50 au nom VAL

ET1 EQU VAL* 5 + 1 ; assigner une expression calculer à VAL

88

PROGRAMMATION EN ASSEMBLEUR FICHIER SOURCE

Déclaration des variables

DB (Define Byte): définit une variable de 8 bits, c-à-d elle

réserve un espace mémoire d'un octet. Donc, les valeurs de telle

variable sont comprises entre 0 et 255 (pour les nombres non

signés ) et de -128 jusqu'à 127 pour les nombres signés .

Nom DB Expression

X DB 8H ; Définir une variable nommée X sur un octet de valeur

initiale (8)16

Y DB ? ; Définir une variable nommée Y sur un octet de valeur

initiale quelconque (autrement dit, la variable n’est pas

n’intialisée)

89

PROGRAMMATION EN ASSEMBLEUR FICHIER SOURCE

Déclaration des variables

DW (Define Word): définit une variable de 16 bits, c-à-d elle

réserve un espace mémoire de deux octets. Donc, les valeurs de

telle variable sont comprises entre 0 et 65535 (pour les nombres

non signés) et de -32768 jusqu'à 32767 pour les nombres signés .

Nom DW Expression

X DW 458H ; Définir une variable nommée X sur deux octets de

valeur initiale (458)16

Y DW ? ; Définir une variable nommée Y sur 2 octets de valeur

initiale quelconque

90

PROGRAMMATION EN ASSEMBLEUR FICHIER SOURCE

Déclaration des tableaux

T1 DW 10,12,14,5,8 ; réserve un tableau de 5 cases, chaque

case est sur un octet tel que

T2 DW 10,1200,140 ; réserve un tableau de 3 cases, chaque

case est sur deux octets tel que

Mess DB 'ISET' ; réserve un tableau de 4 cases, chaque case est

sur un octet et contient le code ASCII du caractère tel que:

Directive DUP: utilisée pour déclarer un tableau de n cases,

toutes initialisées à la même valeur.

10 1200 140

10 12 14 5 8

‘I’ ‘S’ ‘E’ ‘T’

91

PROGRAMMATION EN ASSEMBLEUR FICHIER SOURCE

Déclaration des tableaux

Directive DUP: utilisée pour déclarer un tableau de n cases,

toutes initialisées à la même valeur.

T3 DB 100 DUP (15) ; tableau de 100 cases (octets) valant 15

T4 DW 10 DUP (?) ; 10 cases de 16 bits non initialisés

92

PROGRAMMATION EN ASSEMBLEUR FICHIER SOURCE

Les instructions sont placées dans le segment de code.

Code SEGMENT ; Sert à déclarer le début segment code. On aurait

aussi bien pu choisir un autre nom que Code

ASSUME CS : Code, DS: Data ; Permet d'indiquer à l'assembleur le

nom du segment de données et de code

PROG; La première instruction du programme doit toujours être repérée

par une étiquette (dans notre cas : PROG).

; mettre les instructions du programme

Code ENDS ; Sert à déclarer la fin du segment code.

END PROG ; Permet d'indiquer à l'éditeur de liens quelle est la première

instruction qui a été exécutée lorsque l'on lance le programme

93

PROGRAMMATION EN ASSEMBLEUR FICHIER SOURCE

La syntaxe des instruction est comme suit :

{Label :} Mnémonique {opérandes} { ; commentaire}

Champs Description

Label

(étiquette)

champ optionnel destiné pour marquer une ligne

qui sera la cible d'une instruction de saut ou de

branchement. Il doit se terminer par « : » et ne

peut commencer par un chiffre.

Mnémonique champ obligatoire présente le nom de l’instruction

Opérande champ optionnel selon l'instruction (parfois

l'instruction nécessite deux opérandes, un

opérande et parfois non).

Commentaire champ optionnel sans signification syntaxique et

sémantique mais très intéressant pour la

programmation

94

PROGRAMMATION EN ASSEMBLEUR EXERCICE 1

N1 et N2 sont deux variables de 2 octets chacune

Début

N1 + N2

Résultat > 0

Ranger le résultat

dans le mot mémoire

d’adresse 200h

Ranger le résultat

dans le mot mémoire

d’adresse 100h

Fin

Oui Non

95

PROGRAMMATION EN ASSEMBLEUR EXERCICE 1 (1ÈRE SOLUTION)

PROGRAM Exemple1

Data1 SEGMENT

N1 DW ?

N2 DW ?

Data1 ENDS

Code1 SEGMENT

ASSUME CS : Code1, DS: Data1

Debut : MOV AX, N1 ; AX N1

ADD AX, N2 ;AX N1+ N2

CMP AX, 0

JG Cond1

MOV [200h], AX

JMP Fin

Cond1: MOV [100h], AX

Fin:

Code1 ENDS

END Debut

96

PROGRAMMATION EN ASSEMBLEUR EXERCICE 1 (2ÈME SOLUTION)

PROGRAM Exemple1

Data1 SEGMENT

N1 DW ?

N2 DW ?

Data1 ENDS

Code1 SEGMENT

ASSUME CS : Code1, DS: Data1

Debut : MOV AX, N1 ; AX N1

ADD AX, N2 ;AX N1+ N2

CMP AX, 0

JS Cond1

JE Cond2

MOV [100h], AX

JMP Fin

Cond2: MOV [200h], AX

Fin:

Code1 ENDS

END Debut

97

PROGRAMMATION EN ASSEMBLEUR EXEMPLE DE CODAGE DE TESTS

Langage évolué Assembleur

Jump si la condition est fausse

SI (condition vraie) ALORS

Actions_ALORS

FSI

Suite_programme

Calcul de la condition

JNCond FSI

Actions-ALORS

FSI:

Suite_Programme

98

PROGRAMMATION EN ASSEMBLEUR EXEMPLE DE CODAGE DE TESTS

Langage évolué Assembleur

1ère version

Jump si la condition est

fausse

2ème version

Jump si la condition est

vraie

SI (condition vraie)

ALORS

actions_ALORS

SINON

Actions_SINON

FSI

Suite_programme

Calcul de la condition

JNCond SINON

Actions-ALORS

JMP FSI

SINON:

Actions-SINON

FSI:

Suite_Programme

Calcul de la condition

JCond SI

Actions-SINON

JMP FSI

SI:

Actions-ALORS

FSI:

Suite_Programme

99

PROGRAMMATION EN ASSEMBLEUR EXEMPLE DE CODAGE DE TESTS

Langage évolué Assembleur

Jump si CX 0

Pour i 1 à n FAIRE

Actions-POUR

FP

Suite_programme

MOV CX, n

POUR:

Actions-POUR

LOOP POUR

Suite_Programme

100

PROGRAMMATION EN ASSEMBLEUR EXEMPLE DE CODAGE DE TESTS

Langage évolué Assembleur

Jump si la condition est fausse

TANT-QUE (condition)FAIRE

Actions-TQ

FTQ

Suite_programme

TQ: Calcul de la condition

JNCond FTQ

Actions-TQ

JUMP TQ

FTQ: Suite_Programme

101

PROGRAMMATION EN ASSEMBLEUR EXEMPLE DE CODAGE DE TESTS

Langage évolué Assembleur

Jump si la condition est fausse

REPETER

Actions-REPETER

JUSQUA (condition vraie)

Suite_programme

REPERTER:

Actions-REPETER

Calcul de la condition

JNCond REPETER

Suite_Programme

102

PROGRAMMATION EN ASSEMBLEUR EXERCICE 2

Écrire la suite d’instructions pour réaliser les étapes

suivantes :

1. Copier le contenu de la case mémoire [1230h] dans

CX

2. Comparer CX à 200

a. si < incrémenter CX et recommencer au point 2

b. si > décrémenter CX et recommencer au point 2

c. si = copier CX dans AX et continuer le programme

103

PROGRAMMATION EN ASSEMBLEUR ACCÈS AUX ÉLÉMENTS D’UN TABLEAU

L’adresse du premier octet du tableau est récupérée à

l’aide de la directive offset.

Exemple:

TAB DW 15, 17, 80

MOV BX, TAB; BX contient la valeur 15

MOV BX, offset TAB; BX contient l’adresse du

premier octet du TAB

Pour accéder à un élément d'un tableau, son adresse doit

être calculée.

104

PROGRAMMATION EN ASSEMBLEUR ACCÈS AUX ÉLÉMENTS D’UN TABLEAU

Exercice 3: Écrire un programme qui initialise un

tableau avec 32 éléments (0, 3, 9, 12, ......, 91) dans les

deux cas suivants

Cas 1: Les éléments sont sur un octet

Cas 2: Les éléments sont sur deux octets

105

PROGRAMMATION EN ASSEMBLEUR TRAITEMENT DES CHAÎNES DE DONNÉES

Un élément de la chaîne peut être soit un octet

(caractère) [B] ou un mot [W].

LODSB/W Chargement d’un élément de chaîne depuis la mémoire

dans un registre

STOSB/W Écriture d’un élément de chaîne en mémoire

MOVSB/W Transfert d’un élément entre deux chaînes

SCASB/W Comparaison entre une valeur et un élément de chaîne

CMPSB/W Comparaison entre deux éléments de chaîne

106

PROGRAMMATION EN ASSEMBLEUR TRAITEMENT DES CHAÎNES DE DONNÉES

Une chaîne peut atteindre 128K octets;

La chaîne Source est référencée par DS:SI;

La chaîne Destination est référencée par ES:DI;

L’indicateur D indique le sens de l’accès aux éléments de

la chaîne;

D=1 ⇒ Droite à Gauche (Fin au Début)

D=0 ⇒ Gauche à Droite (Début à la Fin ),

Le bit D est positionné par les instructions STD et CLD.

107

PROGRAMMATION EN ASSEMBLEUR TRAITEMENT DES CHAÎNES DE DONNÉES

D = 0 D = 1

LODSB MOV AL, [DS:SI]

INC SI

MOV AL, [DS:SI]

DEC SI

LODSW MOV AX, [DS:SI]

ADD SI, 2

MOV AX, [DS:SI]

SUB SI, 2

LODSB/W: Chargement d’un élément de chaîne depuis

la mémoire dans un registre

108

PROGRAMMATION EN ASSEMBLEUR TRAITEMENT DES CHAÎNES DE DONNÉES

D = 0 D = 1

STOSB MOV [ES:DI], AL

INC DI

MOV [ES:DI], AL

DEC DI

STOSW MOV [ES:DI], AX

ADD DI, 2

MOV [ES:DI], AX

SUB DI, 2

STOSB/W: Écriture d’un élément de chaîne en mémoire

109

PROGRAMMATION EN ASSEMBLEUR TRAITEMENT DES CHAÎNES DE DONNÉES

D = 0 D = 1

MOVSB MOV R, [DS:SI]

MOV [ES:DI], R

INC SI

INC DI

MOV R, [DS:SI]

MOV [ES:DI], R

DEC SI

DEC DI

MOVSW MOV R, [DS:SI]

MOV [ES:DI], R

ADD SI, 2

ADD DI, 2

MOV R, [DS:SI]

MOV [ES:DI], R

SUB SI, 2

SUB DI, 2

MOVSB/W: transfert un élément de la chaîne source (DS:SI)

vers une élément de la chaîne destination (ES:DI).

110

PROGRAMMATION EN ASSEMBLEUR TRAITEMENT DES CHAÎNES DE DONNÉES

D = 0 D = 1

SCASB CMP [ES: DI], AL

INC DI

CMP [ES: DI], AL

DEC DI

SCASW CMP [ES: DI], AX

ADD DI, 2

CMP [ES: DI], AX

SUB DI, 2

SCASB/W: Comparaison entre une valeur et un élément

de chaîne

111

PROGRAMMATION EN ASSEMBLEUR TRAITEMENT DES CHAÎNES DE DONNÉES

D = 0 D = 1

CMPSB MOV R, [DS:SI]

CMP [ES:DI], R

INC SI

INC DI

MOV R, [DS:SI]

CMP [ES:DI], R

DEC SI

DEC DI

CMPSW MOV R, [DS:SI]

CMP [ES:DI], R

ADD SI, 2

ADD DI, 2

MOV R, [DS:SI]

CMP [ES:DI], R

SUB SI, 2

SUB DI, 2

CMPSB/W: compare un élément de la chaîne source (DS:SI)

avec une élément de la chaîne destination (ES:DI).

112

PROGRAMMATION EN ASSEMBLEUR TRAITEMENT DES CHAÎNES DE DONNÉES

Les indicateurs de FLAGS ne sont pas modifiés par les

opérations (incrémentation et décrémentation) modifiant

la valeur des index (SI, DI) qui se font automatiquement

dans les instructions de traitement de chaines de

caractères. Donc, on ne peut pas utiliser les instructions

de branchement après ces instructions pour détecter la

fin des chaînes.

D = 1

STOSB

JE

MOV [ES:DI], AL

DEC DI

JE

113

PROGRAMMATION EN ASSEMBLEUR TRAITEMENT DES CHAÎNES DE DONNÉES

REP, REPE, REPNE permettent de répéter une

instruction de traitement de chaînes de données. Le

registre CX indique le nombre d’itérations à effectuer.

REP ne peut préfixer que les instructions LODS, STOS,

MOVS.

REPE et REPNE ne peuvent préfixer que les

instructions CMPS et SCAS.

114

PROGRAMMATION EN ASSEMBLEUR TRAITEMENT DES CHAÎNES DE DONNÉES

REP LODSB, REP LODSW, REP STOSB, REP

STOSW, REP MOVSB, REP MOVSW: à chaque

itération, les actions suivantes sont exécutées :

1. Tester le compteur (CX). S’il est à zéro, aller à 2, sinon:

a. Exécuter l’opération sur la chaîne (LODS, STOS ou MOVS)

b. Décrémenter le compteur CX

2. Continuer l’exécution du programme

115

PROGRAMMATION EN ASSEMBLEUR TRAITEMENT DES CHAÎNES DE DONNÉES

REPE SCAS compare au plus CX éléments de la chaîne

pointée par ES:DI avec la valeur du registre AL ou AX

selon le cas. Les itérations sont poursuivies tant que les

éléments de la chaîne sont égaux à la valeur du

registre et tant que le compteur n’est pas nul. Dès

que l’une de ces conditions n’est plus vérifiée,

l’instruction REPE SCAS est terminée

116

PROGRAMMATION EN ASSEMBLEUR TRAITEMENT DES CHAÎNES DE DONNÉES

REPE CMPS compare au plus CX éléments de la chaîne

pointée par ES:DI avec ceux de la chaîne pointée par DS:

SI. Les itérations sont poursuivies tant que les

éléments des deux chaînes sont égaux et tant que le

compteur n’est pas nul. Dès que l’une de ces

conditions n’est plus vérifiée, l’instruction REPE CMPS

est terminée

117

PROGRAMMATION EN ASSEMBLEUR TRAITEMENT DES CHAÎNES DE DONNÉES

REPNE SCAS compare au plus CX éléments de la

chaîne pointée par ES:DI avec la valeur du registre AL

ou AX selon le cas. Les itérations sont poursuivies tant

que les éléments de la chaîne sont différents à la

valeur du registre et tant que le compteur n’est pas

nul. Dès que l’une de ces conditions n’est plus vérifiée,

l’instruction REPE SCAS est terminée

118

PROGRAMMATION EN ASSEMBLEUR TRAITEMENT DES CHAÎNES DE DONNÉES

REPNE CMPS compare au plus CX éléments de la

chaîne pointée par ES:DI avec ceux de la chaîne pointée

par DS: SI. Les itérations sont poursuivies tant que les

éléments des deux chaînes sont différents et tant

que le compteur n’est pas nul. Dès que l’une de ces

conditions n’est plus vérifiée, l’instruction REPE CMPS

est terminée

119

PROGRAMMATION EN ASSEMBLEUR TRAITEMENT DES CHAÎNES DE DONNÉES

Exemple: Copie d’un tableau de caractères dans un autre.

Data Segment

CH DB ‘hello word’ ; chaîne source

RES DB 11 DUP(?) ;chaîne destinataire

Date Ends

Code Segment

Assume CS: Code, DS: Date

Debut: LEA DI, RES ; MOV DI, offset RES

LEA SI, CH ; MOV SI, offset CH

MOV CX, 11 ; longueur de la chaîne

REP MOVSB ; copie

Code Ends

End Debut

120

PROGRAMMATION EN ASSEMBLEUR TRAITEMENT DES CHAÎNES DE DONNÉES

Exemple: Recherche d’un caractère dans une chaîne de

caractères

Data Segment

CH DB ‘hello word’

Date Ends

Code Segment

Assume CS: Code, DS: Date

Debut: MOV AL, ’w’

LEA DI, CH

MOV CX, 11

REPNE SCASB

Code Ends

End Debut

121

PROGRAMMATION EN ASSEMBLEUR ENTRÉES / SORTIES

Pour faire des entrées/sorties (essentiellement avec

l’écran et le clavier), on passe par des interruptions (des

sous-programmes préexistants dans la machine) du

BIOS, la plus importante est l’interruption 21h.

L’appel se fait via l’instruction INT 21h.

Le registre AH contient le numéro de la fonction qu’on

veut utiliser.

122

PROGRAMMATION EN ASSEMBLEUR ENTRÉES / SORTIES

Instructions Fonctionnalité

MOV AH, 4CH

INT 21

Quitter le système d'exploitation.

MOV AH, 01H

INT 21

Lire un caractère au clavier et le renvoyer (son

code ASCII) dans le registre AL.

MOV AH, 02H

INT 21

Afficher le caractère qui se trouve dans le registre

DL à l’écran.

Exemple: afficher le caractère b à l’écran.

MOV DL, ’b’

MOV AH, 2

INT 21h

123

PROGRAMMATION EN ASSEMBLEUR ENTRÉES / SORTIES

Instructions Fonctionnalité

MOV AH,

0AH

INT 21

Lire une chaîne de caractère à partir du clavier

L'adresse du premier caractère de la chaîne est DS:DX,

Il faut préciser dans le premier octet de la chaîne, la

longueur maximale à ne pas dépasser.

Le deuxième octet indique le nombre de caractère

effectivement saisi.

La chaîne se termine par retour chariot.

La longueur de la chaîne doit être supérieure ou égale à 3.

Long max Long lue X X .... X X CR

Chaîne Lue

124

PROGRAMMATION EN ASSEMBLEUR ACCÈS AUX ÉLÉMENTS D’UN TABLEAU

Exemple: Copier une chaîne lue dans une autre

Ch1 DB 15 DUP(13)

Ch2 DB 15 DUP(13)

.....

MOV AH, 0AH

LEA DX, Ch1

INT 21h

MOV CH, 0

MOV CL, [Ch1 + 1]

LEA SI, Ch1+2

LEA DI, Ch2+2

REP MOVSB

125

PROGRAMMATION EN ASSEMBLEUR ENTRÉES / SORTIES

Instructions Fonctionnalité

MOV AH, 09H

INT 21

Afficher une chaîne de caractère à l’écran:

L'adresse du premier caractère de la chaîne est

DS:DX,

Le dernier caractère de la chaîne doit être le caractère

$.

msg DB ’hello world’, ’$’

.....

MOV AH, 9

LEA DX, msg

INT 21h

PARTIE 4:

CODE MACHINE DES

INSTRUCTIONS 8086

126

127

CODE MACHINE DES INSTRUCTIONS

Les instructions 8086 sont présentées dans la machine

sous forme d’une suite de bits.

Elles comportent de 1 à 6 octets:

Le premier octet est obligatoire

Les autres octets sont facultatifs (ils dépendent du

code de l’opération)

De manière générale, le code machine d’une instruction

comportent le code de l’opération (COP), le code du

registre utilisé (REG), le code du mode d’adressage

utilisé (MOD), l’adresse de la case mémoire (R/M), etc.

128

CODE MACHINE DES INSTRUCTIONS

Bits 7 6 5 4 3 2 1 0

1er octet COP D W Le code d’opération

2ème octet MOD REG R/M Le mode d’adressage

3ème octet [Optionnel] Les bits de poids faibles

ADR, DEP ou VAL

4ème octet [Optionnel] Les bits de poids forts de

ADR, DEP ou VAL

5ème octet [Optionnel] Les bits de poids faible de

VAL

6ème octet [Optionnel] Les bits de poids faible de

VAL

129

CODE MACHINE DES INSTRUCTIONS

1er octet: Le code d’opération

COP: présente le code proprement dit de l’instruction

D: désigne la destination du résultat

W: indique si l’opération est sur 8 bits ou sur 16 bits

7 6 5 4 3 2 1 0

COP D W

D

0 Résultat dans mémoire ou Opération entre deux registres

1 Résultat dans un registre

W = 0 W = 1

8 bits 16 bits

130

CODE MACHINE DES INSTRUCTIONS

2ème octet: Le mode d’adressage

MOD: indique le mode d’adressage

7 6 5 4 3 2 1 0

MOD REG R/M

MOD Mode d’adressage

00 Directe

Indirecte avec DEP = 0

01 Indirect déplacement court (sur 8 bits)

10 Indirect déplacement long (sur 16 bits)

11 Par registre ou Immédiat

131

CODE MACHINE DES INSTRUCTIONS

2ème octet: Le mode d’adressage

REG: désigne le registre constituant un opérande

7 6 5 4 3 2 1 0

MOD REG R/M

REG W = 0 W = 1

000 AL AX

001 CL CX

010 DL DX

011 BL BX

100 AH SP

101 CH BP

110 DH SI

111 BH DI

132

CODE MACHINE DES INSTRUCTIONS

2ème octet: Le mode d’adressage

R/M: précise l’adresse constituant l’instruction (direct

ou indirect) ou le code de registre destinataire (par

registre)

7 6 5 4 3 2 1 0

MOD REG R/M

R/M R/M

000 [BX+SI+DEP] 100 [SI+DEP]

001 [BX+DI+DEP] 101 [DI+DEP]

010 [BP+SI+DEP] 110 [BP+DEP]

Direct

011 [BP+DI+DEP] 111 [BX+DEP]

133

CODE MACHINE DES INSTRUCTIONS

Exemples:

MOV AL, BL

88 D8

MOV AX, BX

89 D8

COP D W MOD REG R/M

1000 10 ? ? ? ? ?

1000 10 0 0 11 011 000

COP D W MOD REG R/M

1000 10 0 1 11 011 000

134

CODE MACHINE DES INSTRUCTIONS

Exemples:

MOV DX, [123h]

8B 16 23 01

MOV [123h], DX

89 16 23 01

COP D W MOD REG R/M ADR

1000 10 ? ? ? ? ? ?

1000 10 1 1 00 010 110 2301

COP D W MOD REG R/M ADR

1000 10 0 1 00 010 110 2301

135

CODE MACHINE DES INSTRUCTIONS

Exemples:

MOV [SI], BL

88 1C

MOV [SI + 14h], BL

88 5C 14

COP D W MOD REG R/M

1000 10 ? ? ? ? ?

1000 10 0 0 00 011 100

COP D W MOD REG R/M ADR

1000 10 0 0 01 011 100 14

136

CODE MACHINE DES INSTRUCTIONS

Exemples:

MOV [SI + 14h], BL

88 5C 14

MOV [SI + 146h], BL

88 9C 46 01

COP D W MOD REG R/M ADR

1000 10 0 0 10 011 100 4601

COP D W MOD REG R/M ADR

1000 10 0 0 01 011 100 14

137

CODE MACHINE DES INSTRUCTIONS DE TRANSFERT

Mnémonique 1er octet

MOV

R/M, R/M

M, Val

R, Val

AX/AL, M_direct

M_direct, AX/AL

1000 10dw

1100 011w

1011 w REG

1010 000w

1010 001w

MOD REG R/M

MOD 000 M

Valeur

M_direct

M_direct

(Adr ou dep)

(Adr ou dep)

valeur

XCHG

R/M, R/M

R, AX

1000 011w

10010 REG

MOD REG R/M

(Adr ou dep)

LEA R, Var 10001101 MOD REG 110

Offset de

Var

138

CODE MACHINE DES INSTRUCTIONS ARITHMÉTIQUE

Mnémonique 1er octet

ADD

R/M, R/M

R/M, Val

AL/AX, Val

0000 00dw

1000 00sw

0000 010w

MOD REG R/M

MOD 000 R/M

Valeur

(Adr ou dep)

(Adr ou dep)

Valeur

SUB

R/M, R/M

M, Val

R, Val

AL/AX, Val

0010 10dw

1000 00sw

1000 00sw

0010 110w

MOD REG R/M

MOD 101 R/M

11 101 REG

Valeur

(Adr ou dep)

(Adr ou dep)

Valeur

Valeur

CMP

R/M, R/M

R/M, Val

AL/AX, Val

0011 10dw

1000 00sw

0011 110w

MOD REG R/M

MOD 111 R/M

Valeur

(Adr ou dep)

(Adr ou dep)

Valeur

s=1 dans le cas où une extension de signe 8 bits vers 16 bits

est effectuée sur la donnée valeur avant l’opération.

139

CODE MACHINE DES INSTRUCTIONS ARITHMÉTIQUE

Mnémonique 1er octet 2ème octet

INC

M

R 8 bits

R 16 bits

1111 111w

1111 1110

01000 REG

MOD 000 R/M

MOD 000 R/M

(Adr ou dep)

DEC

M

R 8 bits

R 16 bits

1111 111w

1111 1110

01001 REG

MOD 001 R/M

MOD 001 R/M

(Adr ou dep)

NEG R/M 1111 011w MOD 011 R/M (Adr ou dep)

MUL R/M 1111 011w MOD 100 R/M (Adr ou dep)

IMUL R/M 1111 011w MOD 101 R/M (Adr ou dep)

DIV R/M 1111 011w MOD 110 R/M (Adr ou dep)

IDIV R/M 1111 011w MOD 111 R/M (Adr ou dep)

140

CODE MACHINE DES INSTRUCTIONS LOGIQUE

Mnémonique 1er octet

NOT R/M 1111 011w MOD 010 R/M (Adr ou dep)

AND

R/M, R/M

R/M, Val

AL/AX, Val

0010 00dw

1000 000w

0010 010w

MOD REG R/M

MOD 100 R/M

Valeur

(Adr ou dep)

(Adr ou dep)

Valeur

OR

R/M, R/M

R/M, Val

AL/AX, Val

0000 10dw

1000 000w

0000 110w

MOD REG R/M

MOD 001 R/M

Valeur

(Adr ou dep)

(Adr ou dep)

Valeur

XOR

R/M, R/M

R/M, Val

AL/AX, Val

0011 00dw

1000 000w

0011 010w

MOD REG R/M

MOD 110 R/M

Valeur

(Adr ou dep)

(Adr ou dep)

Valeur

TEST

R/M, R/M

R/M, Val

AL/AX, Val

1000 010w

1111 011w

1010 100w

MOD REG R/M

MOD 000 R/M

Valeur

(Adr ou dep)

(Adr ou dep)

Valeur

141

CODE MACHINE DES INSTRUCTIONS DE DÉCALAGE

Mnémonique 1er octet 2ème octet

SAR

R/M,1

R/M,CL

1101 000w

1101 001w

MOD 111 R/M

MOD 111 R/M

(Adr ou dep)

(Adr ou dep)

SHL/SAL

R/M,1

R/M,CL

1101 000w

1101 001w

MOD 100 R/M

MOD 100 R/M

(Adr ou dep)

(Adr ou dep)

SHR

R/M,1

R/M,CL

1101 000w

1101 001w

MOD 101 R/M

MOD 101 R/M

(Adr ou dep)

(Adr ou dep)

142

CODE MACHINE DES INSTRUCTIONS DE DÉCALAGE

Mnémonique 1er octet 2ème octet

ROL

R/M,1

R/M,CL

1101 000w

1101 001w

MOD 000 R/M

MOD 000 R/M

(Adr ou dep)

(Adr ou dep)

ROR

R/M,1

R/M,CL

1101 000w

1101 001w

MOD 001 R/M

MOD 001 R/M

(Adr ou dep)

(Adr ou dep)

RCL

R/M,1

R/M,CL

1101 000w

1101 001w

MOD 010 R/M

MOD 010 R/M

(Adr ou dep)

(Adr ou dep)

RCR

R/M,1

R/M,CL

1101 000w

1101 001w

MOD 011 R/M

MOD 011 R/M

(Adr ou dep)

(Adr ou dep)

143

CODE MACHINE DES INSTRUCTIONS DE BRANCHEMENT

Mnémonique 1er octet 2ème octet

JMP

Etiq

Short Etiq

1110 1001

1110 1011

DepRel_16

DepRel_8

JS 0111 1000 DepRel_8

JNS 0111 1001 DepRel_8

JC 1110 0010 DepRel_8

JNC 0111 0011 DepRel_8

JE/JZ 0111 0100 DepRel_8

JNE/JNZ 0111 0101 DepRel_8

144

Mnémonique 1er octet 2ème octet

JA 0111 0111 DepRel_8

JAE 0111 0011 DepRel_8

JB 0111 0010 DepRel_8

JBE 0111 0110 DepRel_8

JG 0111 1111 DepRel_8

JGE 0111 1101 DepRel_8

JL 0111 1100 DepRel_8

JLE 0111 1110 DepRel_8

LOOP 1110 0010 DepRel_8

LOOPZ 1110 0001 DepRel_8

LOOPNZ 1110 0000 DepRel_8

JCXZ 1110 0011 DepRel_8

145

CODE MACHINE DES INSTRUCTIONS DE TRAITEMENT DES CHAÎNES

Mnémonique 1er octet

MOVS 1010 010w w = 0 pour MOVSB,

LODSB, STOSB,

SCASB, CMPSB

w = 1 pour MOVSW,

LODSW, STOSW,

SCASW, CMPSW

LODS 1010 110w

STOS 1010 101w

SCAS 1010 111w

CMPS 1010 011w

REP/REPZ/REPE 1111 0011

REPNZ/REPNE 1111 0010

146

AUTRES INSTRUCTIONS

Mnémonique 1er octet Action

CLC 1111 1000 C0

STC 1111 1001 C 1

CMC 1111 0101 C NOT C

CLD 1111 1100 D0 (Gauche à droite)

STD 1111 1101 D 1 (Droite à gauche)

Instructions d’action sur les indicateurs :

Instructions de Conversion

Instruction d’une interruption

Mnémonique 1er octet 2eme octet

INT Num 1100 1101 Numéro d’ interruption (21h)

Mnémonique 1er octet

CBW 1001 1000

CWD 1001 1001

SOURCES DE CE COURS

A. Oumnad, Microprocesseur de la famille 8086, pp.53, Disponible sur

http://arabteam2000-forum.com/index.php?app=core&module=attach§ion=attach&attach_id=133285

Djamal BENNOUAR, Cours Architecture des Ordinateurs 1, Département

Informatique, Faculté des Sciences, USDB, 2012.

Abdelhakim Khouas, Cours Architecture des Ordinateurs, Département de

Physique, Faculté des Sciences, Université de Boumerdes, 2008-2009. Disponible

sur http://infotroniquedz.ble.fr/architecture_des_pcs_107.htm

Microprocesseur 8086 Architecture et Programmation, Disponible sur

http://www.technologuepro.com/cours-genie-electrique/cours-2-microprocesseur-

8086-architecture-programmation/

Philippe Preux, Assembleur i8086, IUT Informatique du Littoral. Disponible sur

www.grappa.univ-lille3.fr/~ppreux/Documents/assembleur-i8086.pdf

147