00FH

-

Upload

soufianesani -

Category

Documents

-

view

8 -

download

2

description

Transcript of 00FH

ETUDE D’UN AMPLIFICATEUR DE TENSION A GAIN ASSERVI

On désire réaliser un amplificateur dont l’amplitude de la tension de sortie restesensiblement fixe lorsque l’amplitude de la tension d’entrée varie autour d’une valeur nominale.Cet amplificateur est donc équipé d’un régulateur de gain. Cette régulation est obtenue en faisantvarier automatiquement le taux de rétroaction négative à l’aide d’une résistance variableconstituée par un transistor J.F.E.T canal N.

+

A1

vs1

R1

S

D

G

VGS 2.5 V

e

ve1

Figure 1

L’amplificateur dont le schéma est donné en figure 1, utilise un amplificateur opérationnelA1 parfait utilisé en mode linéaire. Entre l’entrée - et la masse, on a disposé un transistor JFETcanal N utilisé dans sa zone ohmique, c’est-à-dire travaillant sous une tension VDS faible (vDS = ve1)où ses caractéristiques sont symétriques par rapport à l’origine. Dans la zone ohmique, larésistance RDS du JFET est donnée par la loi :

RR

kVDSDS

GS

=+

0

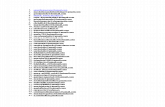

1Avec : RDS0 = 100 Ω et k = 1/3 V-1. Le graphe de la figure 2 indique l’évolution de la résistance RDS

du JFET en fonction de la tension VGS.

3 2. 75 2. 5 2. 25 2 1. 75 1. 5 1. 25 1 0. 75 0. 5 0. 25 00

300

600

900

1200

1500

RDS (Ω)

VGS (V)

Figure 2 : Evolution de la résistance RDS en fonction de VGS

2

I. ETUDE DE L’AMPLIFICATEUR

1.1) Sachant que la tension de repos VGS du JFET est fixée à - 2,5 V, calculer la valeur à donner à larésistance R1 pour obtenir un gain en tension du montage : A = vs1 / ve1 de 101.

1.2) Pour les petites variations autour du point de repos choisi, à savoir VGS = - 2,5 V, l’on peutécrire, en assimilant la courbe RDS = f (VGS ) à sa tangente : dRDS = - a dVGS.Déterminer l’expression du coefficient de proportionnalité a et donner sa valeur numérique sansoublier son unité.

1.3) En supposant maintenant que la tension continue VGS varie légèrement autour de sa valeurnominale, montrer qualitativement que le gain A du montage varie. Indiquer le sens de cesvariations.

II. ETUDE DE L’ELEMENT DE COMMANDE AUTOMATIQUE

e A2

vs2 (t)

D1

D2

R2

R3

i2 (t)

ve2 (t)0

T/2 T

t

ve2 (t)

Ve2m

Figure 3Le montage de commande (figure 3) utilise un autre amplificateur opérationnel idéal A2 attaqué parune tension sinusoïdale ve2 = Ve2m sin (ω.t), d’amplitude Ve2m . Les diodes D1 et D2 sont idéales.

2.1) Montrer qualitativement, en analysant l’état des diodes D1 et D2, pour :• 0 < t < T/2• T/2 < t < T,

que la tension de sortie vS2 (t) est obtenue par redressement mono-alternance de la tension d’entréeve2 (t). Dessiner sur une période la forme de la tension de sortie vS2 (t).

2.2) En déduire lorsque la diode D1 est passante, l’expression du rapport des amplitudes Vs2m / Ve2m

en fonction des résistances R2 et R3.

III ETUDE DE L’AMPLIFICATEUR A GAIN ASSERVI

Le schéma complet de l’amplificateur à gain asservi est donné en figure 4 où la tensionsinusoïdale d’entrée ve1 a une amplitude nominale (ou par défaut) Ve1m de 10 mV.On utilise ici, le montage de la figure 3 avec vs1 = ve2 et la sortie vs2 connectée sur la grille du JFETpar l’intermédiaire d’une capacité C. Cette capacité a une valeur suffisante (100 µF) pourconserver entre ses bornes, la valeur de crête de la tension Vs2 (t) analysée dans la 2° partie.

3

A1

R1

D

G

e

e A2

D1

D2

R2

R3

vs1

ve1 C

100 µF

S

VGS

Figure 4

3.1) Ecrire la relation liant la tension continue VGS et l’amplitude Ve1m de la tension d’entrée ve1 enfonction de RDS, R1, R2 et R3.On donne R2 = 100 kΩ, calculer la valeur à donner à la résistance R3 pour obtenir : VGS = - 2,5V.

3.2) On suppose maintenant que l’amplitude Ve1m de la tension d’entrée varie de dVe1m autour de savaleur nominale égale à 10 mV. Le système étant rétro actionné, la variation de l’amplitude de ve1

entraîne une variation de la tension VGS qui va modifier RDS.Comme le montre le résultat de la question 3.1, la tension VGS est fonction de deux variables Ve1m etRDS. En déduire l’expression de la variation dVGS de VGS (différentielle totale) en fonction desvariations dVe1m de Ve1m et dRDS de RDS..

3.3) En exploitant les propriétés du montage (questions 1.2, 3.1), rechercher l’expression du facteur

de régulation : SdV

dVs m

e m

= 1

1

en fonction de RDS, R1, a, R2, R3 et Ve1m .

Faire l’application numérique pour la valeur nominale Ve1m = 10mV.

CORRIGE

Q11 : VGS = -2,5 V RDS = 600 Ω Av

v

R

Rs

e DS

= = +1

1

11 R1 = 60 kΩ

Q12 : adR

dVDS

GS

= − avec : RR

k VDSDS

GS

=+

0

1 . a

k R

kVADS

GS

=+

= −.( )

02

1

11200

Q13 : Si VGS diminue -> RDS augmente -> A diminue Si VGS augmente -> RDS diminue -> A augmente

Q21 : lorsque 0 < t < T/2 la diode D1 est passante et D2 bloquée (i2 (t) > 0)Pour T/2 < t < T, la diode D2 est passante et D1 bloquée (i2 (t) < 0)

Vs2 (t) a la forme suivante qui correspond à un redressement mono alternance :vs2 (t)

0T/2 T

t

Q22 : D1 passante entraîne : V

V

R

Rs m

e m

2

2

3

2

= −

D1 est idéale c’est-à-dire analogue à un court-circuit.

Q31 : V VR

RVGS S m S m= = −2

3

21 avec : V

R

RVS m

DSe m1

111= +( )

VR

R

R

RVGS

DSe m= − +3

2

111( )

R3 = 247,5 kΩ

Q32 : Sachant que : VR

R

R

RVGS

DSe m= − +3

2

111( )

On calcule la différentielle totale :

dVV

VdV

V

RdRGS

GS

e mR e m

GS

dsVe m dsDScte cte

= +( ) ( )∂∂

∂∂1

1 1

soit : dVR

R

R

RdV V

R

R

R

RdRGS

DSe m e m

DSDS= − + +3

2

11 1

3

2

121( )

Q33 : Sachant que : dRDS = -a dVGS dVR

R

R

RdV V

R

R

R

Ra dVGS

DSe m e m

DSGS= − + −3

2

11 1

3

2

121( ) .

Or : VR

RVGS S m= − 3

21 ce qui entraîne : dV

R

RdVGS S m= − 3

21

Dans ces conditions : SdV

dV

R

RR

RV

R

Ra

S m

e m

DS

e mDS

= =+

+1

1

1

3

21

12

1

1

S = 16,97